10位高速分级比较型单斜模数转换器

2016-05-30张娜,金涛

张 娜,金 涛

(1.中国海洋大学信息科学与工程学院,山东青岛266100;2.中国石油大学(华东)机电工程学院,山东青岛266580)

10位高速分级比较型单斜模数转换器

张娜1,金涛2

(1.中国海洋大学信息科学与工程学院,山东青岛266100;2.中国石油大学(华东)机电工程学院,山东青岛266580)

摘要:本文设计了一种用于CMOS图像传感器的高速列并行分级比较型单斜模数转换器。利用两个斜坡发生器,采取两次分区间比较和减法运算相结合的方式,将信号分级转换。结合流水线操作模式,转换速度比传统单斜模数转换器提高12倍。该ADC在0.18 μm工艺下,实现了10位精度和263 ks/s的高转换速度。ADC的DNL=+0.83/-0.82 LSB,INL=+0.51/-1.5 LSB,SNR=58.28 dB,ENOB=9.3 bit。

关键词:单斜;列并行;模数转换器;减法器

0引言

单斜模数转换器[1]具有结构简单、面积小、功耗低等优点,特别适合用于大像素阵列CMOS图像传感器的列并行处理电路中。然而单斜ADC的转换时间与斜坡台阶数成正比,ADC位数每增加一位,转换时间成倍增长,难以满足10位及以上高精度图像传感器的高速应用需求[2]。

文献[3-4]提出的两步式单斜模数转换器采取3位、7位分别转换的方式,需要9个斜坡发生器,斜坡之间匹配较难实现,易产生转换误差,且大量的斜坡发生器和信号线会增加电源和面积消耗;以3位、7位的方式转换,转换速度较难得到大幅提升,随着第一级转换位数的增加,斜坡发生器数量指数上升,硬件上难以实现。

本文将设计一种10位分级比较型单斜ADC,对像素信号采取两次分区间比较和减法运算相结合的方式,并采用两级流水式操作模式,转换速度比传统单斜ADC提高12倍,且基本不增加列级电路复杂度,有利于高速列并行CMOS图像传感器的实现。

1整体结构和工作原理

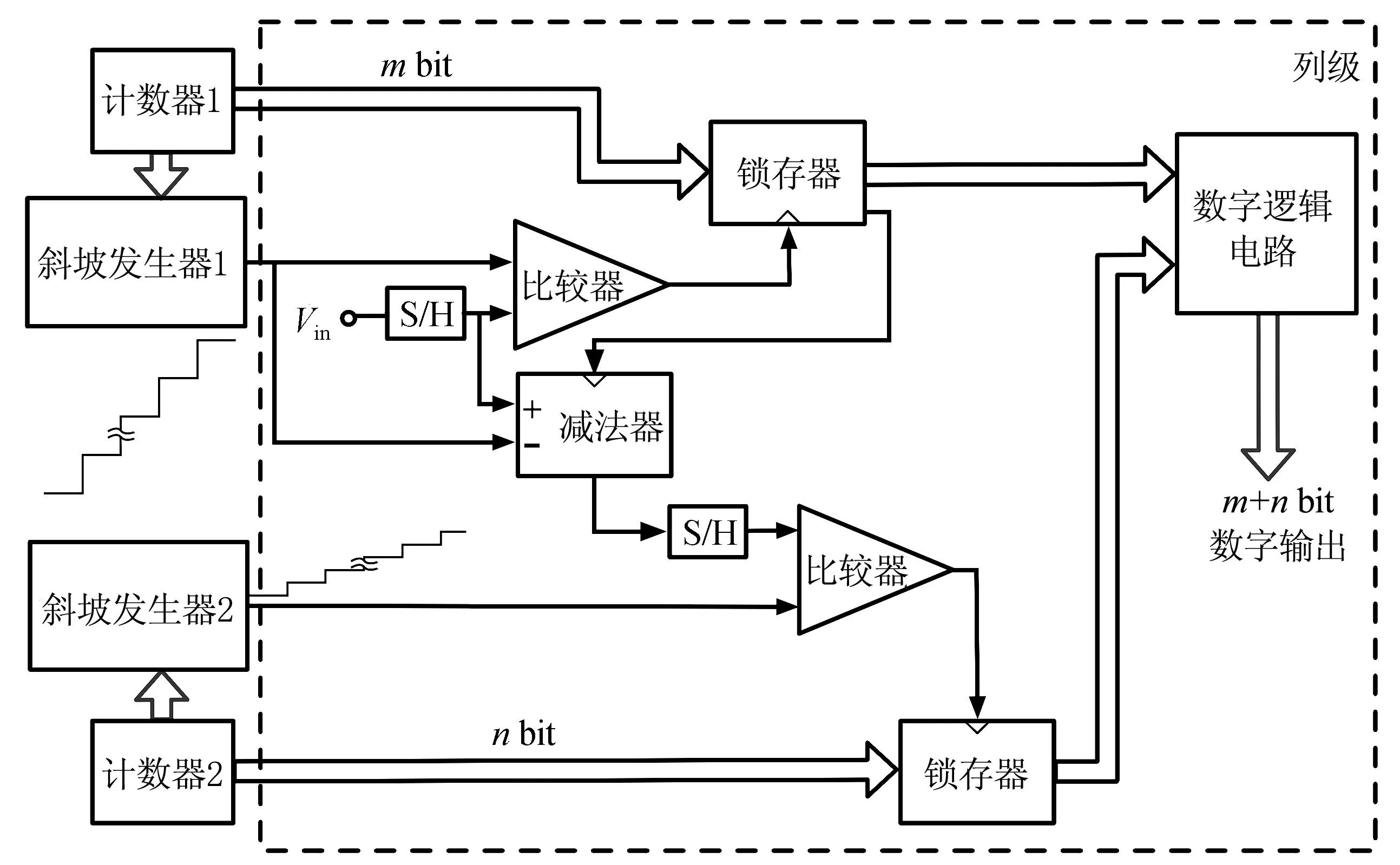

本文提出的分级比较型单斜ADC基本工作原理如下:对(m+n)位的模数转换器采用两次分区间比较,先采用2m个台阶的斜坡信号进行高m位的模数转换;再从原输入信号中减去高m位对应的斜坡信号得到转换差值;然后利用2n个台阶的斜坡信号转换剩下的低n位。两次转换的结果通过逻辑电路组合成m+n位二进制数据。

图1为分级比较型单斜模数转换器结构示意图。主要包括以下模块:斜坡发生器、计数器、锁存器、比较器、采样保持电路、减法器和数字逻辑电路。其中,斜坡发生器与计数器单元为所有列共用,其他模块电路,对应于640列像素每列一个。计数器控制斜坡发生器产生斜坡信号,计数器1为m位,计数器2为n位。斜坡信号1和光强信号为比较器的两个输入信号,当两者达到一致时比较器输出翻转。比较器输出翻转信号通过锁存器输出一个窄脉冲信号,用来控制寄存器存储此时计数器1中的m位数值,同时控制减法器对输入信号和此时的斜坡信号值做差值。随后差值送入第二级比较器,与斜坡信号2进行比较,从而得到低n位数值。最后通过数字逻辑电路得到m+n位数字信号。

普通单斜模数转换器完成m+n位转换约需要2m+n个时钟周期,对于10位ADC即为1 024个时钟周期。采用本文设计的分级比较型单斜模数转换器,完成m+n位转换约需要2m+2n个时钟周期,若取m=n,则对于10位ADC仅需要64个时钟周期,综合考虑差值计算和采样保持所耗费的时间,ADC转换速度可提高12倍以上。

图1 ADC结构图Fig.1 ADC structure diagram

2电路设计

2.1比较器

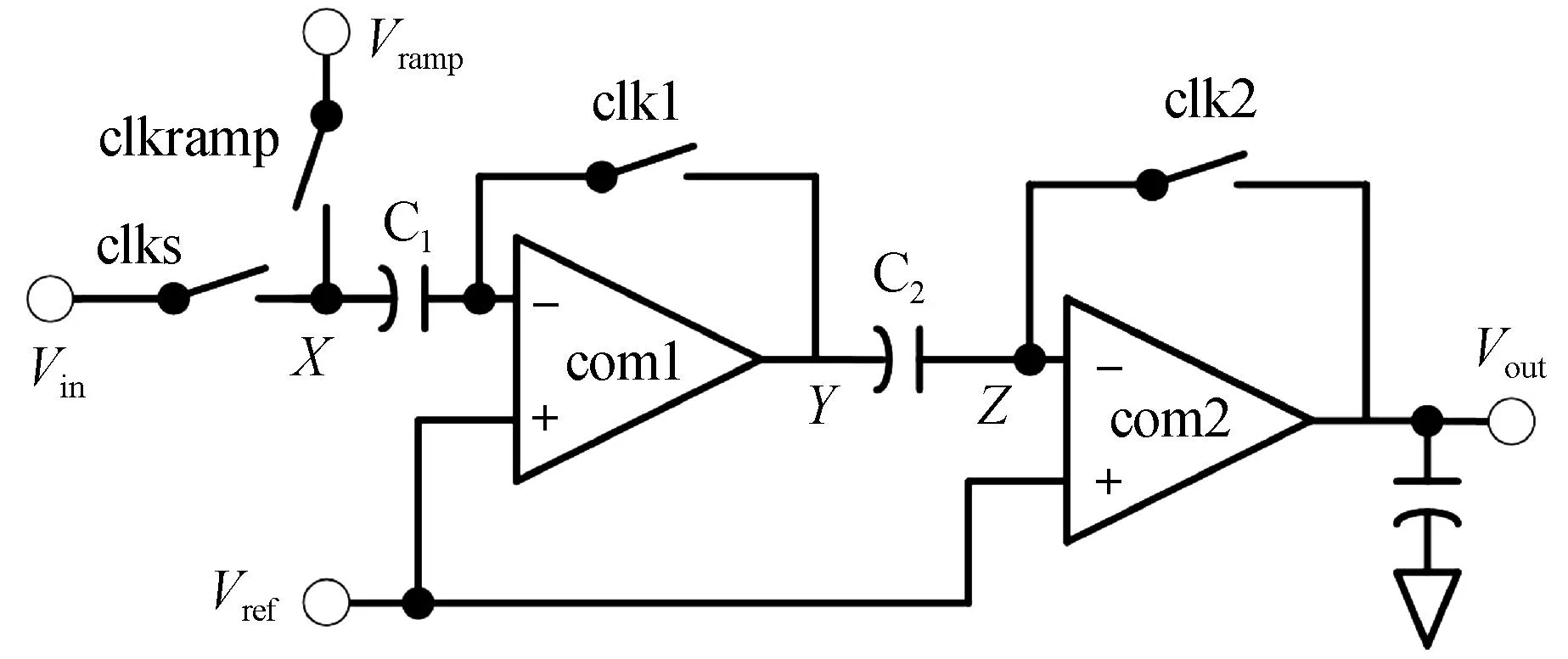

图2 比较器结构图Fig.2 Comparator structure

比较器将代表光强的像素信号与斜坡信号进行比较,当两者相等时输出翻转。

本文设计的CMOS图像传感器采用列并行结构,列处理电路宽度与像素单元宽度一致,即比较器水平方向的宽度由像素单元的宽度所限制,因此本文选用两级差分对运放的简单结构[5-6],如图2所示,既节省面积,又满足精度要求。

比较器工作原理如下:

a.采样阶段。

首先复位开关clk1、clk2闭合,然后开关clks闭合、clkramp关断,复位结束后复位开关clk1、clk2断开,复位阶段完成。采样电容C1上的电荷为:

Q1=(Vin-Vref)·C1,

(1)

采样电容C2上存储的电荷为0,C2上下极板电平相等。

b.比较阶段。

开关clks断开,开关clkramp闭合,采样电容C1上的电荷为:

(2)

采样电容C1、C2上电荷总量不变,由公式(1)、(2)可得:

VX=Vramp-Vin+Vref,

(3)

VY=VZ,

(4)

其中VX、VY、VZ分别为X、Y、Z点的电压值。

由公式(3)、(4)可以看出,比较器实现将斜坡电压Vramp与输入信号Vin相比较的功能。

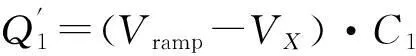

2.2减法器

第一级量化出m位数字信号后,需要计算输入信号和高m位数字信号对应的模拟值的差值送入下一级量化[7]。根据单斜模数转换器的工作原理可知,高m位数字信号对应的模拟值即为比较器翻转时刻的斜坡的台阶信号。

采用开关电容减法器来实现差值的计算,其结构如图3所示。

图3 减法器结构图Fig.3 Subtractor structure

Vcom是两级比较器的输出翻转信号,触发锁存器产生脉冲信号,控制开关clkc选通接入斜坡信号Vramp。由于整个电路的工作是建立在电荷守恒原理的基础之上,为保证电路正常工作,开关clka和clkb须采用两相不交叠时钟控制,clkc接通在clkb闭合的时间范围之内。可得到减法器输出电压与输入电压的关系如公式(5)所示:

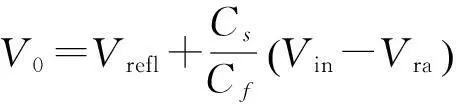

(5)

其中Vra为比较器翻转时刻的斜坡信号值。若取Cs=Cf,可在减法器的输出端计算出高位转换的差值,并利用斜坡最低参考值Vrefl将差值调整至第二级比较器工作范围内。

2.3数字误差校正

若比较器存在失调误差,使得在高m位转换时得出错误的二进制代码,在求差值时就会减掉错误的参考电压,从而得到错误的差值,差值可能超出低n位模数转换的斜坡范围,从而产生全1或全0的输出,导致第二级的转换错误[8]。

因此需采用数字误差校正技术来解决失调误差的问题。对于用来转换高位数据的斜坡发生器1,附加一位冗余位,即进行m+1位转换,一个台阶的高度为ΔV=(Vrefh-Vrefl)/2m+1。对于用来转换低位数据的斜坡发生器2,2n个台阶的总高度可设为2ΔV=(Vrefh-Vrefl)/2m。高位转换得出的m+1位和低位转换得到的n位,经过数字误差校正,最终可得到m+n位数字信号。这样可解决因失调误差差值溢出的问题,并可放宽对比较器的设计精度的要求,从而缩减列级芯片面积,实现高精度。

2.4流水线操作

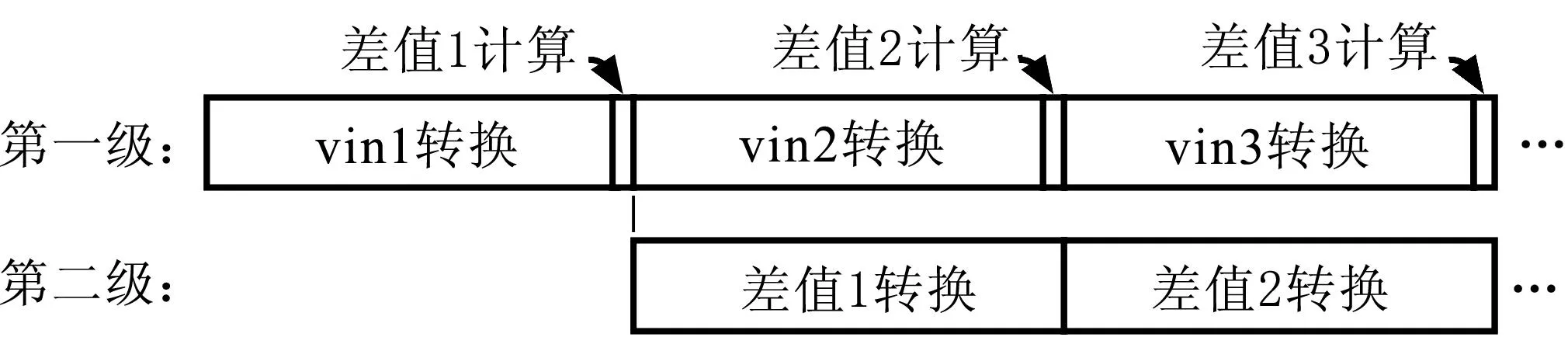

在两级比较器前端添加采样保持电路,对输入信号和差值信号进行采样保持,可将高m+1位转换与低n位转换流水进行。两级转换由两相不交叠时钟分别控制,避免相互干扰。具体时序如图4所示。

图4 流水线操作流程图Fig.4 Pipelined operation flow

利用分级比较型单斜ADC采用两级转换的电路特点,通过简单的添加两个采样保持电路,无需增加其他硬件和改变电路时序,可实现输入信号转换和差值转换并行的流水线操作模式。即第一级先采样输入信号,进行输入信号转换和差值计算,差值信号被第二级采样;然后第二级转换差值信号,同时第一级可转换下一行像素的信号值,因此高低位转换可并行进行,电路的工作速度得到提升。若采用数字误差校正技术,高位转换时间约为2m+1,低位转换时间约为2n。若在m+1和n基本相等的情况下,最快可使电路的转换速度提高一倍。

3设计结果

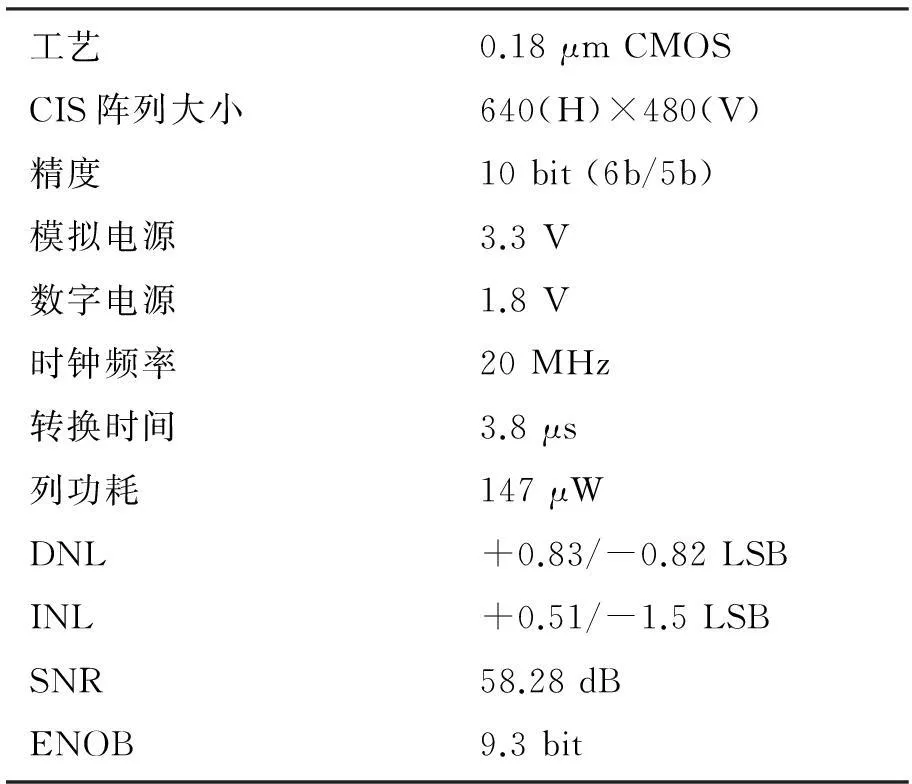

本设计采用Smic 0.18 μm CMOS工艺,其整体性能见表1。

表1 ADC的整体性能

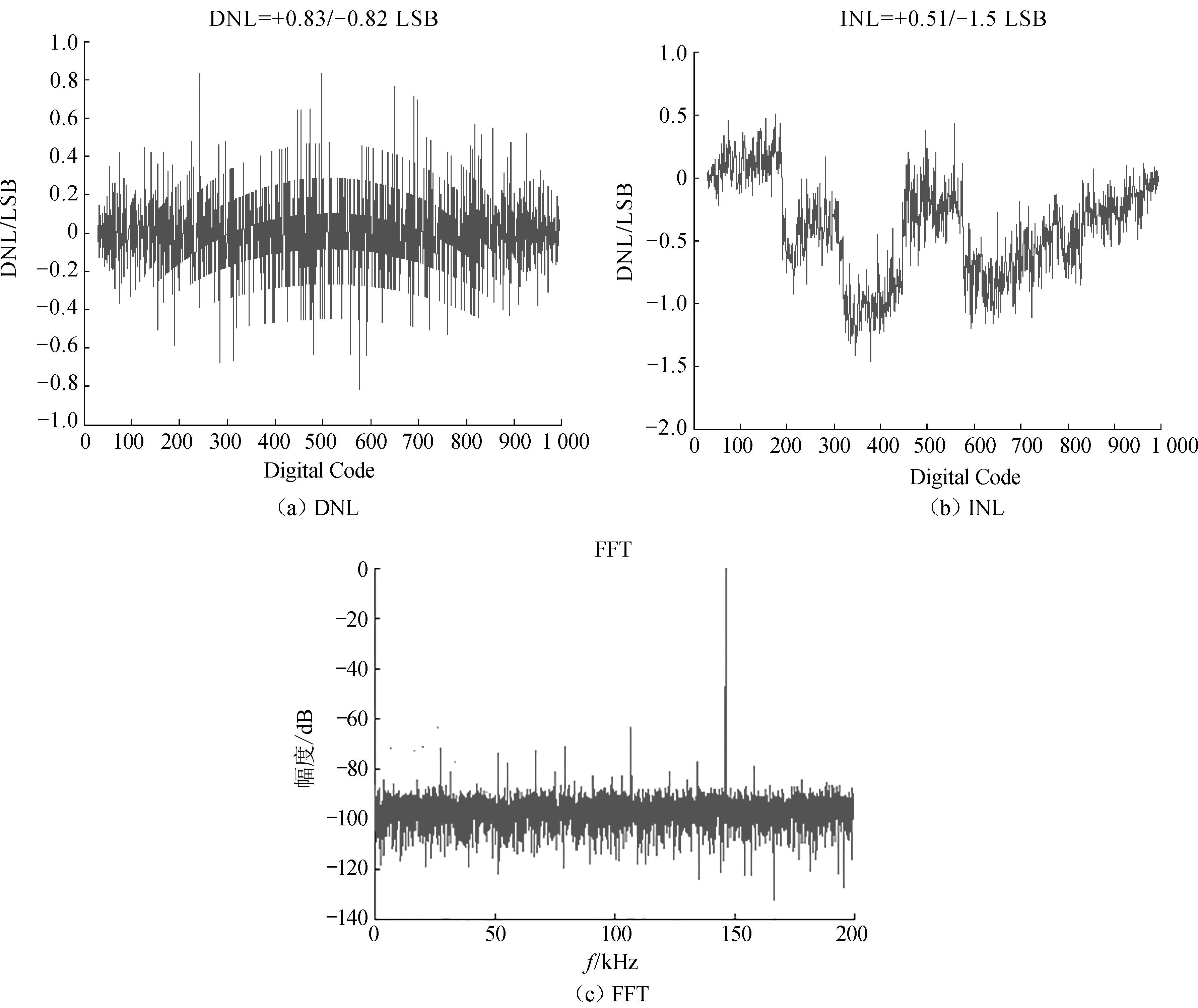

ADC的性能分析如图5所示,ADC的DNL=+0.83/-0.82 LSB,INL=+0.51/-1.5 LSB,SNR=58.28 dB,ENOB=9.3 bit。

图5 ADC性能分析Fig.5 ADC performance analysis

4结语

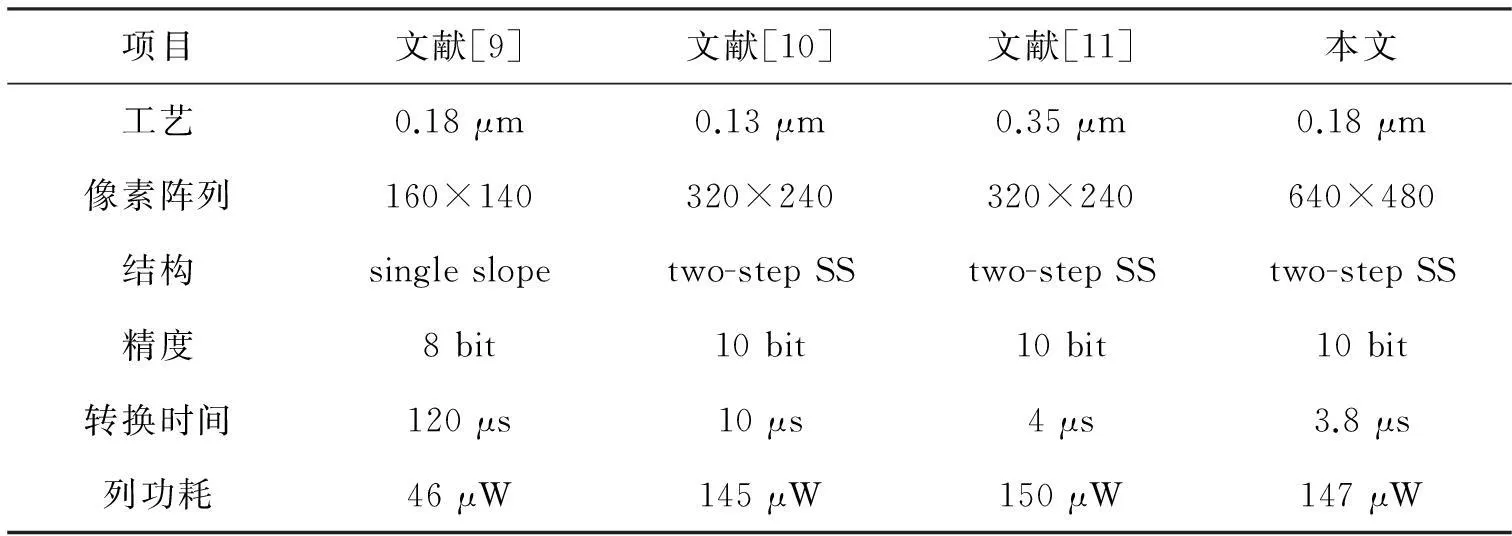

本文设计了一种用于CMOS图像传感器的高速列并行分级比较型单斜模数转换器。对像素信号采取两级分区间比较和减法运算相结合的方式,结合两级流水式操作模式,转换速度可比传统单斜模数转换器提高12倍以上。对设计的ADC进行仿真验证,并与几种传统的单斜ADC进行了比较,如表2所示。本文设计的ADC较传统单斜ADC速度性能得到提升,可满足高速列并行CMOS图像传感器应用需求。

表2 ADC性能比较

参考文献:

[1]CHO N,SONG B,KIM K,et al. A VGA CMOS image sensor with 11-bit columnparallel single-slope ADCs[C]//Proceedings of International Conference onSoCDesign(ISOCC). Incheon: IEEE,2010:25-27.

[2]张娜,姚素英,张钰. 用于CMOS图像传感器的列并行RSD循环ADC[J]. 光电子·激光,2008,19(9):1154-1157.

[3]SNOEIJ M F,DONEGAN P,THEUWISSEN A J P,et al. A CMOS image sensor with a column-level multiple-ramp single-slope ADC[C]//Digest of Technical Papers: IEEE International Solid-State Circuits Conference.San Francisco: IEEE,2007:506-618.

[4]SNOEIJ M F,THEUWISSEN A J P,MAKINWA K A A,et al. Multiple-ramp column-parallel ADC architectures for CMOS image sensors[J]. IEEE Journal of Solid-State Circuits,2008,42(12):2968-2977.

[5]张娜,姚素英,徐江涛. 用于CMOS图像传感器的列并行高精度ADC[J]. 固体电子学研究与进展,2006,26(3):349-353.

[6]凡东东,宋树祥,蒋品群,等. 新型高增益CMOS跨导运算放大器[J]. 广西师范大学学报(自然科学版),2014,32(4):6-10.

[7]LEE J, LIM S, HAN G. A 10b column-wise two-step single-slope ADC for highspeedCMOS image sensor[C]//Proc. IEEE Int. Image Sensor Workshop. Ogunquit: IEEE,2007:196-199.

[8]BAE J,KIM D,HAM S,et al. A two-step A/D conversion and column self-calibration technique for low noise CMOS image sensors[J]. Sensors,2014,14(7):11825-11843.

[9]YEH S F,HSIEH C C,CHENG C J,et al. A novel single slope ADC design for wide dynamic range CMOS image sensors[C]//2011 IEEE Sensors.Limerick: IEEE,2011:889-892.

[10]HWANG Y,SONG M. Design of a CMOS image sensor based on a 10-bit two-step single-slope ADC[J]. Journal of Semiconductor Technology and Science,2014,14(11):246-251.

[11]LIM S,LEE J,KIM D,et al. A high-speed CMOS image sensor with column-parallel two-step single-slope ADCs[J]. IEEE Transactions on Electron Devices,2009,56(3):393-398.

(责任编辑李小玲)

A 10bit High Speed Two-levels Single-slope ADC

ZHANG Na1,JIN Tao2

(1.College of Information Science and Engineering,Ocean University of China,Qingdao Shandong 266100,China;2.College of Mechanical &Electrical Engineering,China University of Petroleum,Qingdao Shandong 266580,China)

Abstract:A design of highspeedcolumn parallel two-levels single-slope ADC for CMOS image sensor is presented. The signal is converted by two sub division and subtraction operation using two ramp generators. With the pipelined operation mode,the conversion speed is 12 times higher than that of the conventional single slope ADC. The ADC achieves 10 bit accuracy and 263 ks/s high conversion rate with 0.18μm process. The DNL,INL,SNR,ENOB of the ADC are +0.83/-0.82 LSB,+0.51/-1.5 LSB,58.28 dB and 9.3 bit respectively.

Keywords:single-slope; column parallel; analog-to-digital converter; subtractor

中图分类号:TN402

文献标志码:A

文章编号:1001-6600(2016)01-0032-06

基金项目:国家自然科学基金资助项目(51405514);青岛市科技发展计划资助项目(13-1-4-249-jch);山东省自然科学基金资助项目(ZR2014FQ027);中央高校基本科研业务费专项资金资助(201513015)。

收稿日期:2015-05-15

doi:10.16088/j.issn.1001-6600.2016.01.005

通信联系人:张娜(1980—),女,山东青岛人,中国海洋大学讲师。E-mail:baiquanbaiquan@126.com