CMOS工艺多功能数字芯片的输出缓冲电路设计

2012-07-13周子昂张利红

周子昂,姚 遥,徐 坤,张利红

(周口师范学院 物理与电子工程系,河南 周口 466001)

近年来,CMOS集成电路产业高速发展,在各种消费类电子、家电和汽车产品中越来越多应用到CMOS芯片,但是在电子产品系统的设计过程中,随着CMOS工艺尺寸越来越小,单位面积上集成的晶体管越来越多,极大地降低了芯片的成本,提高了芯片的运算速度。但是,随着工艺的进步和尺寸的减小、芯片集成度的提高、多芯片模块的出现和数据宽度的增加,芯片外部接口上、模块内芯片间的接口和芯片内的总线与时钟树的大电容驱动问题问题变得日益严峻,同时,它还随着日益显著的互联线RLC效应而变得越来越复杂。这个问题引起了缓冲器插入技术和比例缓冲器的大量研究。

对于一个CMOS集成电路芯片来说,对于接到片外的最终输出级电路,需要驱动包括压点、封装管壳以及印刷电路板的寄生电容,这些电容的总和可能达到几十pF甚至上百pF。当一个电路的输出要驱动一个很大的负载电容时,为了保证电路的工作速度,必须使输出级能提供足够大的驱动电流。在一定工艺条件下,要增大驱动电流必须增大MOS管的宽长比,然而输出级MOS管的尺寸增大,又将使前一级电路的负载电容增大,使前一级的延迟时间加长。因此,在驱动很大的负载电容时(不仅针对连接片外的输出级,也包括扇出很大的电路,如时钟发生器电路等),需要一个设计合理的输出缓冲器,缓冲器要能提供所需要的驱动电流,同时又要使缓冲器的总延迟时间最小。在CMOS集成电路中,一般是用多级反相器构成的反相器链做输出缓冲器。这就是缓冲器插入技术和比例缓冲器的设计问题。

笔者首先介绍等比缓冲器的设计原理,最后基于CSMC 2P2M 0.6 μm CMOS工艺,针对各种缓冲器链的速度和面积优化情况,提出了一种优化的输出缓冲电路的设计,并应用在一款多功能数字芯片上参与MPW计划流片。仿真和流片测试表明,本设计的输出缓冲电路具有占用面积小、功耗低传输延迟小等优点。

1 等比缓冲器链的设计

1.1 设计原理和优化比例因子

比例缓冲器的两种基本类型是等比和变比缓冲器[1]。Lin在文献中第一次提出了等比缓冲器[2],其各级反相器与第一级的大小成式(1)中的比例关系。Jaeger在进一步的研究中得出了经典的等比因子[3],其他一些研究者进一步在最优等比因子中考虑了分开的栅漏电容负载和短路等效电容[4-6]。Vemurut讨论了变比缓冲器,其各级的比例关系如式(2)所示。

所谓等比缓冲器链,就是使反相器链逐级增大相同的比例,这样每级反相器有近似相同的延迟时间,对减小缓冲器的总延迟时间有利。模拟表明,当反相器输入波形的上升、下降时间与输出波形的上升下降时间基本相等时,反相器的充放电电流为一个三角形波形,电流的峰值就是MOS管的最大饱和电流。如果输入波形的上升、下降时间比输出波形的大,则电流峰值下降,也就是说这种情况下没有发挥出MOS管的最大驱动能力。如果输入波形的上升、下降时间比输出波形的小,则充放电电流波形从三角形变为梯形,这说明充放电时间加长[7]。

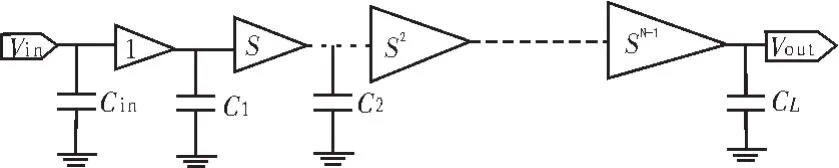

考虑一个逐级增大的S倍的反相器链,如图1所示。

图1 输出缓冲器链Fig.1 Output buffer chain

以第一级反相器尺寸为单位1,则第二级反相器中NMOS和PMOS的宽度都比第一级增大S倍,第三级比第一级增大S2倍,如此类推,第N级反相器比第一级增大SN-1倍。如果忽略连线寄生电容和各个节点的PN结电容,则图1的反相器链中有:

这里把CL看作依次增大尺寸的第N+1级反相器的输入电容,因此有:

如果一个反相器驱动一个和它相同的反相器的延迟时间为tp0,则上述反相器链中每级的延迟时间均为Stp0,则总的延迟时间tp为:

由式(3)可知:

把式(5)代入式(4)得:

如果知道了tp0和Cin以及最终要驱动的负载电容CL,则可以找到一个合适的N值,使输出缓冲器总的延迟时间tp最小。可以得到:

把式(7)代入式(5),可得到优化的比例因子:

这就是说,如果要使尺寸较小的电路(Cin很小)驱动一个很大的负载电容CL,必须通过一个缓冲器,理想情况下,缓冲器由N级逐级增大e倍的反相器链组成,这样可以使总延迟时间最小。

1.2 缺 点

上述设计规则仅仅是从速度优化方面考虑。在驱动很大的负载电容时,为了减小延迟时间,缓冲器中反相器的级数就越多,这将使总面积很大,而且也将增大缓冲器的功耗。在实际设计中应在满足设计速度的前提下,尽量减少反相器链的级数,适当增大比例因子S,这样可以使总面积和总功耗减少。

很多情况下往往对最终输出级的上升、下降时间有一定的要求。在这种情况下应根据给定的上升、下降时间要求和实际负载电容,设计出最终输出级反相器的尺寸,再综合考虑速度,面积和功耗等因素设计缓冲器的前几级电路[8]。

2 不同的输出缓冲器设计方案的比较

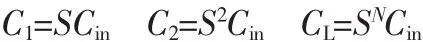

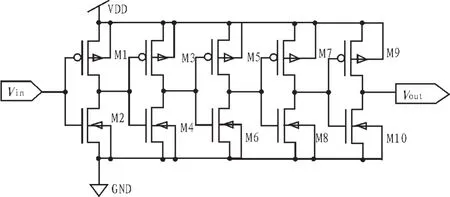

在一款多功能数字芯片的设计时考虑到芯片的驱动能力和所采用的0.6 μm的CMOS工艺,最终级反向器的尺寸为:PMOS 管为 W=540 μm,L=0.6 μm,NMOS 管为 W=216 μm,L=0.6 μm。第一级为芯片内部电路尺寸,PMOS管为W=20 μm,L=0.6 μm,NMOS 管为 W=8 μm,L=0.6 μm。 由以上分析可以知道,当输出反向器链采用不同的级数时,芯片的上升时间、下降时间和延迟时间是不同的,而且采用不同的级数时芯片所占用的面积也是不同的,下边我们通过三种不同的反相器链设计方式来对比,从中选出最合适的输出缓冲器链的设计方式。则输出缓冲器器链的设计为:

1)把输出缓冲器设计为第一种三级反相器链,如图2所示。

图2 三级输出缓冲器链Fig.2 Level three of output buffer chain

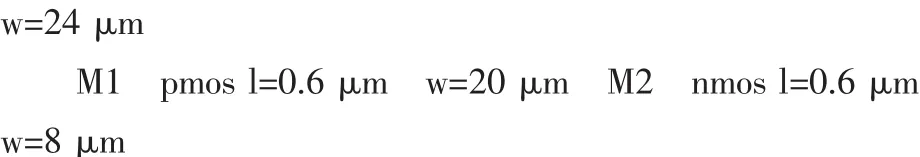

图2中各个PMOS管和NMOS管的尺寸分别为(取S=3):

通过HSPICE仿真软件,在0.6 μm CSMC 2P2M CMOS工艺库下的仿真结果(负载为100 pF电容,1 kΩ电阻)如图3(a)(b)(c)(d)所示。 主要考虑仿真结果中的输出反向器链的上升时间tr、下降时间tf、上升延迟和下降延迟td。

图3 三级反相器链仿真波形Fig.3 Level three of inverter chain simulation waveform

由图 3 (a)(b)(c)(d)可知,在输出缓冲器设计为三级反相器链的情况下,缓冲器的上升时间tr=17.6 ns,tf=16 ns,td=15.84 ns。

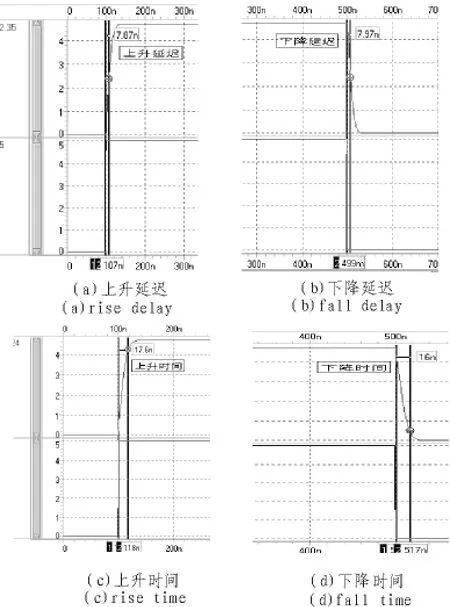

2)把输出缓冲器设计为五级反相器链,如图4所示。

图4 五级输出缓冲器链Fig.4 Level five of output buffer chain

图4中各个PMOS管和NMOS管的尺寸分别为(取S=2.72)。

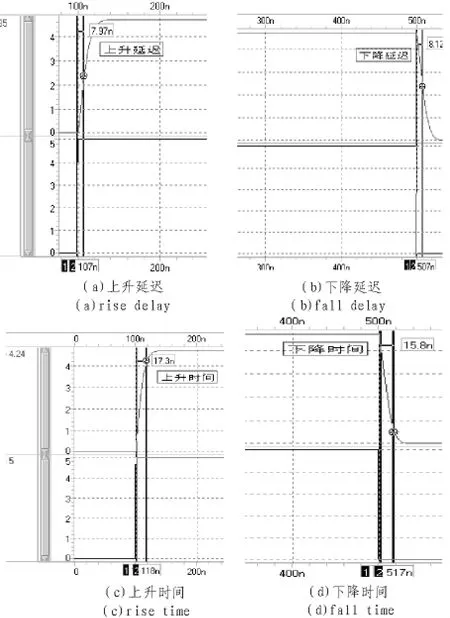

则同样通过HSPICE仿真软件,在0.6 μm CSMC 2P2M CMOS工艺库下的仿真结果为(负载为100 pF电容,1 kΩ电阻)。 如图 5(a)(b)(c)(d)所示,主要考虑仿真结果中的输出反向器链的上升时间tr、下降时间tf、上升延迟和下降延迟td。

图5 五级反相器链仿真波形Fig.5 Level five of inverter chain Simulation waveform

由图 5(a)(b)(c)(d)可知,在输出缓冲器设计为三级反相器链的情况下,缓冲器的上升时间tr=17.3ns,tf=15.8 ns,td=16.09 ns。

3 本设计输出缓冲器的设计

由以上两种设计方案的对比中可以看出,在负载为相同的情况下,两种设计方案在芯片的上升时间、下降时间和延迟时间上相差不大,考虑到芯片版图的面积和工艺问题,在多功能数字芯片的输出电路设计中采用了第一种三级反相器链的设计方案。 由以上的管子尺寸可知,输出反相器链的管子尺寸较大,所以一般采用梳状结构MOS晶体管的版图设计,也就是把一个晶体管分为多个叉指[9-10]。

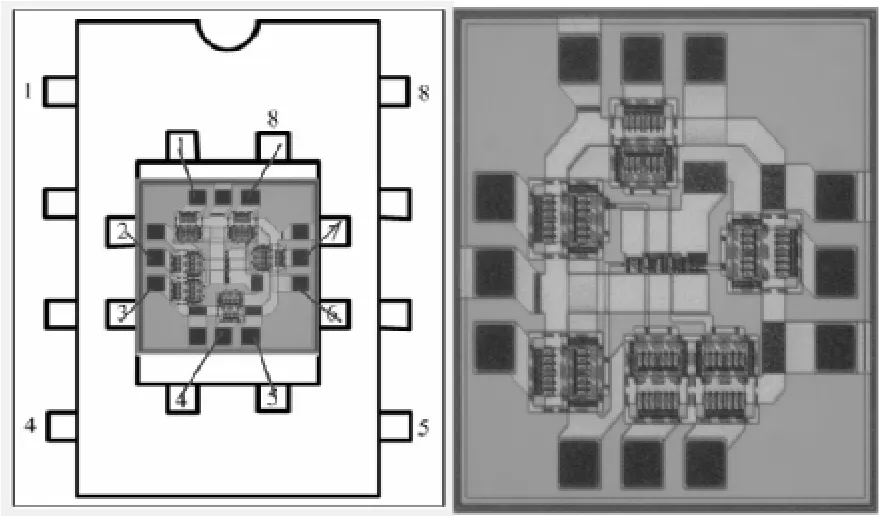

图6 多功能数字芯片版图和封装图Fig.6 Multi function digital IC design and package diagrams

图6所示为一款多功能数字芯片的版图照片和封装示意图,表1为管脚对应图。在多功能数字芯片的设计中,我们在输出端4和7端采用了本设计思想的等比输出缓冲器链电路,另外,由于在输出端设计了最终尺寸很大的CMOS管构成的输出缓冲器链电路来提高芯片的驱动能力,这些MOS管的漏区和衬底形成的pn结就相当于一个大面积的二极管,同样可以起到很好的ESD保护作用。因此,在输出端可不用增加ESD保护器件,从而减小芯片的版图面积。

表1 管脚对应表Tab.1 Pin map

4 结 论

文中系统介绍等比输出缓冲器电路的设计;深入分析了采用不同优化因子的输出缓冲器电路电路的设计优缺点。在此基础上,基于CSMC 2P2M 0.6 μm标准的COMS工艺,进行输出缓冲器链电路的版图设计和验证,并在一款多功能数字芯片上应用,该芯片参与了MPW计划进行流片。测试结果显示该输出缓冲器链电路的设计思想能直接应用到各种集成电路芯片中。

[1]易敬军,沈绪榜.双等比CMOS缓冲器的设计[J].微电子学与计算机,2003,20(1):62-66.

YI Jing-jun,SHEN Xu-bang.Design of dual fix tapered CMOS bufie[J].Microelectronics and Computer,2003,20(1):62-66.

[2]Linholm L W.An optimized output stage for MOS integrated circuits[J].1EEE Solid-State Circuits Society,1975,l0(2):106-109.

[3]Jaeger R C.Omments on an optimized output stage for MOS integrated circuits[J].1EEE J Solid-State Circuits,1975,10(3):185.

[4]Li N C,Haviland G L,Tuszynski A A.CMOS tapered bufer[J].IEEE Solid-State Circuits,1990,25(4):1005-1008.

[5]Prunty C,Ga1 L.Optimum tapered bufer[J].IEEE Solid-State Circuits,1992,27(1):118-119.

[6]Hedenstierna N,Jeppson K O.Comments on the optimum CMOS tapered bufer problem[J].IEEE Solid-State Circuits,1994,29(2):155-159.

[7]Lee C M,Soukup H.An algorithm for CMOS timing and area optimization[J].IEEE Solid-State Circuits,1984,SC-19(5):781-787.

[8]Harry V.Deep-submicron CMOS ICs,from basics to ASICs.Second Edition[M].Boston:Kluwer Academic Publishers,2000.

[9]Glasser L A,Dobberpuhl D W.The design and analysis of VLSI circuits[M].Reading:Addison-Wesley Publishing Company,1985.

[10]Annaratone M.Digital CMOS circuit design[M].Boston:Kluwer Academic Publishers,1986.