通信速率可调的单片机多机通信系统研究

2012-01-15郑毛祥

郑毛祥

(武汉铁路职业技术学院 湖北 武汉 430205)

在单片机的串行异步通信中,实现波特率设置的方法有很多种,但是有些方法要么需要额外的硬件支持,要么实现算法过于复杂,占用单片机的大量资源,而且研究通信波特率高的情况比较多,但对如何适应波特率较低的情况研究较少,这就大大降低单片机通信应用范围。文中研究并实现了一种简单实用的方法,不需要额外的硬件支持,对单片机的波特率有效设置的方法,并且软件开销也非常小。

MCS-51串行通信接口可以作通用异步接收和发送器(UART)使用,也可以作同步移位寄存器用。在异步通信中,传送的数据以帧的形式一帧一帧传送的,数据可以是一个字符代码或一个字节数据。一帧数据由4个部分组成:起始位、数据位、奇偶校验位和停止位。异步通信起始位用“0”表示数据传送的开始,然后从数据低位到高位逐位传送数据,接下来是奇偶校验位(可以省略不用),最后为停止位,用“1”表示一帧数据结束。起始位信号只占用一位,用来通知接收设备一个待接收的数据开始到达,线路上在不传送数据时,保持为1。接收端不断检测线路的状态。若在连续收到1以后,又收到一个0,就知道发来一个新数据,开始接收。数据位一般情况下是 8位(D0~D7)。 奇偶校验位(D8)只占用一位,在数据传送中也可以规定不用奇偶校验位,这一位可以省去,或者把它用作地址/数据帧标志,来确定这一帧中的数据所代表信息的性质,如规定D8=1表示该帧信息传送的是地址,D8=0表示传送的是数据。停止位用来表示一个传送字符的结束,它一定是高电平,停止位可以是1位、1.5位或2位,接收端接收到停止位后,就知道这一字符已传送完毕。两帧信息之间可以无间隔,也可以有间隔,且间隔时间可以任意改变,间隔用空闲位“1”来填充。

1 MCS-51的串行接口及控制寄存器

MCS-51单片机的串行口电路结构如图1所示[1]。

图1 MCS-51单片机串行口结构示意图Fig.1 MCS-51 MCUserial port structure diagram

8051通过引脚RXD(串行数据接收端)和引脚TXD(串行数据发送端)与外界进行通信。单片机内部的全双工串行接口部分,包含有串行发送缓冲器和接收缓冲器,两个物理上独立的缓冲器。发送缓冲器CPU只能写入发送的数据,但不能读出;接收缓冲器CPU只能读出接收的数据,但不能写入。因此,串行口可同时收、发数据,实现全双工传送。串行口发送和接收缓冲器的名称都是特殊功能寄存器SBUF(一个是接收SBUF,一个是发送SBUF),它们共用一个地址 99H。CPU若向外发送一个数据,只要执行一条写传送数据指令(如MOV SBUF,A)。若要接收一个外部传来的数据,只要执行一条读数据传送指令(如MOV A,SBUF)。

2 串行口通信控制

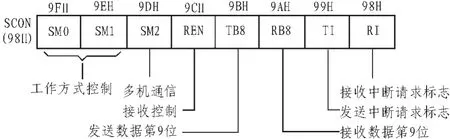

8051串行口是可编程接口,对它初始化编程主要是对串行口控制寄存器SCON(98H)的设置,包含串行口工作方式选择位、接收和发送控制位以及串行口状态标志位,其格式如图2所示。

图2 串行口控制寄存器SCONFig.2 Serial port control register SCON

SM0、SM1:串行口工作方式选择位,8051串行口可设置方式0、方式1、方式2、方式3共4种工作方式。

SM2:多机通信控制位,双机通信时,SM2=0,多机通信时,SM2=1。

REN:允许串行接收位。由软件置1允许接收数据,置0禁止接收数据。

TB8:是在方式2和方式3中发送的附加位数据。根据发送数据的需要由软件置位或复位。可作奇偶校验位,也可在多机通信中作区别地址帧或数据帧的标志位。在方式0、方式1中该位未用。

RB8:是在方式2和方式3中接收的附加位数据。可作约定的奇偶校验位,或是约定的地址/数据的标志位。在方式1中,若SM2=0,RB8中存放的是已接收到的停止位。方式0不使用 RB8。

TI:发送中断请求标志位。在方式0中,串行发送第8位结束时,由硬件置位TI;在其他3种方式中,串行发送停止位开始时,由硬件置位TI。TI=1表示一帧数据发送完毕。可由软件查询TI的状态,TI为1时,向CPU申请中断,CPU响应中断,TI标志必须由软件清零,才能再发送下一帧数据。

RI:接收中断标志位。在方式0中,串行接收到第8位数据时,由硬件置位RI;在其他3种方式中,串行接收到停止位时,硬件置位RI。RI=1表示一帧数据接收结束。可由软件查询RI的状态,RI为1时,向CPU申请中断,CPU响应中断,RI必须由软件清零,准备接收下一帧信息。

发送中断和接收中断是同一中断服务程序入口地址(0023H),所以在全双工通信时,必须由软件查询是发送中断TI=1,还是接收中断RI=1。

3 数据帧格式

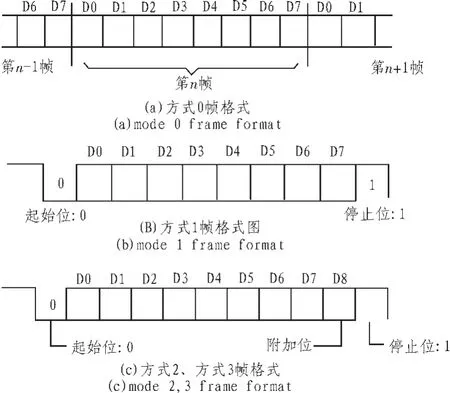

方式0以8位数据为一帧,不设起始位、停止位和奇偶校验位,如图3(a)。先发送或接收低位。工作方式0为同步移位寄存器输入/输出方式。常用于串行口外接移位寄存器以扩展I/O口,也可以外接串行同步输入/输出设备,不能用于单片机之间的通信。方式1为8位数据异步通信接口。传送一帧信息为10位。包括1位起始位(0)、8位数据位(先低位,后高位)和1位停止位(1),如图3(b)。方式2和方式 3为9位数据异步通信接口。传送一帧信息为11位,包括1位起始位(0),8位数据位(先低位,后高位),1位附加可编程控制位,1 位停止位(1),如图 3 (c)所示。

图3 数据帧格式Fig.3 Data frame format

4 波特率设置

方式1与方式3发送和接收数据时的波特率相同,波特率是由内部定时器T1送来的溢出信号经过16或32分频(取决于SMOD位,SMOD是电源控制寄存器PCON的最高位,当SMOD=1时,使串行口波特率加倍。)而得到的,波特率为=2SMOD/32×T1溢出率。波特率是可变的。

方式 2波特率=2SMOD/64×fosc,只有 2种:fosc/64或 fosc/32(取决于SMOD的值)。

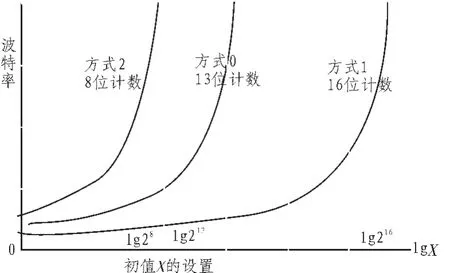

显然,波特率可以灵活改变的只有方式1和方式3,定时器T1作为可变的波特率发生器,T1工作方式有3种,可以工作在方式0(13位定时方式)、方式1(16位定时方式)和方式2(8位自动重装定时初值)。一般情况下,为了不影响波特率的精度,选用定时器工作方式2,且禁止T1中断定(ET1=0),以免T1溢出时产生不必要的中断。设定时器T1的初值为X,计数器长度为 L(取13、16和8)每过 2L-X个计数周期,T1就会产生一次溢出。溢出周期为:12/fosc(2L-X)。T1的溢出率为溢出周期的倒数,则

图4 波特率随初值X的变化Fig.4 Baud rate with initial X changes

从图4可以看出,如果串行通信选用较低的波特率时,将定时器T1设置定时方式1(16位计数)最好控制,X值的变化对波特率引影比较接近线性关系,变化比较平坦,易于对波特率的设置与微调。其次是方式0(13位计数),最后才是方式2。但在选用方式0或方式1的情况下,T1溢出时需由中断服务程序来重装计数初值,而且应该允许T1中断(ET1=1)。中断响应和中断处理的时间虽然会对波特率的精度带来一点误差,但也是可以根据指令执行周期进行校正克服的。

5 单片机通信

单片机之间的通信,可以利用其串行通信口,构成双机通信和多机通信系统。串行口控制寄存器SCON中的SM2为多机通信控制位[2]。

图5 主从式多机通信Fig.5 Master slave multi MCUs communication

双机通信时,在方式1处于接收状态时,SM2置为0,则接收到有效的停止位(高电平 1)时,才会激活 RI(即RI置1);在方式2和方式 3处于接收状态时,SM2置为0,则接收到第 9 位数据(RB8)=1 后,RI置 1。

多机通信,只有工作方式2和工作方式3,主机SM2置为0,由主机发起通信,当从机SM2置为1时,从机接收到第9位数据(RB8)=1后,RI才置 1;当从机 SM2置为 0时,则接收到第 9位数据(RB8)为0或1时,RI都置1。

1)双机通信数据传输

方式1发送数据时,数据从TXD端输出。只要执行把8位数据写入发送缓冲器SBUF命令,便启动串行口发送器发送。启动发送后,串行口能自动地在数据的前后分别插入1位起始位(0)和 1位停止位(1),以构成一帧信息,依次由TXD端上发出。在一帧数据发出之后,也就是在停止位输出时,使TI置1,用以通知CPU可以发送下一个数据。当一帧信息发完之后,自动保持TXD端的信号为1。接收数据时,数据从RXD端输入。在REN置“1”,允许接收器接收的前提下,在没有信号到来时,RXD端状态为1,当检测到有由1到0的变化时,就确认是一帧信息的起始位(0),便开始接收这一帧数据。把收到的数据一位一位地移入接收移位寄存器中,直到一帧数据全部接收完毕(包括1位停止位)。在RI=0并且SM2=0时,前8位数据装入SBUF中,置中断标志RI为1。如果不满足这两个条件,将丢弃接收到的信息,并不置位RI。

方式2和方式3的接收和发送操作完全一样,只是波特率设置不同。方式2(或方式3)发送数据时,数据由TXD端输出,发送一帧信息为11位,附加位数据D8是SCON中的TB8(可作奇偶校验位或地址/数据标志位,发送前根据通信协议由软件设置),CPU执行一条数据写入发送缓冲器SBUF的指令,就启动发送器发送,发送完一帧信息,置中断标志TI为1,发送过程和方式1相同。接收数据时,数据从RXD端输入。方式2(或方式3)在SCON中的REN=1,允许接收时,接收器开始采样RXD电平。当检测到RXD端有1到0变化时,启动接收器接收,把接收到的9位数据逐位移入移位寄存器中(含附加位),接收完一帧信息后,在RI=0并且SM2=0时,前8位数据装入SBUF中,附加位数据D8装入SCON中的RB8,置中断标志RI为1。如果不满足这两个条件,将丢弃接收到的信息,并不置位RI。

2)多机通信数据传输

图5所示为MCS-51多机通信系统的连接示意图。系统中只有一个主机,有多个从机。主机发送的信息可传到各个从机或指定的从机,而各个从机发送的信息只能被主机接收。

当串行口以方式2(或方式3)接收数据时,SM2=1,则仅当接收器接收到的附加位RB8=1时,本帧数据才装入接收缓冲器SBUF,且置RI为1,向CPU发出中断请求信号;若RB8=0,则不产生中断请求信号,数据将丢失。而SM2=0时,则接收到一个数据字节后,不管RB8=0或RB8=1,都产生中断请求信号RI,接收数据装入SBUF中。应用这一特性,便可实现多个MCS-51单片机之间的串行通信。

在多机通信时,主机发送的信息有两类,即地址和数据。地址是需要和主机通信的从机地址。例如,将图5中3个从机的地址分别定义为00H,01H,02H。主机和从机串行口工作在方式2(或方式3),即9位异步通信方式。主机发送的是地址信息时特征是D8=1,而发送的是数据信息时特征是D8=0。对于从机就要利用SM2位的功能来确认主机是否在呼叫自己,及数据传送。从机处于接收时,置SM2=1,然后依据接收到的串行数据的附加位的值来决定是否接收主机信号,多机通信实现过程如下。

首先定义从机地址,由系统初始化程序(或相关处理程序)将从机串行口编程为方式2或方式3接收(9位异步通讯方式),然后置从机SM2=1,REN=1,允许串行口中断。

①主机首先将要通信的从机地址发出,发地址时D8=1,所有从机都接收。

② 从机串行口接收D8=1时,则置位中断标志RI,各从机CPU分别响应中断。

③各从机执行中断服务程序,以判断主机送来的地址是否与本机地址相符。若与本机地址相符,则SM2清零,准备和主机通信;若地址不一致,则保持SM2=1。

④ 主机发送数据(附加位为0)。

⑤ 从机接收到D8=0的信息帧(表示数据),只有SM2=0的从机才激活中断标志RI=1,转入中断程序,表示接收主机的数据或命令,实现主机与从机的信息传送。而其他从机因SM2=1,附加位为0,不激活RI中断标志,接收的信息自动丢失不作处理,从而实现主机和从机的一对一通信。

⑥从机在通信完成后,重新使SM2置1,并退出中断服务程序,等待下次通信。

用定时器T1,定时器T1工作在方式1(16位计数方式)作为波特率发生器,由设定的波特率得到的此时的初装值为XXH,将主机中的数据块(数据块长度放在R7中)传送到从机。

主机程序:

DATA_BUF EQU 40H;数据存放区首地址

SLAVE_ADDR EQU 30H;从机地址

ORG 0000H

AJMP MAIN

ORG 001BH

AJMP INT_T1

ORG 0050H

MAIN:MOV TMOD,#10H;定时器T1初始化,工作方式1

MOV TH1,#0XXH

MOV TL1,#0XXH

MOV SCON,#0D0H ;串口工作在方式3,多机位值 SM2=0,允许接受

SETB TB8,#1 ;发送地址标志

SETB TR1 ;启动定时器1

SETB IT1

SETB ES

SETB EA

MOV A,SLAVE_ADDR;发送从机地址

MOV SBUF,A

JNB TI,$

CLR TI

MOV TB8,#0 ;发送数据标志

MOV R0,#DATA_BUF

HERE: MOV SBUF,@R0;发送数据

JNB TI,$

CLR TI

DJNZ R7,HERE

SETB TB8

MOV SBUF,A SJMP$

INT_T1:MOV TH1,#0XXH

MOV TL1,#0XXH

RETI

END

从机程序:

FLAG BIT 2AH ;数据传送标志

ADDR_ACK EQU 1AH

DATA_BUF EQU 40H

TEMP_BUF EQU 31H ;数据暂存器

ORG 0000H

AJMP MAIN

ORG 001BH

AJMP INT_T1

ORG 0023H

AJMP HANDLEDATA

ORG 0050H

MAIN:MOV TMOD,#10H;定时器T1初始化,工作方式1

MOV TH1,#0XXH

MOV TL1,#0XXH

MOV SCON,#0F0H;串口工作在方式3,多机位SM2=1,允许接收

CLR FLAG

SETB TR1 ;启动定时器T1

SETB IT1

SETB EA

AJMP$

HANDLE_DATA:CLR RI

MOV A,SBUF

MOV TEMP_BUF,A

SEND:JNB RB8,DATA_RECEIVE

CJNE ADDR_ACK,TEM_BUF, XXXX

JB FLAG OVER

SETB FLAG

CLR SM2

RETI

OVER:SETB SM2

CLR FLAG

RETI

DATA_RECEIVE:MOV DATA_BUF,TEMP_BUF

INC DATA_BUF

XXXX:RETI

INT_T1:MOV TH1,#0XXH

MOV TL1,#0XXH

RETI

END

在进行上述多机通信时,要先运行从机中的接收程序,再运行主机中的发送程序。

6 结束语

简要阐述了单片机[7-8]通信方式及串行接口的原理,并通过实例介绍了单片机串行多机通信频率可调的实现方法,经过实验验证,文中所提出的波特率可调方法具有简单、准确、调节范围广的特点。可以应用于几乎所有的具有波特率的串行通信系统中,满足多种特定环境通信速率的不同要求。

[1]郑毛祥.单片机基础[M].2版.北京:人民邮电出版社,2009.

[2]李云鹤,武善玉.基于ISP的简约型51单片机实验板的设计[J].微计算机信息,2008,5(2):95-97.LI Yun-he,WU Shan-yu.Based on ISP compact 51 MCU experimental board design[J].Microcomputer Information,2008,5(2):95-97.

[3]李晓鹏,王民.单片机串行通信自适应波特率的一种简单实现算法[J].现代计算机,2010(10):90-93 LI Xiao-peng,WANG Min.MCU serial communication baud rate of a simple adaptive algorithm[J].Modern Computer,2010(10):90-93.

[4]洪沙.阳翰凌·单片机多机通信中从机串口中断服务程序设计[J].微机应用,2008(12):153-155.HONG Sha,YANG Han-ling.The single-chip microcomputer communication from the machine serial port interrupt service program design[J].Microcomputer Application,2008 (12):153-155.

[5]潘策,陈晓南,杨培林.PC机与单片机串行通信的硬件设计[J].现代电子技术,2003(15):4-8.PAN Ce,CHEN Xiao-nan,YANG Pei-lin.PC machine serial communication with the MCU hardware design[J].Modern Electronic Technology,2003(15):4-8.

[6]彭宗乾.MCS-51单片机多机通信的组成原理及通信程序[J].通迅与电视,1992(2):20-22.PENG Zong-qian.MCS-51 MCU communication principle and communication program[J].Communication and Television,1992(2):20-22.

[7]孙俊,王京梅,李莉,等.基于单片机的串联锂离子电池组监测系统设计[J].电子科技,2011(10):4-6.SUN Jun,WANG Jing-mei,LI Li,et al.Design of supervising and measuring system of serial lithium-ion batteries based on MCU[J].Electronic Science and Technology,2011(10):4-6.

[8]吴汶泰,扈维,林胜洁.分布式单片机网络中CSMA的软件设计与性能分析[J].电子科技,2009(7):93-95.WU Wen-tai,HU Wei,LIN Sheng-jie.Software design of CSMA in the distributed SCM Network and its performance analysis[J].Electronic Science and Technology,2009(7):93-95.