SoC门级功耗分析方法

2011-05-22徐永钊田祖伟阳若宁姚丽娜李洪涛曾志峰

徐永钊,田祖伟,阳若宁,姚丽娜,李洪涛,曾志峰

(①东莞理工学院,广东 东莞 523808; ②湖南第一师范学院,湖南 长沙 410000; ③湖南广播电视大学,湖南 长沙 410004)

0 引言

自20世纪90年代后期SoC(System on a Chip)出现以来,随着超深亚微米工艺的不断发展,SoC的发展日新月异,基于片上系统SoC的便携式电子产品越来越广泛地应用于人们的日常生活和工作中[1]。随着集成电路设计规模的增加和芯片运行频率的提高,集成电路设计中低功耗的需求也随之提高。当今SoC低功耗设计技术纷繁复杂,几乎芯片设计的方方面面都有低功耗设计的技巧。例如系统级的定义和划分、功耗管理模块、低功耗指令集的选取、结构级的总线低功耗方法、版图级的缩小芯片面积、缩短互连线长度,这些都是可能降低SoC芯片功耗的方法[2]。要知道这些方法是否有效地降低了芯片的功耗,需要一套比较精确的功耗分析和估计技术。一套精确有效的功耗评估方法,有利于设计人员及时了解改动引起的功耗变化,有利于采用功耗较优的设计细节,兼顾功能的正确和功耗的优化。

1 功耗分析基础

1.1 功耗模型

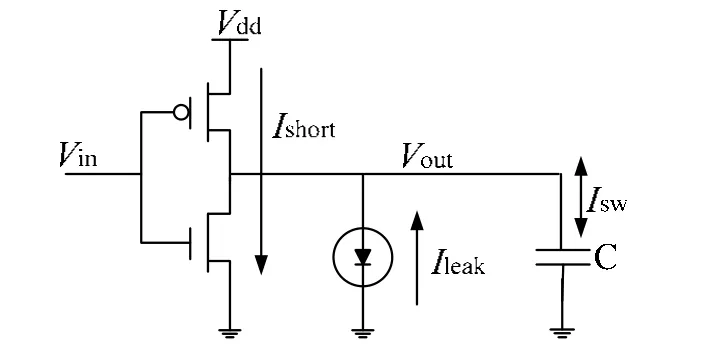

以CMOS门单元为基础的SoC电路的功耗,主要有三种功耗因素[1],即:信号变化时,电路电容充放电功耗;信号有限的上升和下降时间引起的短路电流;结反偏时的漏电流。

1.1.1 充放电功耗

充放电功耗是指当 CMOS电路的输出端电平发生变化时,此输出端的所有电容充放电所消耗的功耗,功耗大小正比于总的容性负载。

以CMOS反相器为例,如图1所示,C是寄生电容和负载电容的总和,包括后继单元的输入门电容、互连电容和反相器源漏区的电容三种类型的电容。深亚微米工艺中,门的尺寸按比例缩小,互连电容将逐渐占主要作用。假设输入信号的翻转概率为α,电路的时钟频率为f,则电路功耗可粗略地估计为CV2ddfα。

图1 CMOS反相器

动态充放电功耗在CMOS电路中起决定作用,大约占全部功耗的70%~90%,因此,低功耗分析研究的主要重点就在于准确地估计信号活性和节点的电容。信号翻转率α是功耗估计和分析中最重要的参数。

1.1.2 短路电流功耗

理想的CMOS电路的晶体管改变状态不需要时间,不存在从电源到地的通道。当输入门的上升/下降时间大于输出的上升/下降时间时,可能存在从电源到地的短路电流。如果n型 MOS管的开启电压是VTn,p型 MOS管的开启电压是VTp,则当VTn< Vin< Vdd-|VTp|成立时,将出现从源到地的短路电流。输入上升/下降时间越长,则短路电流存在的时间越长,平均短路电流越大。

对于大多数芯片,短路电流功耗占总的动态功耗的5%~10%。如果电源电压低于两种晶体管的开启电压之和,即Vdd< VTn+|VTp|,则可以消除短路电流,但低电源电压是以降低芯片速度为代价的。

1.1.3 漏电流功耗

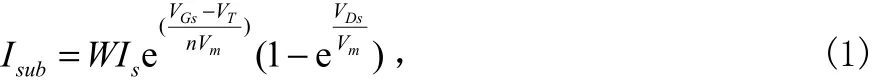

漏电功耗包括由寄生反向PN结漏电和亚阈区漏电引起的功耗,其中寄生反向 PN结漏电引起的功耗很小,可忽略不计,而亚阈区漏电流的公式如下:

其中 Vtm = kT/q是热效应电压,k是普朗克常量,q为单位电荷,T为绝对温度,VT为阈值电压。从公式(1)可以看出,亚阈区漏电流与阈值电压有密切关系。当阈值减小时,亚阈区漏电流会呈指数级快速增大。

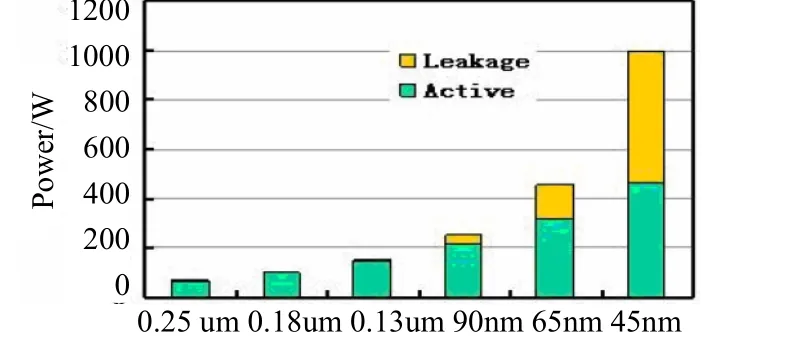

实验表明,对于目前国内主流工艺下(0.18μm)的SoC,90%~99%的功耗来源于信号跳变导致的负载电容充放电,如图2所示[3],功耗评估的重点是动态功耗。

1.2 功耗分析层次

功耗分析可以利用不同粒度模型的层次化分析方法,从而获得精确性和效率间的折衷[4-5]。功耗分析可分为四个层次:

1.2.1 晶体管级

晶体管级模拟采用非线性的电流、电压和电容建模电路行为,误差主要来源于对寄生参数的建模,它可以处理动态的和静态的功耗。SPICE、Nanosim是这类工具中比较典型的,但它们通常只能用来仿真数万门规模的电路,而且要花费数天的时间,甚至可能不收敛。

图2 动态功耗和静态漏流功耗对比

1.2.2 门级

使用集总电容模型,即所有电容都归并到门的输出结点,其精确值由单元库、扇出和互连决定。厂商一般会提供门单元对应不同输入和输出负载情况的功耗精确值查找表,如图3所示,通过向查找表输入负载和输入信号质量就可以获得当前情况下的功耗估计值。

图3 门单元电路的功耗查找表

1.2.3 寄存器传输级

随着系统集成度的提高,功耗分析方法的重心都在向更高层移动。寄存器传输级(RTL级)的电路抽象为组合电路块和其输入输出端状态锁存器的互连。在行为级仿真时,获取电路块的输入输出数据的统计参数,然后将电路模块的电容表示为这些参数的函数。

1.2.4 行为级

动态功耗依赖于物理电容,而在行为级,设计细节未实现以前,估计物理电容是困难的。行为级功耗分析方法可分两类,一是建立电路模块电容与电路复杂性和工艺参数之间的解析关系模型,二是映射到RTL级或门级,使用RTL级或门级的功耗分析技术。

要精确分析功耗,需要精确计算出电路内部节点中的翻转率(Switching Activity)。最简单的方法是使用电路仿真。晶体管级分析的优点是可以比较真实地反映芯片工作状态,功耗数值的估计也比较准确。但缺点也很明显,对超大规模电路设计来说,需要大量的计算模拟大量内部节点的信号跳变,仿真速度还较慢,严重影响功耗分析效率。寄存器级和行为级分析方法则相反,要精确计算电路内部节点在特定时间内的平均跳变电容量是比较困难的,但因为仿真节点大大简化,速度比晶体管级快得多。门级分析则在精度和速度之间达到了很好的平衡,因为门级可以直接从工艺库中提取出精确的电容信息,仿真的节点数又少于晶体管级,是这里准备重点介绍的功耗分析方式。

2 门级功耗分析方法

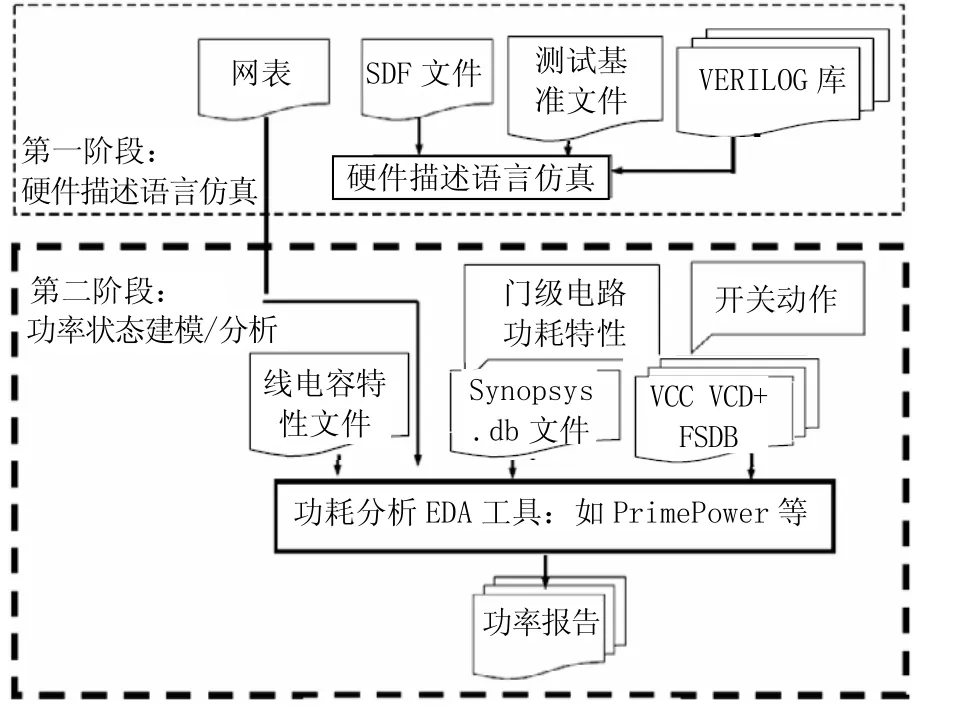

SoC电路门级功耗分析的流程如图4所示[6-7]。

图4 门级功耗分析流程

其中第一阶段的网表是逻辑综合后的门级单元,SDF文件记录的是各门单元的门延时和门电路间的互连延时,第二阶段要求的线电容特性和门级电路的功耗特性都包含在门电路延时特性记录文件(.db)中。

利用上述的门级功耗分析流程,对设计中的一个SoC子电路SPI模块进行了功耗分析。分析之前首先需要对已经设计完成的SPI模块进行逻辑综合,获得门级网表,和门级电路的延时反标文件;然后采用预先编制的测试激励对综合后的门级网表进行带延时的仿真,输出电路各节点的波形变化;最后利用功耗分析工具,这里使用PrimePower,读入网表信息、电路工艺信息和节点波形,就可以输出SPI电路的门级功耗分析报告。

3 结语

采用相同的测试激励对 SPI接口进行仿真,门级和晶体管级功耗分析得到SPI接口电路的功耗情况如表1所示。

表1 门级和晶体管级功耗分析对比

从上述对比可以看出,门级功耗分析在与晶体管级功耗分析误差不超过33%的情况下,分析时间缩短了近20倍,大大提高了对类似SoC这样的大规模集成电路的处理能力。因此,对于SoC设计而言,门级功耗分析是非常有效的功耗评估手段。

[1]张志敏,常晓涛.SoC低功耗设计技术发展综述[J].信息技术快报,2005(04):5-14.

[2]LANDMAN P. Low-power Architectural Design Methodologies[D].California: University of California, Berkeley, 1994.

[3]HU J G, LIN G, LI Siyu. Simulation Platform for Smart Card Chip[J]. Journal of Information and Computational Science,2008, 5(12):2459-2464.

[4]胡建国,谭洪舟,位召勤,等. 低功耗RFID 电源产生电路的优化设计[J].半导体技术,2008(09):825-839,

[5]张忠志,胡建国.无源RFID标签天线接口电路研究与实现[J].通信技术,2008,41(12):22-25.

[6]胡建国,陈亮.面向 CPU芯片的验证技术研究[J].微电子学,2007(02):17-23

[7]王鹏飞,郑龙根.短波电路仿真测量研究[J].通信技术,2008,41(12):104-106.