基于FPGA的语音存储与回放系统

2011-04-27河南大学闫占强

河南大学 梁 勇 闫占强

前言

数字化语音存储与回放系统的作用是对声音信号进行存储和回放,并实现数字化控制。能够做到的控制方法有很多,譬如单片机控制、DSP控制、FPGA控制等。本文研究的是基于FPGA控制下的语音存储与回放系统,在该系统中,没有使用专用的语音处理芯片,而是利用FPGA作为核心控制器,完成语音信号的数字化处理,从而实现语音的存储与回放。

1.系统总体结构

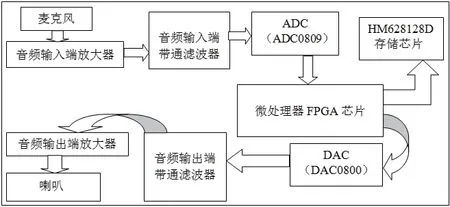

图1 数字化语音存储与回放系统示意图

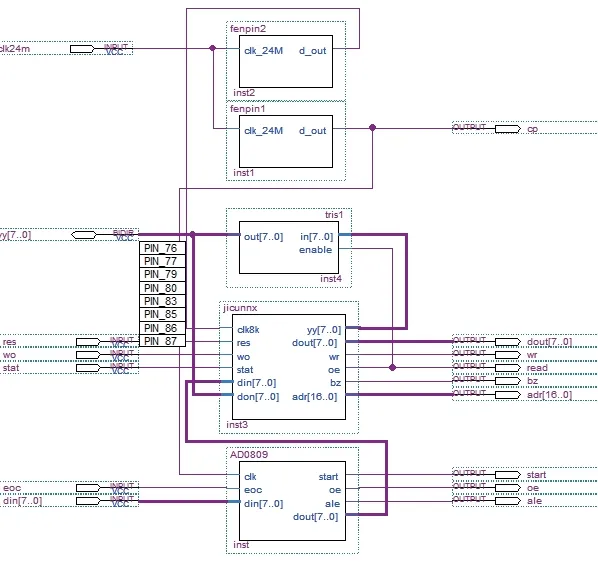

图2 FPGA外部接线

该数字化语音存储与回放系统的基本工作原理是:将麦克风采集到得语音信号经过模拟放大和滤波处理后,通过模数转换器(A/D)转换成数字信号,再通过控制器(FPGA)的控制存储在存储器中;回放时,由控制器(FPGA)将数据从存储器中读出,然后通过数模转换器(D/A)转换成模拟信号,经放大后由扬声器输出。当然,为了实现高质量的音质要求,在AD之前及DA之后,用带通滤波器滤除不必要的噪声,以达到较好的效果。人实际说话的频率范围300~3400Hz,所以滤波器设计在该频道范围。

本设计方案系统总体结构框图如图1所示。

2.主控电路

2.1 FPGA顶层电路

FPGA顶层接线如图2所示。在该设计中clk24m接24MHz晶振;cp接ADC0809模数转换电路;yy[7..0]接HM628128D;res接按键开关,res为0时地址复位;wo接高低电平开关,wo为0时录音为1时放音;dout[7..0]接D/A转换器的数据输入端;wr、read、adr[16..0]接HM628128D;bz接发光指示灯,显示录音或放音工作状态;其余端接ADC0809模数转换电路。

2.2 各部分介绍

分频器1,用来产生存储器所需要的存储时钟;分频器2,用来产生AD芯片所需要的采样时钟。

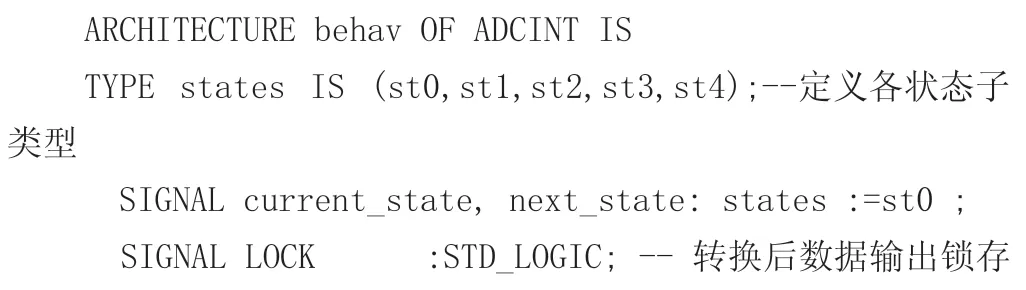

根据数模转换电路ADC0809的功能实现以及各管脚的具体作用,我们可以对ADC0809进行控制,以实现其数模转换的作用。

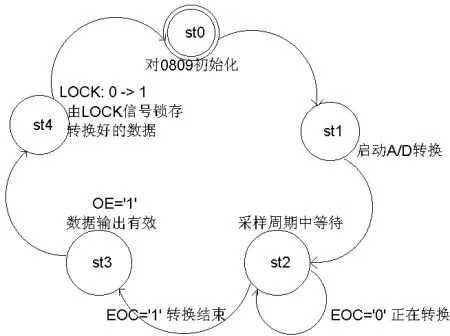

AD0809的采样工作时序如图3所示,我们可以根据该时序,画出控制器的时序转换图,如图4所示。

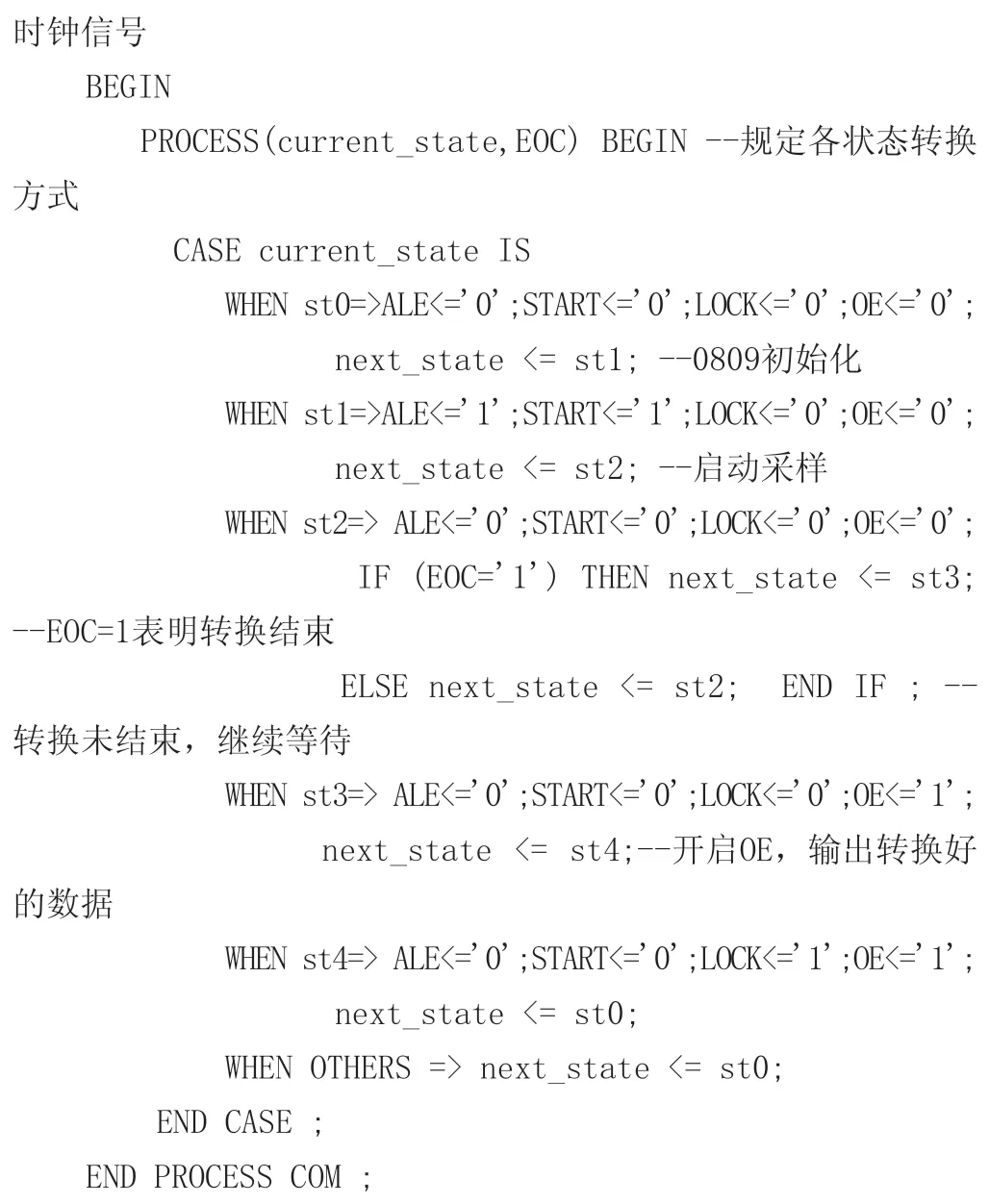

我们用状态机的思想设计该控制器。以下是部分代码。其实现的电路封装后的形式如图2的最下面的芯片。

图3 AD0809采样时序

图4 ADC0809采样状态图

存储芯片HM628128D控制模块为jicunnx。在实际的操作过程中,任何存储芯片对于数据的存储与读取都需要一定的控制信号,这样方能实现数据的存储与读取。为此,我们在FPGA芯片中对于该存储芯片的控制进行了设计。同样用状态机的思想来实现,程序略。

三态门,由于存储芯片HM628128D的数据端是双向端口,输入输出共用,所以FPGA和它连接的时候需要设计三态门,使得在HM628128D进行读操作时,三态门处于高阻状态。其实现的电路封装后的形式如图2的tris1的芯片。

3.电路仿真

控制电路我们使用quartusⅡ自带的仿真工具进行验证。

3.1 分频器的仿真

对于分频器电路来说,我们可以通过quartusⅡ自带的仿真软件进行仿真,由于分频器1和分频器2完全相同,可以对任意一个进行仿真即可,对分频器1的仿真结果如图5所示。

该设计所使用的分频器为48分频,由图5可以看出该设计达到了要求。

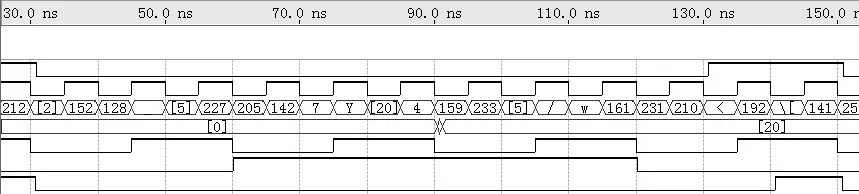

3.2 模数转换电路ADC0809控制模块的仿真

由该图(图中信号从上到下依次为:ale,clk,din[7..0],dout[7..0],eoc,oe,start)可以看出,在clk下降沿时刻,当eoc为高电平时,就将din[7..0]的数据传送给dout[7..0],ale与start则周期性的出现(由于输入eoc的周期出现)。从而实现信号转换的开始与锁存。

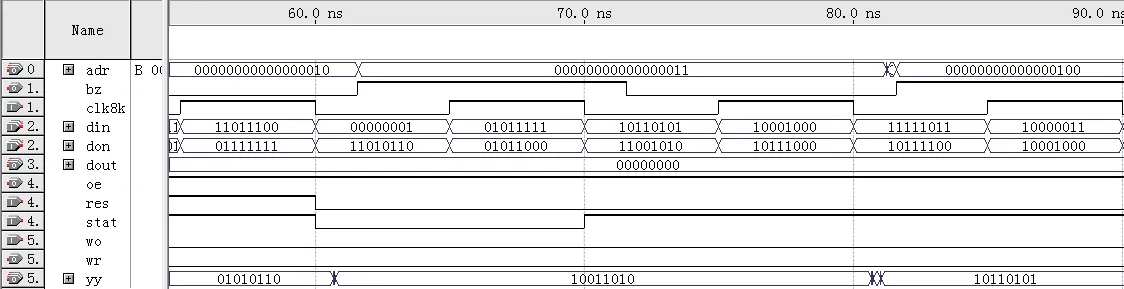

3.3 三态门电路的仿真

该三态门所能实现的功能是:当写入时,wr=0,read=1,tris1为打开状态,DIN[7..0]通过输出YY[7..0]写入芯片HM628128D,当读出时,wr=1,read=0,此时,trish高阻状态,由芯片HM628128D读出数据,DON[7..0]通过DOU[7..0]送到DAC0800中。该三态门实现8位数据的传输。其仿真结果如图7所示。

图5 分频器电路的仿真结果

图6 ADC0809控制模块的仿真

图7 三态门电路的仿真结果

图8 存储芯片控制模块的仿真结果

3.4 存储芯片控制模块的仿真

对于存储芯片的控制模块的仿真结果如图8所示。

由图中可以看出,该设计可以对存储芯片HM628128D的存储与读取进行控制,实现其功能。

结论

在本设计中,实现了用FPGA芯片控制语音的存储与回放,由于FPGA芯片自带容量较小,无法实现大量数据的存储,所以使用了HM628128D实现存储容量的扩展,这样可以使语音存储时间为10s以上。如果在软件中增加压缩算法,可节省存储空间,是一种实用的电路方案。

[1]张常年,王振红.全国大学生电子设计竞赛训练精选[M].北京:化学工业出版社,2010.

[2]王诚,吴继华等.Altera FPGA/CPLD设计(基础篇)[M].北京:人民邮电出版社,2005.

[3]潘松,黄继业.EDA技术实用教程(第三版)[M].北京:科学出版社,2007.

[4]李洋.EDA技术实用教程(第二版)[M].北京:机械工业出版社,2009.

[5]徐志军等.CPLD/FPGA的开发与运用[M].北京:电子工业出版社,2002.

[6]Peter Wilson著.杜海生,等译.FPGA设计实践[M].北京:人民邮电出版社,2009.

[7]华成英,童诗白.模拟电子技术基础(第四版)[M].北京:高等教育出版社,2006.