CMOS集成电路闩锁效应抑制技术

2010-09-05董丽凤李艳丽王吉源

董丽凤,李艳丽,王吉源

(江西理工大学信息工程学院,江西 赣州 341000)

CMOS集成电路闩锁效应抑制技术

董丽凤,李艳丽,王吉源

(江西理工大学信息工程学院,江西 赣州 341000)

闩锁效应是CMOS集成电路在实际应用中失效的主要原因之一,而且随着器件特征尺寸越来越小,使得CMOS电路结构中的闩锁效应日益突出。文章以P阱CMOS反相器为例,从CMOS集成电路的工艺结构出发,采用可控硅等效电路模型,较为详细地分析了闩锁效应的形成机理,给出了闩锁效应产生的三个基本条件,并从版图设计和工艺设计两方面总结了几种抑制闩锁效应的关键技术。

CMOS集成电路;闩锁效应;可控硅;抑制

1 引言

CMOS(Complementary Metal-Oxide-Semiconductor)集成电路是目前大规模(LSI)和超大规模(VLSI)集成电路中广泛应用的一种电路结构,相对于传统的双极型、NMOS和PMOS集成电路而言,其在功率消耗、噪声抑制等方面具有明显的优势,虽然CMOS电路具有以上众多优点,但也有一些由于自身结构引发的寄生效应限制了其优越性的充分发挥,隐含于体硅CMOS(指在硅衬底上制作的CMOS)结构中的闩锁效应就是一个最典型的例子,并且随着器件尺寸的不断缩小,闩锁效应对电路性能的影响将愈发明显。

2 闩锁效应及其形成机理

闩锁效应(latch up)是指在体硅CMOS结构中,从电源到地存在的PNPN寄生可控硅结构,在满足可控硅触发条件下,引起电源到地的极大电流,破坏电路正常工作乃至烧毁整个电路的现象,也称自锁效应。闩锁效应往往发生在芯片中某一局部区域,有两种情况:一种是闩锁只发生在外围与输入输出有关的地方,另一种是闩锁可能发生在芯片的任何地方,在使用中前一种情况遇到较多。

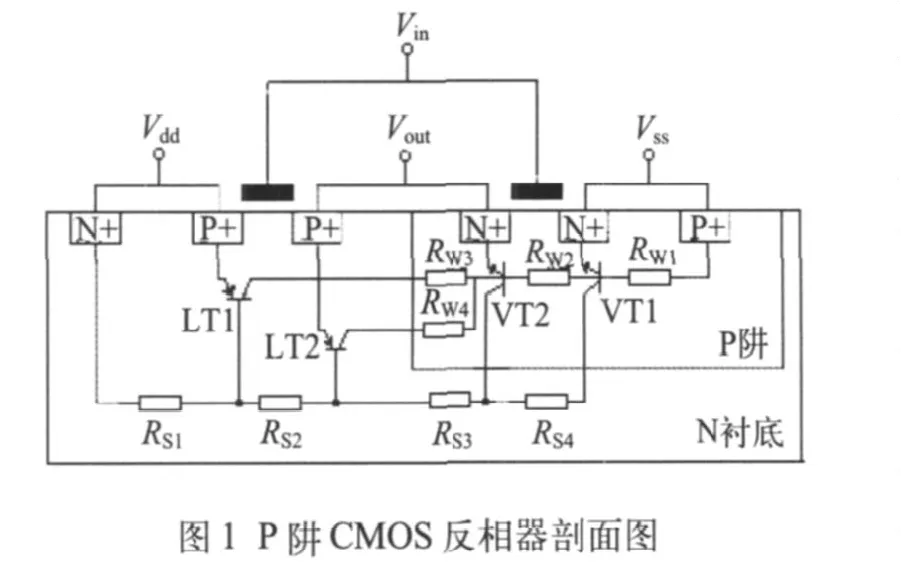

下面以一个P阱CMOS反相器为例,来说明闩锁效应的形成机理[1-2]。图1是CMOS反相器的剖面图。从图1中我们可以看出,在形成CMOS反相器结构的同时,也不可避免地产生了由寄生双极晶体管构成的PNPN器件,即可控硅(SCR),该可控硅器件由两个横向的PNP双极型晶体管和两个纵向的NPN双极型晶体管组成,即P沟道MOSFET的源(漏)极、N型衬底以及P阱分别为横向PNP双极晶体管LT1(LT2)的发射极、基极和集电极;N沟道MOSFET的漏(源)极、P阱及N型衬底分别为纵向NPN双极晶体管VT1(VT2)的发射极、基极及集电极,这种寄生的纵向NPN晶体管和横向的PNP晶体管通过P阱和共同的衬底耦合。

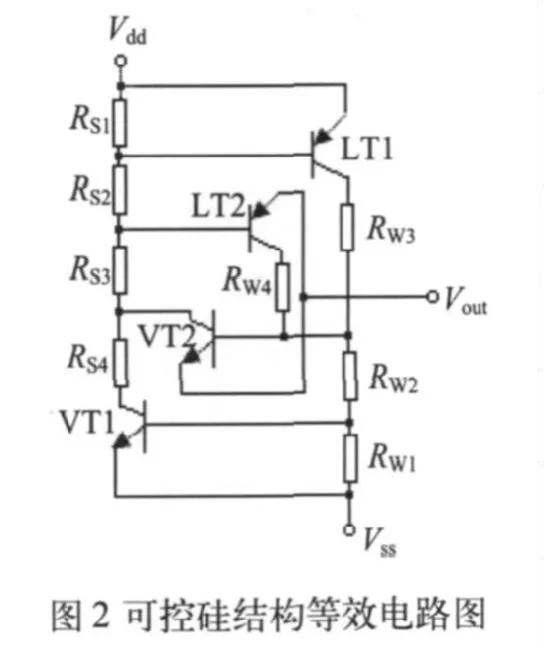

因此我们可以得到寄生可控硅结构的等效电路图,如图2所示。

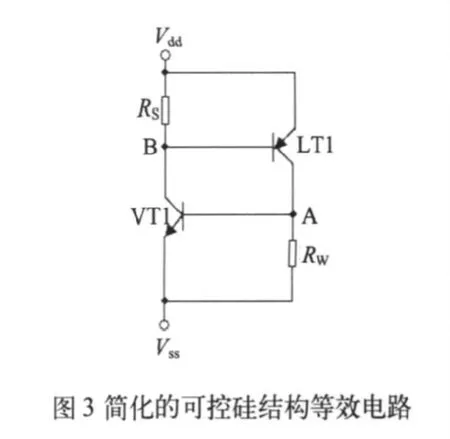

从图2中可以看出,双极晶体管VT2、LT2可以不予考虑,因此可以将该电路进行简化,得到简化的可控硅结构等效电路图,如图3。由寄生部分的等效电路图分析闩锁效应发生的条件。由图3可见寄生电路在LT1和VT1之间形成了一个正反馈回路,在正常情况下,由于Vdd与Vss之间有一个反偏的阱与衬底PN结隔离,只有很小的二极管漏电流在其间流过,不会对反相器正常工作产生影响。但当CMOS集成电路接通电源后,如果在A点有电流注入,会使节点电压VA上升,即NPN管VT1的VBE增大,当VBE增大到一定程度时(>0.7V),纵向NPN晶体管VT1会导通而进入放大区,导致IC2增大,故使得VB下降,VB下降则LT1的VBE也增大,导致|IC1|增大,最终导致VA进一步上升,一旦LT1和VT1之间形成的正反馈回路增益大于或等于1,上述过程将持续下去,直至两个晶体管完全导通,在Vdd与Vss之间产生很大的电流。此时,即使A点的注入电流消失,Vdd与Vss之间的电流仍然存在,这就是闩锁效应的形成过程。

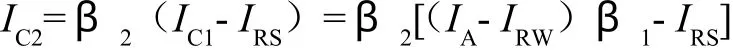

下面导出产生闩锁效应的条件,假设NPN管的共射电流增益为β1,PNP管的共射电流增益为β2,A点的注入电流为IA。根据射、集、基极的电流关系有:IA=IRW+IB1,IC1=β1IB1,IC1=IRS+IB2,IC2=β2IB2,所以:

式中IRW、IRS较小,因此有:IC2≈β1β2IA。

若β1β2>1,则IA的反馈量IC2>IA。这样两个寄生管同时工作,形成正反馈回路,加深了可控硅导通,在电源和地之间形成极大的导通电流,并使电源和地之间锁定在一个很低的电压,即该电路被闩锁。

由上述分析可总结出产生闩锁效应的三个基本条件,即:

(1)环路增益必须大于1,即βNPN×βPNP≥1;

(2)横向PNP管和纵向PNP管的发射结都被加正偏电压;

(3)电源所提供的最大电流大于寄生可控硅导通所需要的维持电流。

3 闩锁效应的抑制技术

由以上分析可知,闩锁效应起因于寄生的可控硅结构,且其发生需具备一定的条件,因此只要破坏产生闩锁效应的三个基本条件或其中之一,就能有效地避免闩锁的发生。在实际应用中,通常可从版图和工艺等方面采取措施,消除闩锁效应的发生。

3.1 版图设计考虑

3.1.1 保护环技术

由产生闩锁效应的基本条件可知,减小电阻RS和RW,降低寄生三极管的电流放大倍数βNPN,βPNP,可有效提高抗闩锁的能力。因此,可以通过在版图设计中引用保护环技术[3]来实现减小衬底电阻RS和阱区电阻RW的目的。图4为增加了保护环的反相器剖面图。

从图中看出所谓保护环即是在N衬底区P沟道器件的周围加上接电源Vdd的N+环;在P阱区N沟道器件的周围加上接Vss的P+环。

3.1.2 合理布局电源接触孔

合理布局电源接触孔,可以降低横向电流密度和衬底电阻RS,减小寄生晶体管的放大倍数, 同样可以达到抑制闩锁的目的。需注意的问题如下[4]:

(1)采用接衬底的环形Vdd电源线(P阱),并尽可能将衬底背面接Vdd;

(2)增加电源Vdd和Vss接触孔,并尽可能加大接触面积;

(3)P阱CMOS中接Vdd的孔尽可能安排的离阱远一些,接Vss的孔要尽可能安排在阱的所有边缘上。同时对每一个接Vdd的孔都要在相邻的阱中配以对应的Vss接触孔,并尽量使Vdd和Vss的接触孔的长边相互平行。

3.2 工艺方面考虑

3.2.1 外延衬底技术

外延衬底技术[5]主要是通过减小衬底电阻RS达到抑制闩锁的目的。普通N型衬底工艺是将整个电路做在一个低掺杂的N-型衬底上,使得衬底电阻RS较大,外延衬底则是采用双层衬底,即在低掺杂的N-型衬底下方还有一层较高掺杂的N+衬底,以此大大减小了衬底电阻RS,增加了闩锁的预防水平。

3.2.2 倒退阱

类似于高注入的衬底,倒退阱可以降低阱的电阻RW,防止纵向的寄生三极管开启。制作倒退阱有多种方法,如埋层的外延层,高能离子注入及反型杂质的注入等。

3.2.3 沟槽隔离

所谓沟槽隔离就是在PN有缘区之间形成一个绝缘的槽体,绝缘物质通常为二氧化硅,以此来降低横向三极管的增益,削弱NMOS晶体管和PMOS晶体管之间可能形成的寄生连接,从而起到预防闩锁的作用。槽的深度越深,对闩锁的防治效果就越好。

3.2.4 SOI技术

SOI工艺技术是指在表层与衬底之间加入一层绝缘层,由于有了更高的阻抗,使电子迁移不会传到下层,使电子束或电子本身的迁移速度加快,从而提高了整个芯片的性能,使芯片速度更快、耗电更少、电路密度更高。由于绝缘层的存在,阻断了PNPN放电路径的形成,从根本上避免了闩锁的形成。

4 结束语

随着CMOS集成电路的飞速发展,芯片上的器件尺寸越来越小,闩锁效应的预防问题变得愈发重要,因此需尽可能地避免、降低或消除闩锁效应的形成,从而为CMOS电路的广泛应用奠定基础。

[1]牛征.CMOS电路中的闩锁效应研究[J].电子与封装,2007,3.

[2]钱敏等.CMOS集成电路抗闩锁策略研究[J].集成电路应用,2005,2.

[3]唐晓峰等.CMOS电路抗闩锁研究[J].微处理机,2009,2.

[4]朱正涌.半导体集成电路[M].北京:清华大学出版社,2000.

[5]艾伦等著,冯军等译.CMOS模拟集成电路设计[M].北京:电子工业出版社,2005.

Overview on the Prevention of Latch-up Effect in CMOS IC

DONG Li-feng, LI Yan-li, WANG Ji-yuan

(Jiangxi University of Science and Technology,Ganzhou341000,China)

Latch-up effect is one of main cause that CMOS IC becomes invalid in application, and as device channel length becomes smaller and smaller, Latch-up effect in CMOS structure is stand out increasingly. Based on CMOS inverter in P-well, the structure of CMOS IC are presented.SCR equivalent circuit model is took to analyze the mechanism of latch-up in detail, gives three main conditions that latch-up becomes and sums up several kinds of key technology in prevention from layout and process.

CMOS IC; latch-up effect; SCR; prevention

TM341

A

1681-1070(2010)09-0028-03

2010-04-16

董丽凤 (1981-),女,辽宁锦州人,2007年辽宁大学毕业,硕士,助教,研究方向为微电子学与固体电子学。