基于FPGA和DSP的扩频信号发生器设计与实现

2010-08-06王杰,康潇

王 杰, 康 潇

(民航河南空管分局, 河南 郑州 451162)

0 引言

数字多波束天线扩频通信系统作为一种具有较强的抗干扰能力和低信噪比门限的相关接收特性的通信体系,是现代通信领域的一个重要发展方向。我们在调试数字多波束天线扩频通信系统时必要要用到专门设计的扩频信号发生器,因此提出一种扩频信号发生器实现方案。

1 扩频信号产生原理及系统方案

扩频通信可以显著提高通信系统抗干扰的能力,特别是频率选择性衰落和多径干扰。为此在发端输入的信息先经信息调制形成数字信号,然后由扩频码发生器产生的扩频码序列去调制数字信号以展宽信号的频谱。展宽后的信号再调制到射频发送出去[1]。一般的扩频通信系统都要进行三次调制,一次调制为信息调制,二次调制为扩频调制,三次调制为射频调制。在扩频通信中需要用高码率的窄脉冲序列,即伪随机码或简称 PN码。这类码序列最重要的特点是近似噪声的特性。但是真正的随机序列是不可能重复和产生的,因此我们只能产生一种类

周期性的脉冲信号来近似噪声的特性,二元M序列是一种最常见的伪随机序列我们采用它作为我们的扩频序列[3]。

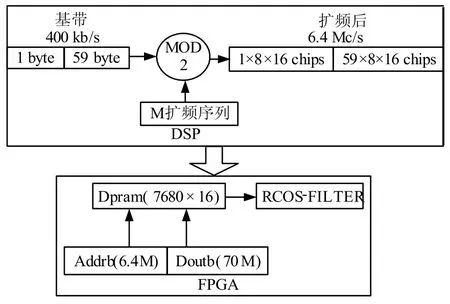

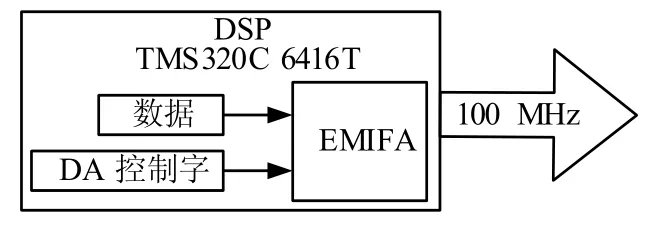

在硬件平台上,本系统(见图1)采用TI公司的TMS320C 6416T,它的主频最高可达 600 MHz,可以满足高性能数字信号处理的要求,故我们采用它作为主处理器来实现用户数据扩频和D/A控制字的设置[2]。

图1 系统方案框

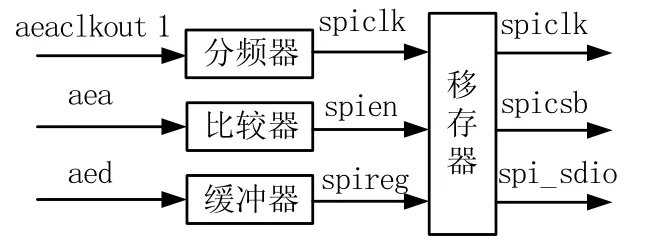

扩频中使用128位大M序列,扩频码数据速率6.4 Mc/s。为了便于之后对中频载波进行调制,我们把码速率插值到70M样本/秒,之后经过余弦滚降滤波器滤波后使用BPSK调制方式调制到中频70 MHz[2]。数据流程见图2。

图2 数据流

2 硬件接口设计

DSP访问片外存储器必须通过外部存储器接口(External Memory Interface,EMIF)。C6416的 EMIF具有很强的接口能力。C64xx提供 2个独立的 EMIF:EMIFA和EMIFB。EMIFA提供64bit宽度的外总线数据接口,EMIFB提供16bit宽度的外总线数据接口。EMIF的时钟ECLKOUTn是基于EMIF输入时钟在内部产生的。

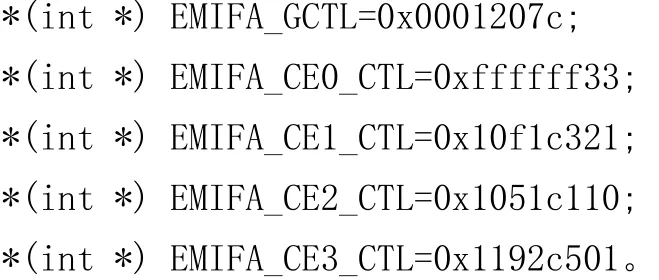

为了保证DSP与FPGA的数据传输能够稳定进行,它们之间的连接通过EMIFA实现。EMIF接口设计的一个重要问题就是根据PCB板的布线情况来调整一些重要的延时,具体控制寄存器设置如下:

接口设计中的 FPGA端要根据 EMIFA的时序图来编写FPGA的接口模块。图3为C6416与Vetrix2接口的写时序图,根据这个时序图可以编写FPGA中接口的时序:

图3 C6416与Vetrix2接口的写时序

AD9777与FPGA通信使用SPI接口。它可以支持四根信号线:时钟信号线SCLK, 使能信号CS,串行数据输入输出端口 SDIO,串行数据输出端口 SDO。其中可以只选用前三根信号线而不选用第四根SDO信号线。AD9777在SPI的通信协议的内容包括:

①SDIO的数据在SCLK的上升沿被采样;

②SDIO的数据在SCLK的下降沿被改变;

③SCLK在空闲状态下,可以为高电平也可以为低电平;

④串行传输过程中,MSB模式的时序。

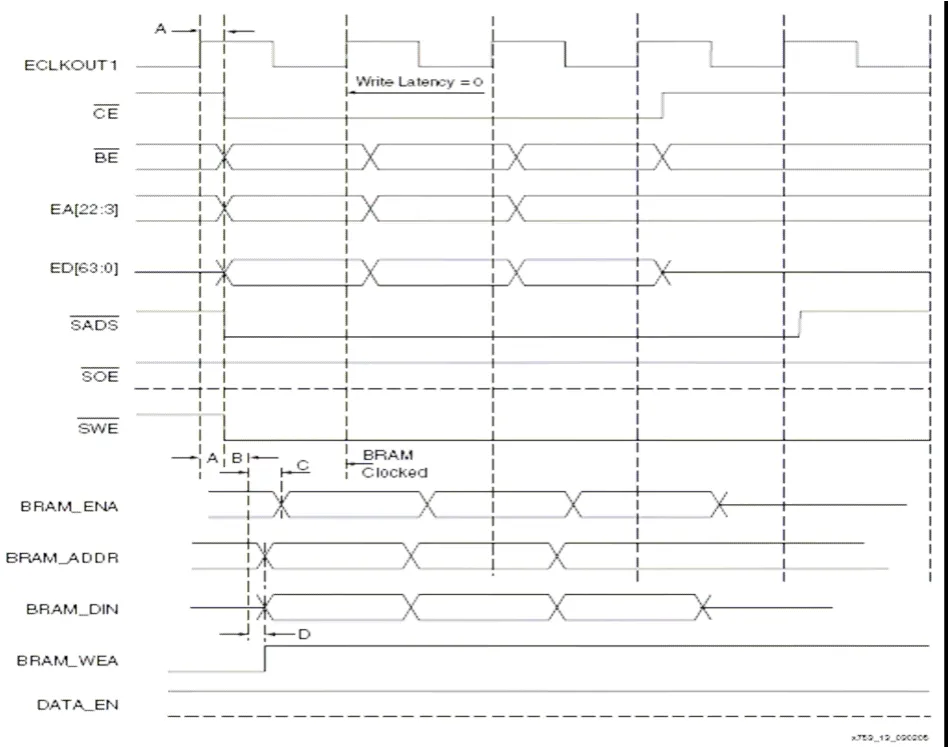

根据AD9777的串口时序图和DSP的EMIFA的端口时序设计这个模块,实现了DSP对AD9777控制参数的设置。使用EMIFA的输出时钟aeaclkout1分频产生SPI端口(见图4)使用的spiclk用于控制移存器把从DSP收到的16位宽的数据aed转换为1位宽的串行数据spi_sdio。使用EMIFA的地址输出aea控制SPI端口使能spicsb,spicsb为低电平时输出串行数据spicsb。

图4 SPI模块结构

3 软件设计

3.1 DSP控制和数据生成

DSP部分的主要功能是对用户数据扩频,控制AD9777的工作方式,其结构如图5。

图5 DSP部分功能示意

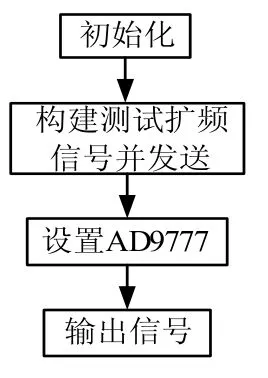

DSP部分程序有main.c,signal_gen.c。main.c的功能是产生扩频序列,同时控制AD9777调制生成BPSK信号,流程如下页图6。

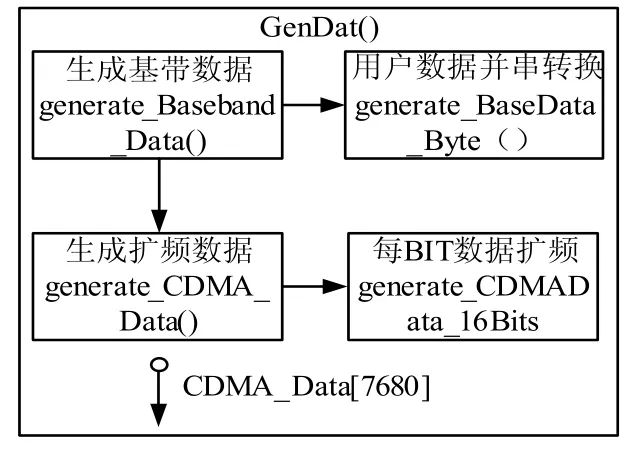

signal_gen.c的主要函数是GenDat(),功能是实现对用户数据的训练序列插入并扩频处理,程序流程如下页图7。其中函数 void generate_BaseData_Byte(unsigned char Dat , char* dp)实现把char类型的并行数据转换为bit流形式的串行数据。并且为了便于实现BPSK调制,我们使用了双相不归零码,这样与载波相乘即可完成 BPSK调制。

图6 main.c软件流程设计

图7 GenDat()内部流程

扩频时,把采用的128位M序列存贮于数组中,利用查表进行相乘直接实现扩频,扩频序列可调,性能稳定可靠。

在本系统的应用中,AD9777的输入时钟70M,数据速率70 MHz,载频70 MHz,根据芯片资料提供的最佳参数设置,我们设置PLL2倍频,进行2倍插值,fs/2调制,经过实验证明,这样的参数设置可以提供最优的信号输出。

3.2 .FPGA处理部分

本系统采用Verilog硬件描述语言,RTL级描述了系统功能。FPGA中模块的划分如图8所示。

4 设计的调试结果

图9为在Chicoscope中观测到的进入升余弦滚降滤波器之前的码型和经过升余弦滚降滤波器之后送往 AD9777的码型。经过系统的调试和使用证明这是一种成功的扩频信号发生器。

图8 FPGA内部模块

图9 Chicoscope中观测到的信号码型

5 结语

为了验证此系统的正确性与实用性,我们进行了大量的实验。我们首先在Xlinx自带调试软件Chicoscope中观测到的进入升余弦滚降滤波器之前的码型和经过升余弦滚降滤波器之后送往 AD9777的码型,其后又在在频谱仪上观测的70MHz 上经过BPSK调制的中频信号的频谱。比对观察发现信号升余弦滤波前后的码型正确,产生的中频钟型波形状标准。经过在数字多波束天线系统的接收机调试过程中的使用,证明了这是一种使用方便和发射信号灵活的试验用扩频信号发生器

[1] 王涛,彭茜,李威.基于中低速率短波扩频通信系统设计[J].通信技术,2009,42(08):39-41.

[2] 杨小牛,楼才义,徐建良.软件无线电原理与应用[M].北京:电子工业出版社,2001:208-209.

[3] Pickholtz R L,Schilling D L,Milstein L B.Theory of Spread Spectrum Communications[J].A Tutorial Special Issue of IEEE Trans.comm.,1982,30(05):45-46.