H.264/AVC编码器在TMS320DM6437上的EDMA优化*

2010-06-07崔慧娟

崔 遥,赵 锴,崔慧娟,唐 昆

(清华信息科学与技术国家实验室,北京 100084)

1 引言

TMS320DM6437(简称DM6437)数字媒体处理器是一款高性能定点数字信号处理芯片,采用第三代高性能的超长字指令(VLIM)结构,主频可达 400~700 MHz,峰值运算速率高达 3200~5600 MI/s(兆指令/秒)。DM6437芯片所特有的增强型直接内存存取(Enhanced Direct Memory Access,EDMA)数据搬移工具,可以采用乒乓缓存机制,通过配置芯片上的EDMA寄存器,实现CPU与数据搬移的并行操作,提高CPU的运行效率,而H.264/AVC[1]编码器中大量的数据搬移,正好可以利用EDMA进行优化,提高编码器的高速缓冲存储器(cache)命中率和编码速率。

2 DM6437 EDMA简介

2.1 EDMA结构和工作流程

EDMA在传输过程中完全不占用CPU资源,节省大量的时钟周期,支持片内存储区到片外,片内存储区之间和片外存储区之间的数据读写并且传输模式灵活,支持三维传输模式,可以对传输数据进行重排,大大增强代码的灵活性。

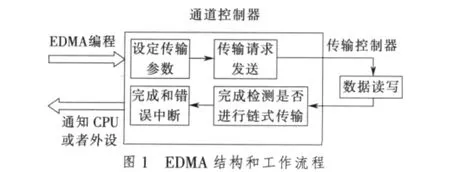

EDMA主要由EDMA通道控制器 (EDMA Channel Controller)和EDMA传输控制器 (EDMA Transfer Controller)组成,如图1所示。EDMA通道控制器主要完成数据传输前的准备工作,如申请传输通道,配置传输参数到参数寄存器(PaRAM)中,发送传输请求以及传输完成检测等工作。EDMA传输控制器主要是对EDMA通道控制器发送过来的传输请求进行处理,然后按照预先的设置,进行数据传输,具体参数配置主要是在EDMA通道控制器中完成。

2.2 EDMA传输控制器结构

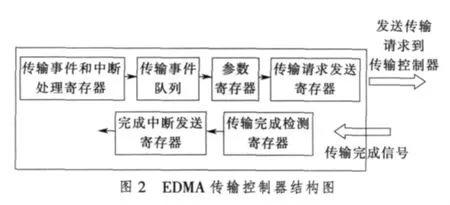

EDMA传输控制器主要包括传输事件和中断处理寄存器、传输事件队列、参数寄存器、传输请求发送寄存器和传输完成检测寄存器以及完成中断发送寄存器,结构如图2所示。传输事件和中断处理寄存器用于触发传输,传输事件队列会按照优先级对传输事件进行排序,参数寄存器用于存储传输中需要设置的参数,如源地址、目的地址、数据格式等参数,传输完成检测寄存器用于检测传输是否完成,完成后是否进行链式传输,完成中断发送寄存器用于在传输完成后向外设和CPU发送中断信号。

2.3 EDMA的传输模式

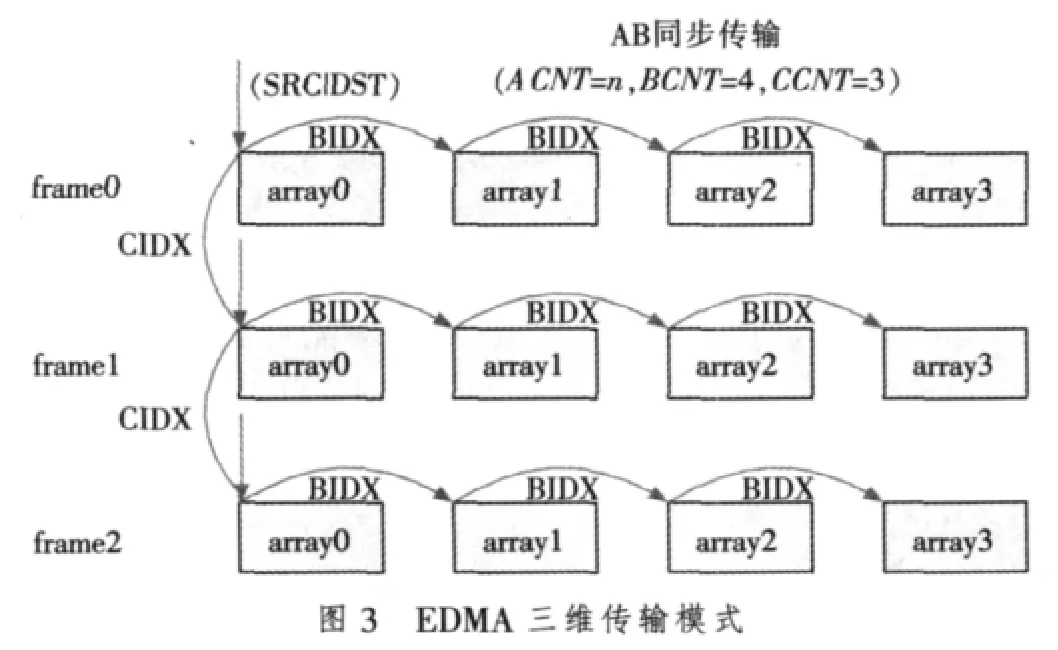

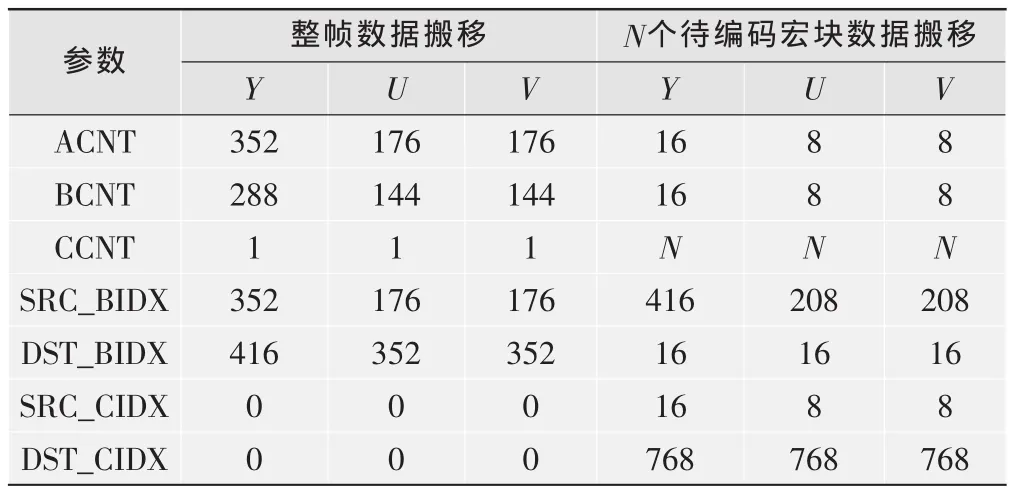

EDMA传输模式主要有2种:A同步模式和AB同步模式。A同步模式在每次传输被触发后,会传输一个array,然后会产生一个中断信号,AB同步模式每次传输一个frame,传输效率高,本文采用AB同步模式。ACNT,BCNT和CCNT分别代表三维传输数据块的尺寸大小,如图3所示,每个array由ACNT个字节组成,每个frame由BCNT个array组成,每个block由CCNT个frame组成。BIDX和CIDX分别表示第二维和第三维传输的地址自增偏移量。根据程序需要,对这几个参数进行合理的设置,可以在数据传输过程中实现数据的重排,优化数据存储结构,提高cache命中率,从而最终提高代码执行效率。

2.4 EDMA乒乓缓存机制

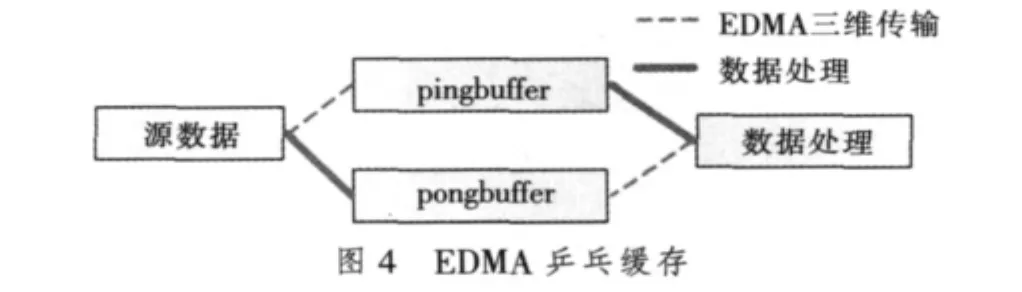

乒乓缓存机制是EDMA最重要的一种传输方式,如图4所示。该方式可以实现EDMA与CPU的并行,本文两处EDMA优化均使用该传输方式。其实现主要是将传输目的缓冲区设置为原来目的缓冲区的2倍,然后分别用pingbuffer和pongbuffer作为这2块缓冲区的指针,当EDMA向pingbuffer存储区传输数据时,编码数据指针指向pongbuffer,当pongbuffer中的数据编码完成后,pingbuffer存储区数据传输完毕,然后分别交换EDMA传输目的地址和待编码宏块的指针,即将pongbuffer缓冲区赋值给待编码宏块指针,将pingbuffer缓冲区赋值给EDMA传输的地址指针。这样2个数据通路,在一路利用EDMA传输数据的同时,另一路由CPU进行编码的数据运算。如果传输时间小于编码运算的时间,则EDMA完全独立于CPU在后台运行,不耗费一个时钟周期,因此实现了数据传输和CPU并行,提高了代码的运行效率。

3 H.264/AVC编码器EDMA优化

3.1 编码器数据存储情况

H.264/AVC编码器编码步骤如下:1)编码数据及辅助信息拷贝,主要包括两部分数据,一是待编码宏块数据从片外传输到片内,另一部分是周围重建宏块的数据信息(用于帧内预测)和编码信息(用于MV预测和熵编码等)。2)宏块分析,即根据率失真优化得到该宏块的最佳编码模式。3)宏块编码,根据分析出来的最佳编码模式,进行帧内和帧间预测,得到残差信息。4)重建编码宏块,并将当前编码宏块的辅助信息(预测模式、MV信息等)写入缓冲区(为编码临近宏块使用)。5)宏块熵编码,根据宏块编码模式和残差数据进行进一步的数据压缩。通过以上分析,在帧数据读入后进行边界扩展和编码前宏块拆分阶段,都涉及到了大数据量的搬移,因此对这两部分进行EDMA优化。

3.2 帧级EDMA优化

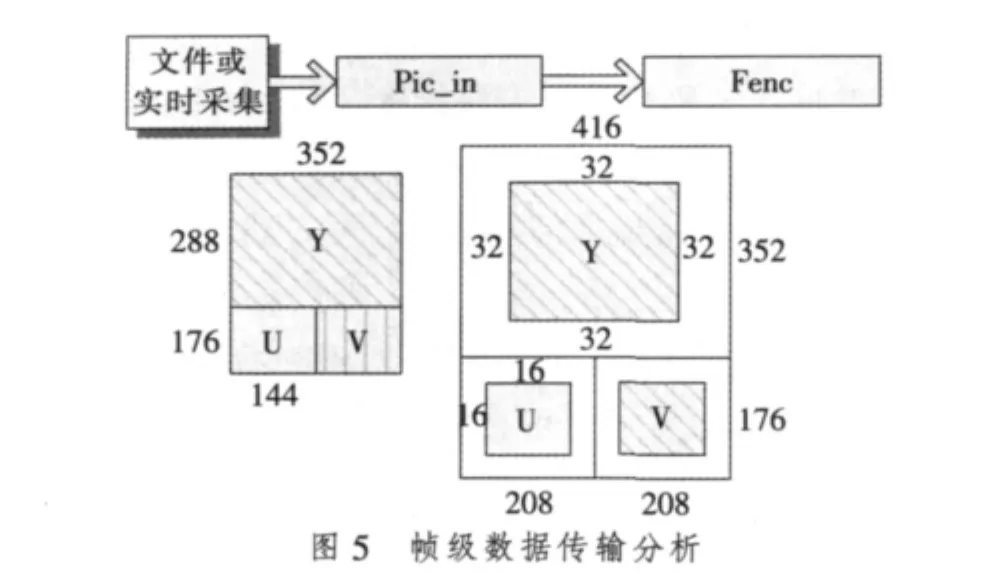

编码器在编码前,首先会读入一帧数据到片外存储区Pic_in,为提高压缩效率,支持越界搜索,对这一帧数据进行边界扩展后存储到片外存储区Fenc,如图5所示。而对帧数据进行边界扩展,需要对整帧数据进行搬移,如果采用数据拷贝指令,占用了CPU的资源,费时费力,并且由于只有一块存储区,编码器每次必须等数据传输完成后,才能进行下面的操作,由于数据量大,等待时间较长,因此这里可以使用EDMA乒乓缓存机制进行优化。

3.3 宏块级EDMA优化

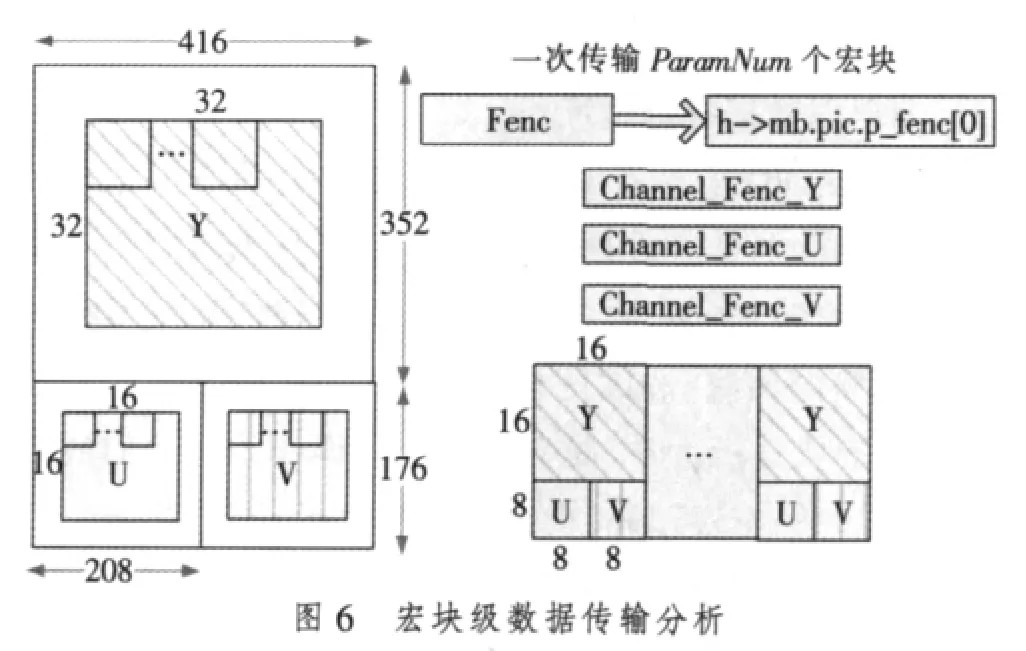

为了更好地发挥EDMA在大数据量搬移上的优势,首先对程序进行修改。修改前,编码器从片外整帧数据中读入一个宏块的数据到片内,然后进行编码,但是一个宏块的数据量较小,EDMA的优势难以得到发挥,因此对程序进行调整,编码器每次读入若干宏块,如图6所示,宏块的个数通过ParamNum来控制,增加了每次传输的数据量。因此,进行调整后的编码器,在这里也可以使用EDMA进行优化。

帧级和宏块级EDMA优化的具体参数配置如表1所示。

表1 EDMA优化配置参数

4 试验结果与分析

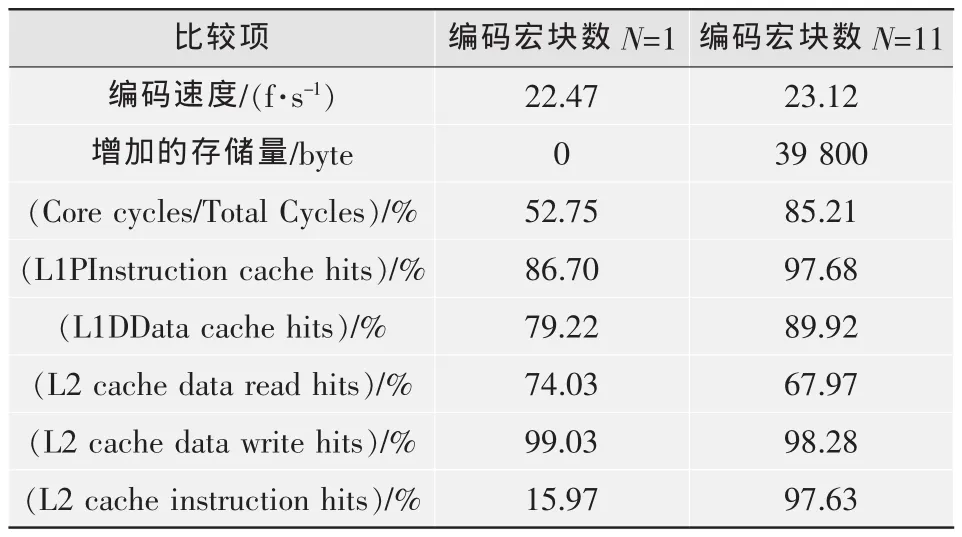

测试平台使用DM6437开发板,采用典型测试序列Foreman(),对汇编优化[2]过的x264[3]编码器 cache命中率和编码速度进行测试。根据DM6437上片内存储资源,对cache和内部RAM配置如下:L1P存储空间全部配置为cache,大小为32 kbyte;L1D存储空间64 kbyte配置为内部数据存储存储空间,16 kbyte配置为数据cache;L2存储空间128 kbyte全部配置为cache(程序cache或者数据cache)。经过多次测试,编码器编码前读入的宏块数目为11时,cache命中率得到显著提高。具体的测试结果如表2所示。

表2 cache命中率影响对比

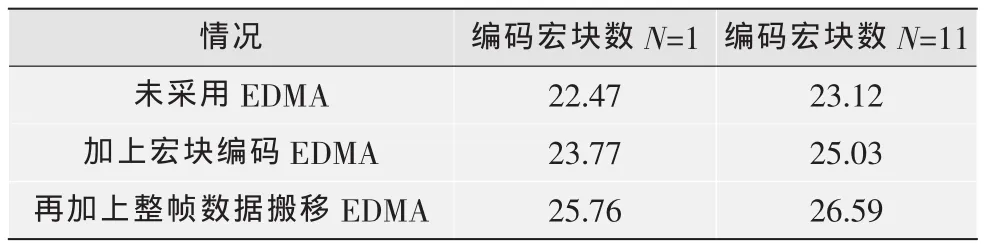

而采用EDMA优化后,编码速度也得到了改善,提高了大约3~4帧,并且一次读入11个宏块与一次读入1个宏块相比,前者采用EDMA优化的效果更为明显,如表3所示。

表3 编码速率影响对比 f/s

5 小结

通过对H.264/AVC编码器进行分析和结构调整,采用EDMA乒乓缓存机制,对编码器进行了优化,提高了cache命中率和编码速度,证明在处理大数据量的数据传输时,EDMA有其特有的优势。下一步将分析H.264解码器的存储结构和程序流程,思考如何利用EDMA进行解码器的优化,以完成实时视频通信的目标。

[1]WIEGAND T,SULLIVAN G J,BJONTEGAARD G,et al.Overview of the H.264/AVC video coding standard[J].IEEE Trans.Circuits and Systems for Video Technology,2003,13(7):560-576.

[2]彭烨.H.264/AVC编解码器在TMS320C6400上的优化实现[J].电视技术,2008,32(9):21-23.

[3]X264 Codec[EB/OL].[2010-06-01].http://www.videolan.org/developers/x264.html.