基于LDPC码的以太网数据传输编码设计

2018-12-10甄国涌焦新泉储成群

王 琦, 甄国涌, 焦新泉, 储成群

(中北大学 仪器科学与动态测试教育部重点实验室,太原 030051)

0 引 言

以太网已经成为现代社会常用的通信方式之一,成为通信界当之无愧的“宠儿”[1]。以太网通信经过了多年的发展,其传输速率已经达到万兆甚至十万兆,在如此高速率的数据传输中,光缆的传输成为了必不可少的传输媒介。在高速远距离光缆传输过程中,为了降低以太网的误码率不能单单依靠循环冗馀校验码(Cyclic Redundancey Check,CRC)校验。为了保证以太网数据传输的可靠性,本文提出低密度奇偶校验码(Low Density Parity Check Code,LDPC)的编码方式, LDPC码其灵活性较强,译码方式较为简便,译码吞吐量高,可以在编解码过程中实现纠错功能,保证数据传输可靠性[2],在以太网光缆传输中加入LDPC编解码可以有效保证其数据传输可靠性,本文主要是对以太网LDPC码的编码进行研究与实现。

1 LDPC码的选择

LDPC码的低密度特性降低了其在编解码过程的复杂度同时大大提高了其性能,其密度的高低程度成为了判断LDPC码的纠错性能的好坏以及其编译码简单程度的重要条件[3]。

LDPC码的构造具有如下几个原则:Tanner图无短环且直径尽可能小,码间距离、伪码字重量、诱捕集以及停止集不能过小[4]。LDPC码的码长确定取决于以太网在链路层的传输码字的长度。千兆以太网在PHY采用8b/10b编码的编码方式[5],因此在不经过解码后其链路层传输位数为10 bit,为了方便起见确定LDPC码信息位数为此传输位数即10 bit的整数倍。同理,因为万兆以太网编码常用编码方式为64b/66b[6],采用双通道并行结构,所以LDPC码的码长选择为33 bit的整数倍即可[7]。

本文选择准低密度奇偶校验码(Quasi-Cyclic Low-Density Parity-check,QC-LDPC)进行编码设计,QC-LDPC码称为准循环LDPC码,此类码的构造是将基础矩阵进行循环移位得到的循环矩阵[8]。而在构造基本矩阵时可以选用Gallager给出的方法进行构造。选择QC-LDPC码可以减少硬件上的工作量,大大简化硬件构成的复杂程度[9]。校验矩阵的构造如下:

(1)

式中,A为a×a子矩阵,之后将此基础矩阵作为标准进行整体循环从而构造出所需的校验矩阵[10]。根据上文选定的LDPC码的长度规则,对其进行如表1的相关设计。

本文以千兆以太网为例进行LDPC编码设计,首先对LDPC校验矩阵即H矩阵进行设计,如1表所示,千兆以太网的LDPC编码的校验矩阵H是由3×8个24×24大小的基础矩阵循环移位得到。

表1 LDPC校验矩阵设计参数

2 LDPC码编码整体架构

传统以太网在进行数据传输时,每一帧数据会首先经过一次解码发送至数据链路层,之后在数据链路层进行信道编码。为了节省时延,将以太网未经过第一次解码的数据直接进行LDPC编码,从而减少一次解码,缩短传输时间。

针对以太网LDPC编码,设计LDPC的校验矩阵H,H矩阵为LDPC编码校验矩阵,将其进行分割,分割为HS以及HP矩阵:

H=[HSHP]

(2)

(3)

式中:HS矩阵为信息位矩阵;HP为校验位矩阵。

为了方便计算将HP矩阵变换为如下矩阵[11]:

(4)

假设输出码字C=[SP]。其中:S为信息位;P为校验位。分析LDPC编码特点可知H与C具有如下关系:

H·CT=0T

(5)

根据式(5)并结合以上分析可得

(HS:HP)·(ST:PT)=0T

(6)

因此

HS·ST=HP·PT

(7)

(8)

由式(8)可知,对于校验位的计算需要求得HP的逆矩阵,但由于矩阵的逆矩阵求解过程较为复杂,在实现方面有一定的难度,同时因为LDPC码的校验矩阵为稀疏矩阵,若经过求逆之后可能会破坏其稀疏性导致计算过程变得复杂,而且会造成编码延时加长,因此,本文不选择直接求逆的方式进行计算。结合HP矩阵的特点,采用迭代的方式进行校验码的计算成为了一种较好的方式[12]。令hT=HS·ST,其检验位的计算如下式所示:

(9)

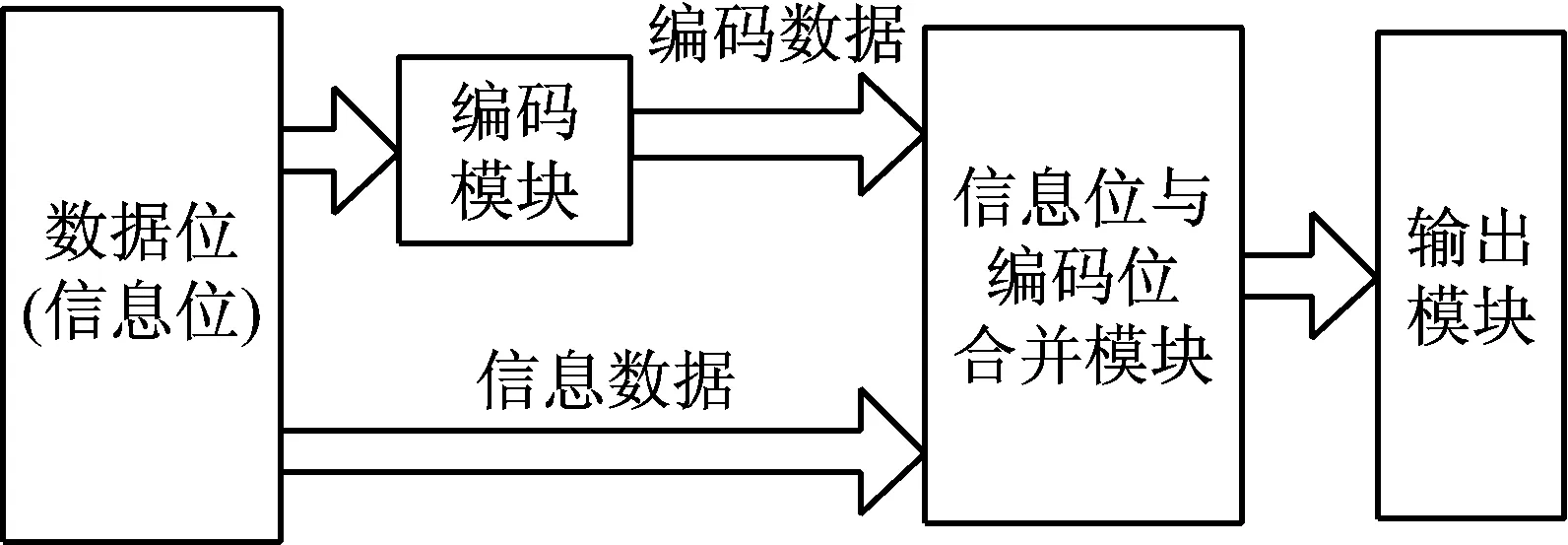

如图1所示为编码架构图,在编码过程中,传输数据10 bit并行发送至编码模块中,在LDPC编码模块中进行编码计算,之后根据编码输出要求输出信息位以及校验位[13]。

图1 编码架构

3 LDPC码编码的FPGA实现

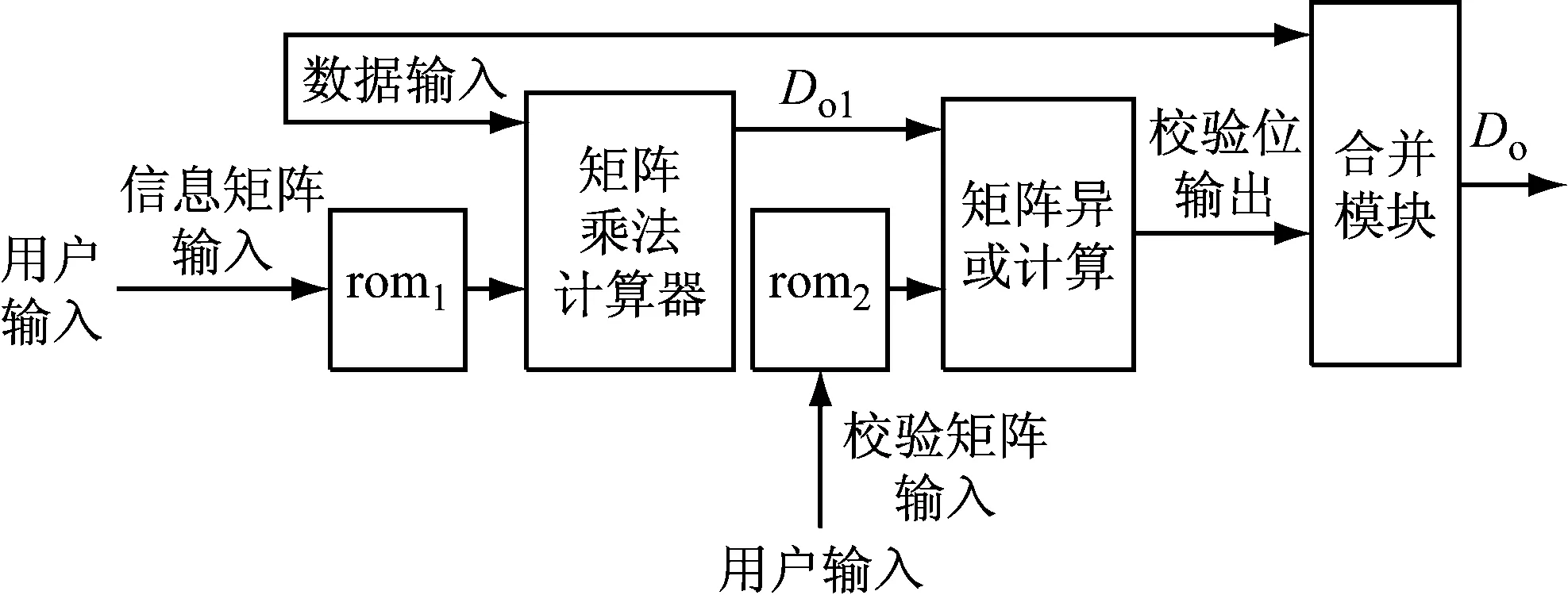

根据上文对LDPC编码算法的研究与分析可知,LDPC编码基于的FPGA实现,其重点在于矩阵乘法和异或运算的实现,图2所示为FPGA实现LDPC编码的整体设计方案。

图2 LDPC编码整体设计方案

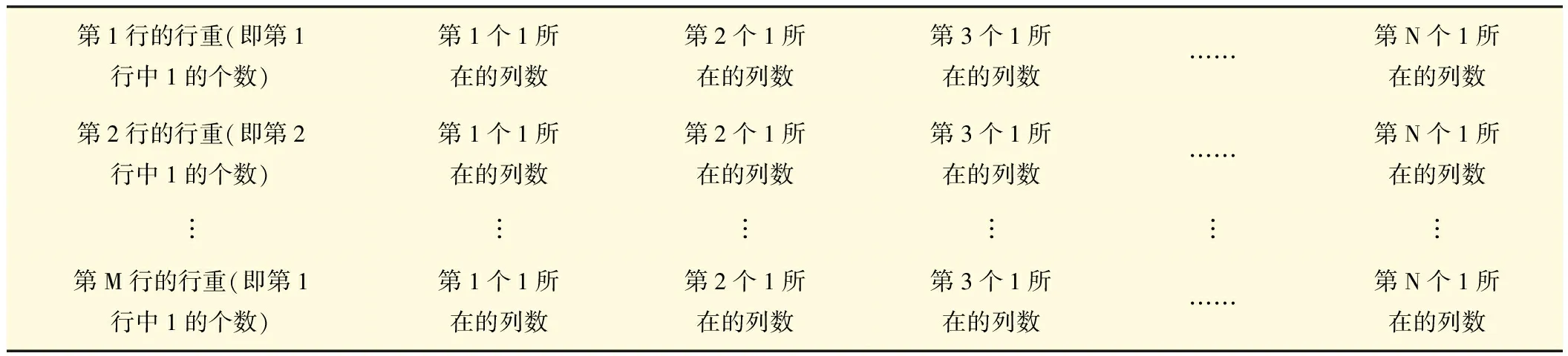

由图2可见,首先信息位与信息矩阵进行矩阵乘法计算得到中间输出值Do1,之后Do1与校验矩阵进行异或计算得到校验位,最后输出编码结果Do。整套设计方案的核心主要是矩阵乘法的计算,对二进制矩阵的乘法进行FPGA的设计,其具体思路如下:对矩阵HS进行行扫描,扫描每一行中‘1’的位置,同时对矩阵S进行相同的扫描。比较矩阵HS中每一行中‘1’的位置与矩阵S中‘1’的位置,当两个矩阵中‘1’的位置相同时计数加‘1’,直到HS单行扫描完成,如果计数为奇数,则输出值为‘1’;反之则为‘0’。对矩阵HS的每一行都进行如上所述的步骤,最终输出中间值Do1,至此矩阵乘法的运算即可结束。同理,矩阵的异或计算可以采用相类似的算法。基于LDPC码的特点,其校验矩阵中‘1’的数量远远小于‘0’的数量,这就大大简化了矩阵的运算过程[14-15]。为了进一步优化,在HS的存储方法上可以采用不同的方式。因为在矩阵乘法的计算过程中,关注点在于‘1’的数量及位置,因此可以规定矩阵存储的规则,在进行矩阵存储时只存储此矩阵的行重以及其‘1’的位置。如表2所示为矩阵存储表,即为本文采用的矩阵存储方式[16]。

表2 矩阵存储表

4 LDPC码编码仿真结果

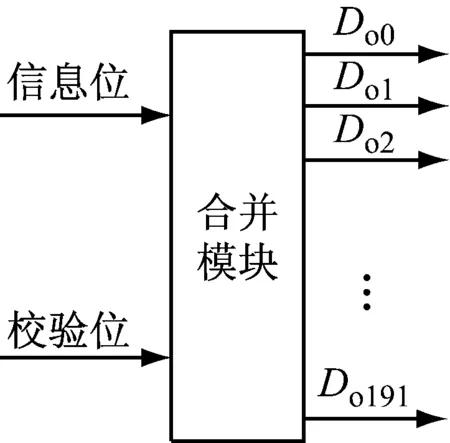

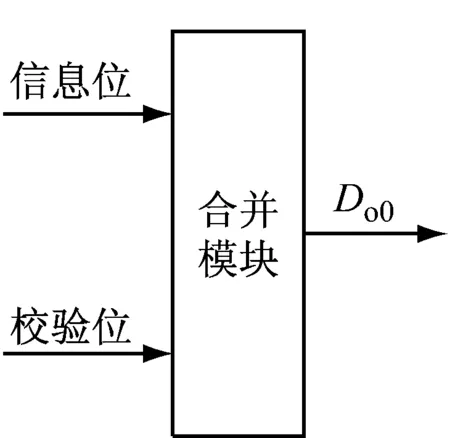

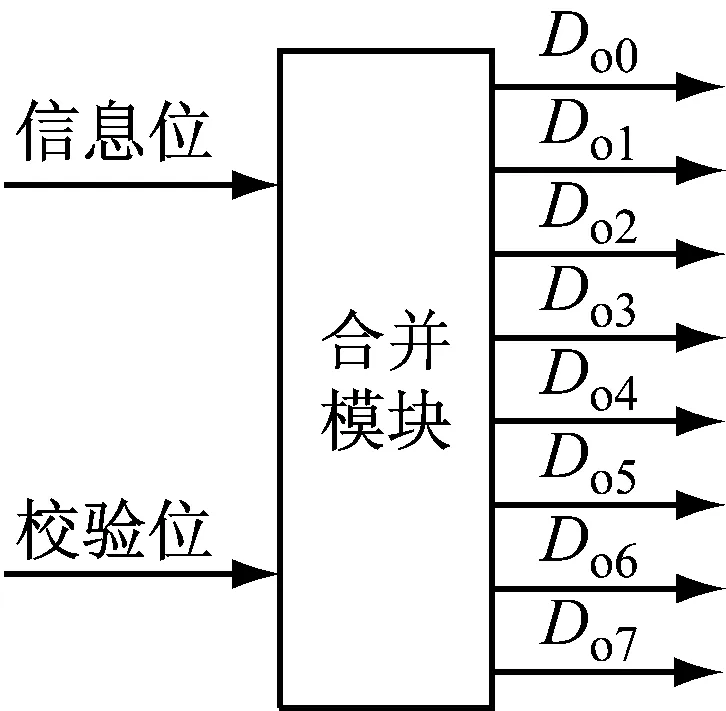

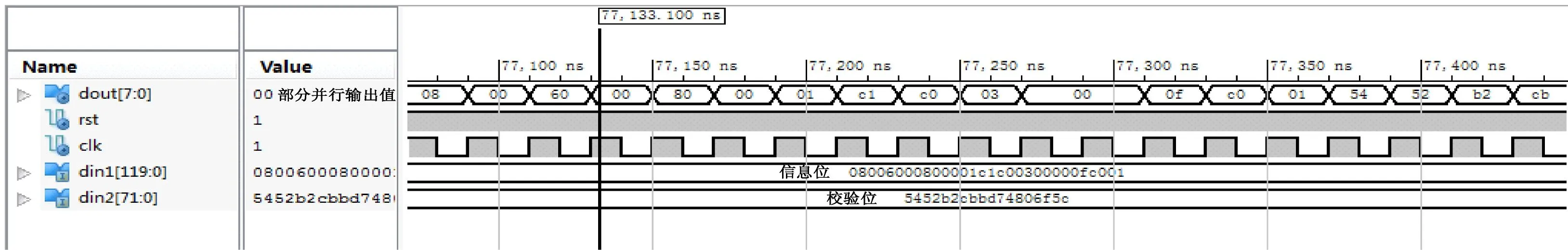

根据以上分析对其进行编码仿真分析,在输出端口拟采用3种输出方式,第1种方式是以完全并行的方式直接进行输出,这种做法可以提高传输速度但是其I/O口资源占有率大大增加,一般情况下FPGA可用I/O口远远小于其占有I/O口数量,因此此方案无法在实际中应用;第2种方式采用完全串行的方式进行输出,这种方案可以大大减小I/O口的占用率,但是会使得编码速度变慢;最后一种方式是采用部分并行的方式进行输出,既可以将输出以8位并行的方式进行输出,这种方案既可以在一定程度上提高编码速度,同时I/O口资源占有率也不会特别高,还可以根据实际情况对并行位数进行调整。如图3所示为3种不同输出模式,如图4所示为LDPC编码仿真结果。

如图3所示,为不同的输出模式,其中(a)(b)(c)分别为3种模式的输出方式。图4所示为LDPC编码结果输出图,其中(a)(b)(c)分别为3种不同输出方式的输出结果。如图所示信息位为以太网输出的120 bit的信息数据,校验位为经过LDPC编码后输出的72位校验数据,最终输出值Dout为编码后码字的输出值。对上述3种不同的编码输出方式的资源占用率进行分析。

(a) 完全并行输出模式

(b) 完全串行输出模式

(c) 部分并行输出模式

图3 3种不同输出模式

(a) 完全并行输出模式

(c) 部分并行输出

图4 LDPC编码结果图

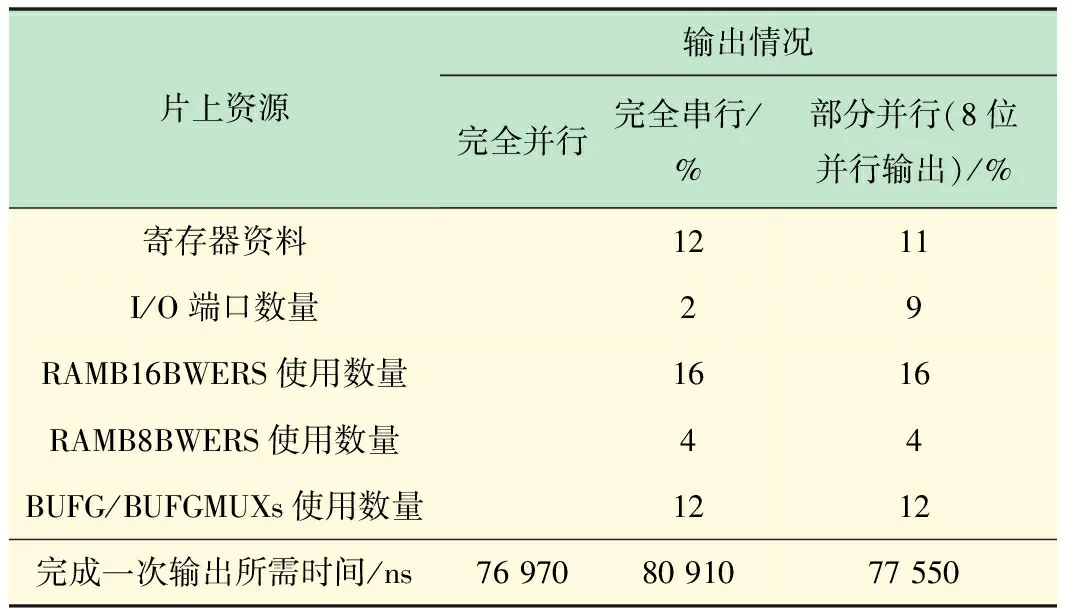

表3所示为资源利用情况以及运行速度情况,其中运行速度即完成一次输出所需的时间,其与校验矩阵的构造有很大关系。由表3可知,完全并行的输出方式由于I/O口资源不够,因此无法在实际中应用,但根据仿真结果可分析其运行速度,其完成一次输出所需时间为76 970 ns,是3种输出方式中速率最快的一种。对其余两种方式进行对比,可以看到资源利用方面两种方式只是在I/O口占用率方面差别较大,在运行速度方面,采用部分并行的输出方式要比完全串行的输出方式快。综合以上资源利用率以及运行速度情况,在I/O口资源足够的情况下采用部分并行的方式进行输出可以提高传输速率,达到最好的效果。

表3 资源利用率

5 结 语

本文根据以太网数据传输方式实现了LDPC的(192,120)编码同时分析对比了完全串行输出,完全并行输出以及部分并行输出的3种编码输出模式的资源占用率以及运行速度,发现部分并行的方式进行编码输出可以达到性能最优。