一种三层EPI结构SGT MOSFET设计

2023-12-04商世广郭雄雄王洋菲

商世广,郭雄雄,张 雨,王洋菲,俱 帅

(1.西安邮电大学 电子工程学院,陕西 西安 710121;2.上海维安半导体有限公司,上海 201207)

金属氧化物半导体场效应晶体管(Metal-Oxide-Semiconductor Field-Effect Transistor,MOSFET)是一种常用的电子器件。在传统沟槽型MOSFET(Trench MOSFET)的基础上,屏蔽栅沟槽MOSFET(Shielded Gate Trench MOSFET,SGT MOSFET)在栅极Gate下方添加了一个接源极或地的埋层场板,即屏蔽栅,利用屏蔽栅通过电荷耦合效应对N-漂移区进行辅助耗尽,优化了器件内部的纵向电场分布,降低了纵向电场的峰值,提高了器件的击穿电压[1-3]。在耐压能力相同的情况下,与Trench MOSFET相比,SGT MOSFET增加了外延层的掺杂浓度,降低了正向导通时器件的导通电阻[4-5]。另外,由于屏蔽栅的静电屏蔽作用,减少了栅极和漏极之间的交叠面积,有效地降低了栅漏电容,从而降低了器件的开关损耗,提高了SGT MOSFET的开关速度[6]。与传统沟槽型MOSFET相比,SGT MOSFET是一种开关速度快[7]、频率特性好[8]、开关损耗低[9],具有较好电学性能的MOSFET[10]。

近年来,60 V SGT MOSFET由于在消费级电子、电源管理芯片和服务器等领域已经得到广泛应用且市场份额不断增大[11]。随着应用领域的不断扩展,不同需求对SGT MOSFET性能的要求也越来越高,导致器件的研究朝着高耐压[12]、低导通[13]和低开关损耗[14]等方向发展。在SGT MOSFET结构中,外延(Epitaxy,EPI)层对器件的性能影响较大,一方面是在流片过程中,外延层可以使得器件表面平整,减少了衬底自有的缺陷;另一方面,在SGT MOSFET中,外延层由于掺杂浓度较低,屏蔽栅在漂移区产生电荷耦合效应,能够获得较高的耐压性能[15]。

为了进一步提升SGT MOSFET的电学性能,文献[16]提出一种多层外延漂移区SGT,该研究指出,纵向电场峰值的个数与外延层数有关,通过提高SGT漂移区中部电场,能够获得更高的耐压性能。文献[17]基于150 V和200 V的SGT MOSFET,通过仿真比较两层EPISGT MOSFET和三层EPI结构SGT MOSFET进一步降低比导通电阻效果,结果发现,三层EPI结构在电学性能方面优于双层EPI。但是,现有的方法只是单一地改变了外延层的电阻率和厚度,未能一起进行拉偏仿真,无法获得更优的外延层电阻率和厚度的组合方式。关于如何提高SGT MOSFET的耐压能力和降低比导通电阻的研究还有待进一步深入。

为了提高SGT MOSFET的耐压能力和降低比导通电阻,结合文献[17]中三层EPI结构在电学性能方面优于双层EPI的研究结果,拟设计一种三层EPI结构的60 V SGT MOSFET。该设计基于单层EPI结构,通过改变外延层厚度和电阻率来改变N-漂移区耗尽层的横向电场,以提高漂移区掺杂浓度以及优化纵向峰值电场,并在提高SGT MOSFET的耐压能力的同时,降低比导通电阻。

1 SGT MOSFET的结构与工作原理

常见的上下结构N沟道SGT MOSFET的基本结构示意图及电场分布情况如图1所示。

图1 SGT MOSFET结构和电场分布示意图

图1中,图1(a)为N沟道SGT MOSFET结构原理图。传统的Trench MOSFET采用刻蚀深沟槽和生长栅氧化层,沉积单层多晶硅作为控制栅的制备工艺。SGT MOSFET利用刻蚀深沟槽和生长厚氧化层,沉积多晶硅并回刻蚀形成屏蔽栅的制作工艺,在此基础上,将再沉积隔离氧化层,沉积多晶硅再次回刻作为控制栅。SGT MOSFET与Trench MOSFET有相似的工作原理,都是通过栅极施加电压来控制纵向沟道的开启。当SGT MOSFET处于反向耐压时,相比传统的Trench MOSFET,在漂移区的沟槽拐角处还存在一个峰值电场,假设P体区和N-漂移区的纵向电场可以近似为单边突变结,理想情况下的Y方向上纵向电场如图1(b)曲线I所示呈矩形纵向电场,在P体区和N-漂移区的边界上到达临界电场Ec。在实际器件仿真过程中,漂移区中部电场为低谷区,纵向电场出现两个峰值呈哑铃状分布,如图1(b)曲线II所示,SGT MOSFET的耐压能力比理想器件明显降低。漂移区内X方向上横向电场如图1(c)所示呈线性分布。

2 结构参数设计与仿真

2.1 初始化元胞结构参数

SGT MOSFET典型的静态特性仿真参数,主要包括漏源击穿电压(Drain-Source Breakdown Voltage,BVDSS)、比导通电阻Ronsp和阈值电压Vth等,并引入了品质因数(Figure of Merit,FOM)[13]来衡量器件的性能。根据半导体物理相关知识的计算和器件设计经验,初步设计60 V单层EPI结构SGT MOSFET的工艺参数如表1所示。

表1 60 V单层EPI结构SGT MOSFET工艺参数

2.2 器件结构仿真

结合SGT MOSFET的结构原理和工艺标准参数条件,使用Sentaurus TCAD软件对器件结构进行初步仿真,单层EPI结构SGT MOSFET仿真结果如图2所示。从图中可以看出,相较于经典Trench MOSFET结构,单层EPI结构的SGT MOSFET结构中,在栅极下方添加了一个屏蔽栅结构来辅助耗尽漂移区。

图2 单层EPI结构SGT MOSFET仿真结果

3 单层EPI结构SGT MOSFET性能

3.1 外延层厚度

外延层厚度直接影响器件的击穿电压和比导通电阻,故选用合适的外延层厚度尤为重要。根据SGT MOSFET的工艺标准条件,使用Sentaurus TCAD软件对器件的外延层厚度Tepi进行上下拉偏仿真,仿真结果如表2所示。由表2可以看出,外延层厚度对阈值电压的影响较小,对击穿电压和比导通电阻的影响较为明显。

表2 单层SGT MOSFET外延层厚度拉偏仿真结果

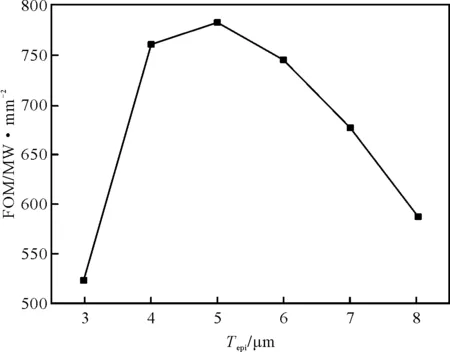

图3为单层EPI结构SGT MOSFET击穿电压BVDSS和比导通电阻Ronsp随外延层厚度的变化的仿真结果。图4为单层EPI结构SGT MOSFET品质因数FOM随外延层厚度变化的仿真结果。从图3中可以看出,当外延层厚度从3 μm增加到5 μm时,击穿电压会迅速增大;当外延层大于5 μm时,击穿电压基本稳定在一个恒定值附近。当增加外延层厚度时,会引起漂移区电阻的增加,比导通电阻也随之增加,这种增加类似于线性增加。图4表明,当外延层厚度为5 μm时,器件的品质因数FOM达到最大,为783.2 MW·mm-2。

图3 BVDSS、Ronsp随外延层厚度的变化的仿真结果

图4 FOM随外延层厚度的变化结果

图5为单层EPI结构SGT MOSFET不同外延层厚度下的纵向电场分布的仿真结果。由图中可以看出,当外延层厚度较小时,沟槽会深入到衬底区域,空间电荷区止于衬底附近,使得耗尽层变窄,击穿电压较小。当外延层厚度小于5 μm且逐渐增大时,由于衬底杂质外扩的原因,沟槽底部的杂质浓度逐渐减小,在此处形成的空间电荷区与衬底之间的距离逐渐增大,耗尽层逐渐展宽,击穿电压增大。当外延层厚度大于5 μm时,外延层耗尽线固定于沟槽底部处,沟槽下方未耗尽的外延层电场强度为0,耗尽层会稳定在一个位置附近,不随外延层的厚度的增大而展宽,此时,器件内部的纵向电场也不会发生变化,器件的击穿电压也稳定不变。

图5 不同外延层厚度下的纵向电场分布仿真结果

3.2 外延层电阻率

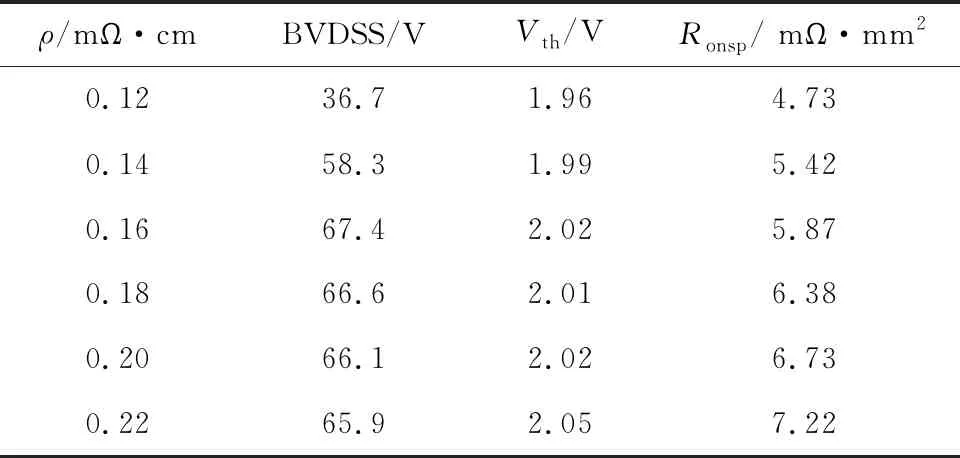

对于中低压SGT MOSFET而言,由于沟道电阻与N-漂移区电阻占总电阻的绝大部分,并且,随着器件的击穿电压增大,漂移区电阻占比也随之增大,因此,在满足耐压的情况下外延层电阻率的设计选择尤为重要。使用Sentaurus TCAD工具对器件的外延层电阻率ρ进行仿真,单层EPI结构SGT MOSFET外延层电阻率拉偏的仿真结果如表3所示。从表中可以看出,外延层电阻率对阈值电压的影响较小,对击穿电压和比导通电阻的影响较为明显。

表3 外延层电阻率拉偏的仿真结果

图6为单层EPI结构SGT MOSFET击穿电压BVDSS和比导通电阻Ronsp随外延层电阻率变化的仿真结果。从图中可以看出,当外延层电阻率在0.12 mΩ·cm~0.16 mΩ·cm范围内时,击穿电压BVDSS随电阻率的增加逐渐增大;当外延层电阻率在0.1 6 mΩ·cm~0.22 mΩ·cm范围内时,击穿电压随着电阻率的增加而略微减小。比导通电阻随着外延层电阻率的增加线性增加。

图6 BVDSS、Ronsp随外延层电阻率变化的仿真结果

图7为单层EPI结构SGT MOSFET品质因数FOM随外延层电阻率变化的仿真结果。由图中可以看出,当外延层电阻率为0.16 mΩ·cm时,器件的品质因数FOM达到最大为783.9 MW·mm-2。

图7 FOM随外延层电阻率变化的仿真结果

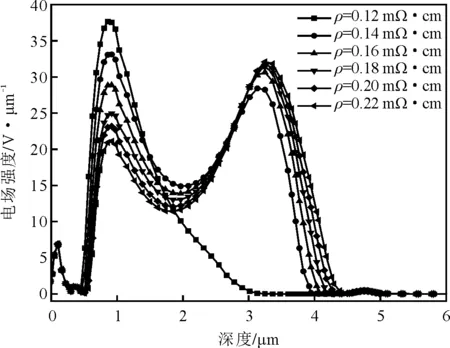

图8为单层EPI结构SGT MOSFET不同外延层电阻率下的纵向电场分布仿真结果。从图中可以看出,在一定范围内增加外延层电阻率,会导致纵向电场在P体区和N-漂移区界面处强度逐渐减小,在沟槽底部处强度逐渐增大。当外延层电阻率很小时,外延层掺杂浓度很大,N-漂移区耗尽层宽度很窄,纵向电场强度较高,SGT MOSFET击穿电压相对较低。当外延层的电阻率小于0.16 mΩ·cm时,增大外延层的电阻率,降低外延层掺杂浓度,N-漂移区耗尽层会展宽,从而降低纵向电场强度,击穿电压逐渐增大。当外延层电阻率增加到某一特定范围值时,屏蔽栅的补偿作用处于一个欠补偿与过补偿的动态平衡状态,表面电场峰值引起的电场面积减少变化量与沟槽底部耗尽层展宽的电场面积增加变化量之间达到平衡,此时,击穿电压相对稳定。若继续增加外延层电阻率,则会引起漂移区电阻的增加,引起比导通电阻也随之增加。这种增加类似于线性增加。

图8 不同外延层电阻率下的纵向电场分布仿真结果

4 三层EPI结构SGT MOSFET性能

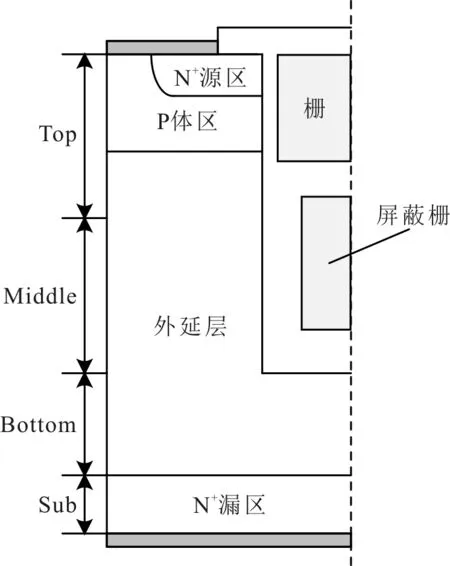

为了优化击穿电压和比导通电阻,将单层EPI结构划分为三层EPI结构,从上到下对应为Top层、Middle层和Bottom层,其结构示意图如图9所示。

图9 三层EPI SGT MOSFET结构示意图

4.1 三层EPI厚度仿真

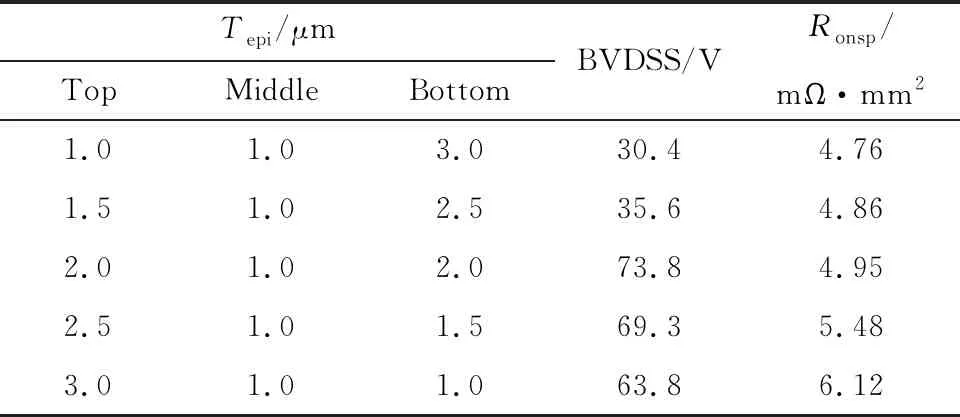

根据单层EPI结构SGT MOSFET外延层厚度拉偏结果可知,在满足60 V耐压的条件下,外延层厚度应选用5 μm最为合适。结合设计经验和外延层电阻率拉偏结果可以得出每层EPI的电阻率,其中Top层电阻率为0.18 mΩ·cm,Middle层电阻率为0.1 mΩ·cm,Bottom层电阻率为0.16 mΩ·cm。固定Middle层厚度为1 μm,对Top层和Bottom层厚度进行拉偏仿真。三层EPI结构SGT MOSFET外延层厚度拉偏结果如表4所示。从表中可以看出,当器件的Middle层EPI保持不变时,随着器件的Top层EPI厚度的增大或Bottom层EPI厚度的减小,器件的击穿电压先逐渐增大后逐渐减小。Top层EPI厚度为Middle层EPI的2倍时,器件的击穿电压最大。

表4 三层EPI结构SGT MOSFET外延层厚度拉偏结果

图10为三层EPI结构SGT MOSFET的品质因数FOM随Top层EPI厚度变化的仿真结果。从图中可以看出,当Top层EPI厚度为2 μm时,对应的Middle层与Bottom层EPI厚度分别为1 μm和2 μm,此时,器件的品质因数FOM达到最大,为1 098 MW·mm-2。

图10 FOM随TOP层EPI厚度变化的仿真结果

固定Top层电阻率为0.18 mΩ·cm,Middle层电阻率为0.1 mΩ·cm,Bottom层电阻率为0.16 mΩ·cm,Middle层厚度为1 μm,对Top层和Bottom层厚度进行拉偏仿真,三层EPI不同厚度下的纵向电场分布仿真结果如图11所示。从图中可以看出,当Top层EPI厚度增大,或Bottom层EPI厚度减小时,P体区和N-漂移区界面处电场强度逐渐增大,沟槽底部处的电场强度逐渐减小。当Top层EPI厚度为Middle层EPI的2倍时,低电阻率的Middle层能够明显地提升漂移区中部的纵向电场。由于Middle层电阻率较小,此区域引入的横向电场较大,电荷耦合作用增强,在Middle层产生了一个新的纵向电场峰值,提高了器件的击穿电压。当Top层EPI厚度较大或较小时,Middle层所产生的峰值电场靠近表面电场或沟槽底部电场,在纵向电场的分布图中表现不明显。

图11 不同三层EPI厚度下的纵向电场分布仿真结果

4.2 三层EPI电阻率仿真

综合上述实验,可以得到在最佳的击穿电压和比导通电阻情况下的三层EPI的厚度,其中Top层为2 μm,Middle层为1 μm,Bottom层为2 μm。固定Middle层EPI电阻率为0.1 mΩ·cm,对Top层和Bottom层EPI电阻率分别做拉偏仿真,三层EPI结构SGT MOSFET外延层电阻率拉偏结果如表5所示。从表中可以看出,当Top层电阻率为0.18 mΩ·cm、Middle层电阻率为0.1 mΩ·cm和Bottom层电阻率为0.16 mΩ·cm时,器件的击穿电压达到最大。当Top层EPI电阻率为0.18 mΩ·cm时,随着Bottom层EPI电阻率的增大,击穿电压略微增大;当Bottom层EPI电阻率为0.18 mΩ·cm时,随着Top层EPI电阻率的增大,击穿电压逐渐增大。

表5 三层EPI结构外延层电阻率拉偏结果

图12为三层EPI结构SGT MOSFET的品质因数FOM随Top层或Bottom层EPI电阻率变化的仿真结果。从图中可以看出,当Top层EPI电阻率为0.18 mΩ·cm,Middle层EPI电阻率为0.1 mΩ·cm,Bottom层EPI电阻率为0.16 mΩ·cm时,器件的品质因数FOM达到最大为1 098 MW·mm-2。

图12 FOM随三层EPI电阻率变化的仿真结果

固定Top层为2 μm,Middle层为1 μm,Bottom层为2 μm,Middle层EPI电阻率为0.1 mΩ·cm,对Top层和Bottom层EPI电阻率进行仿真,不同三层EPI电阻率下的纵向电场分布仿真结果如图13所示。

图13 不同三层EPI电阻率下的纵向电场分布仿真结果

从图13(a)中可以看出,当Top层的电阻率为0.18 mΩ·cm时,随着Bottom层的电阻率增大,横向电场作用增强,此时屏蔽栅补偿效果相对增强;另外,沟槽底部表面电场变大,耗尽层略微展宽,沟槽底部的纵向电场峰值逐渐增大,击穿电压略微增大。从图13(b)中可以看出,当Bottom层的电阻率为0.18 mΩ·cm时,随着Top层的电阻率减小,器件表面的纵向电场峰值逐渐增大,沟槽底部纵向电场峰值迅速减小。主要因为Top层的杂质浓度增加,耗尽层宽度会变窄,漂移区不会夹断,屏蔽栅补偿效果相对减弱,引入的横向电场作用减弱或消失,器件可能会在P体区发生提前击穿。

4.3 三层与单层EPI结构的耐压特性

图14为三层与单层EPI结构SGT MOSFET的纵向电场分布仿真结果。由图中可以得出,相比单层EPI结构SGT MOSFET,三层EPI结构SGT MOSFET在N-漂移区的纵向电场强度明显提高,N-漂移区因为Middle层为重掺杂层,屏蔽栅电荷耦合产生横向电场较高,导致纵向电场由哑铃状趋向矩形,使击穿电压提高9.5%;在Bottom层适度掺杂较容易形成载流子的堆积层,比导通电阻降低15.6%。

图14 单层与三层EPI结构的纵向电场分布仿真结果

5 结语

提出了一种三层EPI结构SGT MOSFET的设计方案。基于单层EPI结构,拉偏仿真60 V N沟道SGT MOSFET。将单层EPI结构分为Top层、Middle层和Bottom层,分别采用高、低和中的电阻率,即相对杂质浓度为轻掺杂、重掺杂和适度掺杂。仿真结果表明,在所设计的三层EPI结构SGT MOSFET中,Top层的EPI拥有较大的电阻率来维持击穿电压,Middle层的EPI选用较小的电阻率来调制纵向电场,Bottom层的EPI选用合适的电阻率,在保证其耐压的情况下,降低比导通电阻。除此之外,设计的三层EPI结构SGT MOSFET拥有更大的灵活性来调整外延层电阻率和外延层厚度,在保证耐压足够的情况下,可以进一步降低比导通电阻。