学科竞赛与课程设计有机融合的计算机组成原理实验教学探索

2023-07-16樊彦恩张俊霞

樊彦恩,张俊霞

(中国科学技术大学 计算机科学与技术学院,安徽 合肥 230026)

0 引言

信息和通信技术的飞速发展,对计算机专业人才的综合素质、竞争能力和创新能力的要求越来越高。为推动我国计算机领域创新人才培养,为我国高端芯片及核心系统的技术突破与产业化培养后备人才,教育部高等学校计算机类专业教学指导委员会(简称“计算机类教指委”)和系统能力培养专家组共同发起 “全国大学生计算机系统能力培养大赛”。大赛以赛促学、以赛促教,助力我国高校与企业产学研合作的健康、快速发展。其中,“龙芯杯”作为该赛事的CPU赛道(以下简称CPU设计大赛),以计算机系统设计、分析、优化、应用为目标,涉及到计算机系统结构中的CPU、操作系统和编译器3个方向的知识,重点培养学生的系统观、创新力、工程实践能力和团队协作精神。

计算机组成原理作为计算机专业最重要的核心基础课之一,其教学内容是软件与硬件的结合,不仅涉及计算机系统结构中下层的数字逻辑电路设计和指令系统,还涉及到上层的操作系统和编译程序等软件技术,在整个计算机专业教学中起着承上启下的作用[1-2]。该课程对于学生完整理解计算机系统的层次结构,系统地建立计算机整机概念,具有非常重要的作用。

近年来,在全国计算机教学指导委员会的指导和推动下,各高校都在进行计算机系统能力培养的教学改革[3-5]。其中,针对计算机组成原理实验课程教学改革的研究与探讨工作也在不断发展和完善中。北京工业大学教学硬件课程组分析并梳理了计算机类竞赛典型参赛作品中涉及到的各种硬件知识点,在计算机组成原理这一核心课程上,借鉴了竞赛的CPU架构,增加了一些典型外设的连接任务等内容[6]。针对计算机组成原理实验课程特点,成都大学提出将科技竞赛与其融合,通过建立具有科技竞赛背景的教师团队进行教学改革[7]。硬件实验平台对于计算机组成原理的实验课程教学具有重要意义。合肥工业大学教学课题组通过分析安徽省系统能力培养竞赛题目和成绩,以及对部分院校计算机组成原理实验平台的调查,提出以ModelSim为主要实验平台,以仿真为主的轻量级实验体系[8]。南京邮电大学和北京科技大学通过引入龙芯开源 CPU的教学实验平台,开展了一系列教学改革尝试[9-10]。综上所述,各高校对计算机组成原理实验课程的教学改革主要集中在实验平台、教学方法以及硬件外设应用方面,并取得了预期成效[11-12]。然而,鲜有教改在实验内容中增设软件技术和CPU功能调试技术,这两方面内容对于学生建立系统观和锻炼工程实践能力非常有帮助。在计算机组成原理实验的考核方面,目前的主流方式是实验检查,将实验报告与平时成绩相结合。在实验检查时,由于助教的知识水平和评判标准差异,给出的分数带有一定的主观性,并且区分度较小。因此,对实验结果进行科学、有效的量化显得尤为重要。

中国科学技术大学计算机科学与技术系春季学期开设的计算机组成原理实验课程要求学生在FPGA开发板上设计出一个最小计算机硬件系统。其核心是针对给定的RISC-V指令系统,采用硬件描述语言Verilog HDL,在FPGA芯片上设计出拥有完整CPU架构的片上系统(System on Chip,SoC)。为了进一步培养学生的计算机结构系统观和工程实践能力,课题组将CPU设计大赛中涉及到的计算机系统硬件、软件知识点以及CPU功能调试技术,经过研究、裁剪和融合,渗透到计算机组成原理实验教学内容中,将在CPU设计大赛中采用的系统测试方法和评分标准应用到实践教学中,更新和扩充教学内容,将竞赛与教学进行有机结合,切实提高实验教学质量。

1 实验课程知识储备

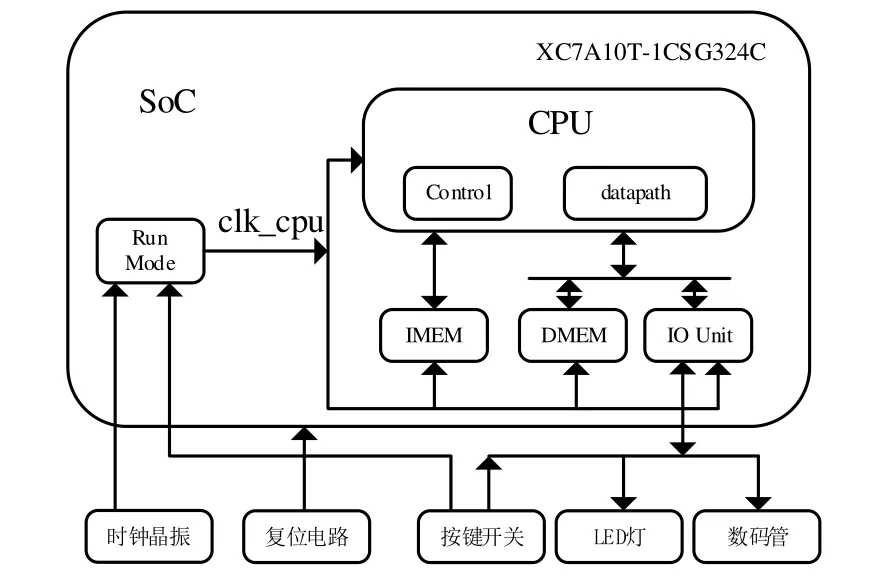

计算机组成原理实验课程旨在利用电子设计自动化技术(Electronic Design Automation,EDA),在FPGA开发板(Nexys4 DDR)上构建一个能正确工作的最小计算机硬件系统,如图1所示。该最小计算机硬件系统由拥有完整CPU架构的SoC芯片及其外设接口设备组成。其中,开关和按键控制Run Mode模块输出时钟信号clk_cpu,控制CPU工作在单步调试模式或连续运行模式;CPU通过访问IO Unit模块管理外设,如驱动开发板上的LED灯、数码管,并接收外部开关、按键的输入等。在数字电路理论和实验课程中,学生已经掌握在Vivado集成环境下,采用Verilog HDL语言在FPGA芯片上进行数字逻辑单元设计和简单的数字系统设计。其次,在计算机组成原理理论课程中,学生深入学习了RISC-V指令系统,以及单周期、多周期和流水线CPU数据通路设计。计算机组成原理实验课程建立在此基础上,从设计CPU部件级电路开始,逐步完成RISC-V体系结构的完整CPU设计。

Fig.1 Schematic diagram of minimum computer hardware system图1 最小计算机硬件系统原理

2 实验课程内容设置

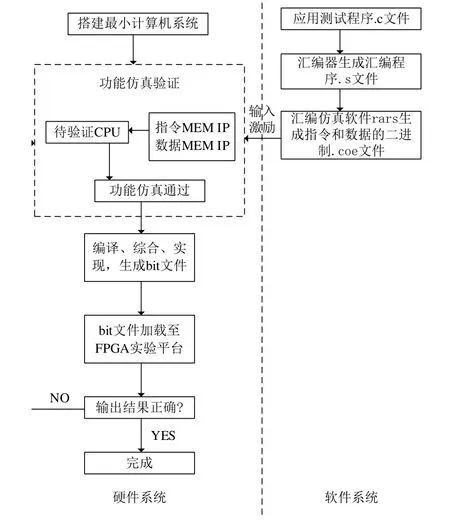

计算机组成原理实验课程旨在以“搭积木”的方式构建一个能正确工作的最小计算机系统,实验内容主要包括CPU调试技术以及CPU部件级设计、编译工具使用及汇编程序设计、单周期CPU设计、流水线CPU设计和综合设计。其中,CPU作为计算机系统的核心器件,是实验课程中需要重点设计的部分。最小计算机系统工作原理如图2所示。

Fig.2 Working principle of minimum computer system图2 最小计算机系统工作原理

2.1 CPU部件级设计

CPU硬件架构由一系列功能部件组成,如算术逻辑单元(Arithmetic and Logic Unit,ALU)、寄存器、存储器等。这些功能部件通过数据通路与控制器互连,实现了一个指令的5个处理步骤:取指、译码、执行、访存、写回。在实验课程中,部件级实验主要包括ALU设计及其应用、寄存器堆与存储器设计。

2.2 编译工具使用及汇编程序设计

“龙芯杯”CPU设计大赛的初衷在于提高学生的计算机系统能力,参赛队员不仅要掌握CPU的工作原理及设计方法,而且需要了解基于GNU编译套件(GNU Compiler Collection,GCC)编译的一般过程,即一个C或汇编程序是如何一步步转化为一个可执行文件的。由于待测试的最小计算机硬件系统没有运行任何操作系统,无法直接运行可执行文件,因此需要利用RAM IP的初始内容加载功能。基于此,课题组设计了GCC交叉编译工具的使用和汇编程序设计方面的实验内容。

2.2.1 GCC交叉编译工具使用

结合CPU设计大赛中对交叉编译工具的使用要求,同时借鉴美国一流大学UC-Berkeley、Stanford大学和卡内基梅隆大学等在相关实践课程方面的教学理念及教学思路[13]:“C语言程序→汇编语言程序→机器目标代码→处理器结构”,在单周期CPU设计实验开始之前,课题组安排了GCC交叉编译工具的使用实验。学生根据指导书完成虚拟机环境搭建,通过使用GCC工具和简单的Linux 操作命令,将一个简单的C语言程序hello.c通过编译、汇编、链接,转换成目标机器代码。该实验作为一个验证性实验,具有很强的综合性,旨在帮助学生理解高级语言与机器语言之间的转换关系,使学生对一个程序的处理过程以及计算机硬件系统和软件系统是如何协调工作的,有一个全面了解,初步建立计算机系统概念。

2.2.2 汇编程序设计

计算机组成原理实验要求学生在FPGA开发板上设计并实现一个最小计算机硬件系统,然后通过在该计算机硬件系统上运行测试程序来完成CPU的功能验证。该测试程序通常采用C语言或汇编语言编写。编写C语言代码比较方便、快捷,适合编写复杂程序;汇编语言在编写时虽然比较繁琐,但可以明确控制指令顺序,编译结果。因此,帮助学生学会阅读并设计汇编程序非常有必要的。

在汇编程序设计实验中,要求学生设计汇编程序,实现斐波那契—卢卡斯数列,然后利用汇编仿真工具Rars(RISC-V Assembler and Runtime Simulator),将汇编程序的代码段与数据段分别转换成inst.coe和data.coe文件。该coe文件即可作为后续CPU的功能测试程序。

2.3 CPU调试技术

从学生做实验的周期来看,仿真和调试所占比重相对较大,也是学生反馈最多问题的地方。CPU设计大赛给出了一套基于Trace比对的调试仿真技术[14],其核心思想是单步调试策略,能够判断每一行代码的运行结果是否正确,可以帮助参赛者对自己的设计进行仿真验证。但在实际调试过程中,经常会碰到仿真上板行为不一致的情况,更多时候是仿真正常,上板异常。由于学生上板调试能力较弱,导致很难定位错误。基于此,课题组借鉴基于Trace比对的调试仿真技术核心思想:单步调试策略,对本部分实验内容作如下安排:①设置Vivado在线调试工具ILA(Integrated Logic Anylyzer);②通过FPGA开发板上的拨码开关控制Run Mode模块,控制CPU工作在单步运行或连续运行模式;③在单步运行模式下,通过按键控制Run Mode模块输出时钟脉冲,即按一次按键,输出一个时钟脉冲。

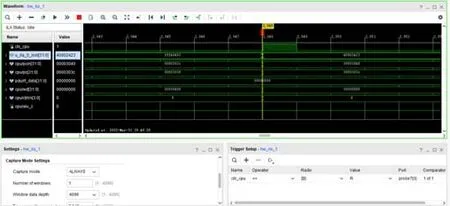

在上板异常时,首先控制CPU运行在单步运行模式,然后按下时钟脉冲触发按键,通过单步调试的“慢动作”运行程序的每一行代码,之后利用ILA工具抓取关键的调试信号,如PC值、从RF读出的数据rf_data、从数据存储器读出的数据m_data、RF的写回数据wb,以及各流水段寄存器控制信号ctrl、ctrlm、ctrlw等,能够看到每一行代码的运行行为是否符合预期,从而及时定位出错点,如图3所示。其中,clk_cpu是CPU模块的时钟信号,将clk_cpu的上升沿作为触发条件。

Fig.3 CPU single step running ILA interface图3 CPU单步运行ILA界面

2.4 CPU设计

2.4.1 单周期 CPU设计

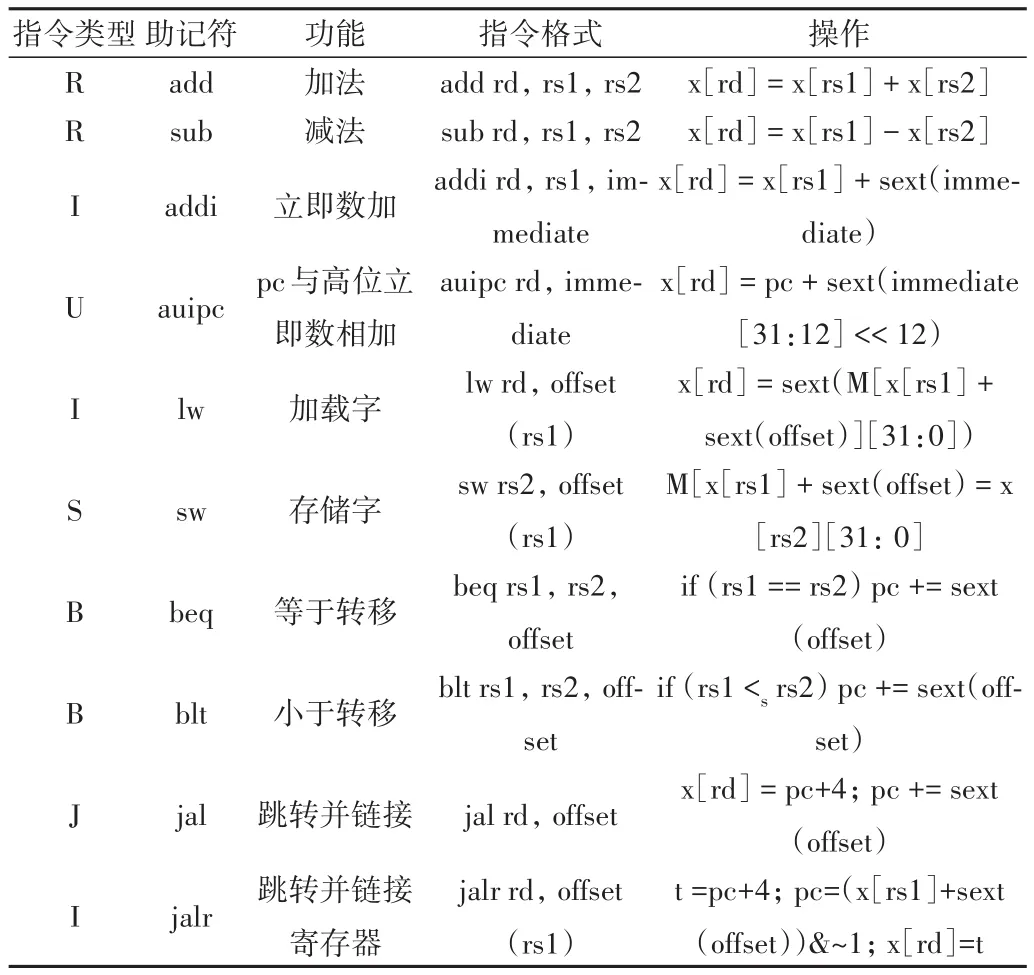

为了使学生能够在最短时间内接触到CPU设计的核心知识,课题组从基础整数指令集RV32I中选取10条最具代表性的指令,构建最小计算机系统。10条指令分别为:add,addi,sub,auipc,lw,sw,beq,blt,jal,jalr,其功能介绍如表1所示。实现上述10条指令的单周期CPU数据通路如图4所示。

Table 1 The instructions implemented by CPU表1 CPU需要实现的指令

Fig.4 Datapath of single-cycle CPU图4 单周期CPU数据通路

2.4.2 流水线CPU设计

流水线是现代工业体系的关键思想。在现代CPU中,为了缩短数据通路、提升主频,设计者使用多组寄存器将CPU的各个部分分割开来,形成了指令与数据的流水线。一般来说,电路主频越高,所需的流水线的级数则越多,但这并不意味着级数越多越好。由于触发器本身存在延时,两级流水线之间的路径和组合逻辑都会引入延时,因此主频不能无限提高。其次,流水线级数越多,所带来的相关性问题便会越复杂。在本实验中,采用最经典的5级流水线设计,每条指令均包含IF(Instruction Fetch,取指令)、ID(Instruction Decode,译码)、EX(Execution,执行)、MEM(Memory Access,访存)和 WB(Write Back to Register,写回)5个步骤。

流水线CPU可能存在3类相关问题[15]:结构相关、数据相关和控制相关。本实验要求学生在单周期CPU数据通路基础上,设计出相同指令集的流水线CPU数据通路,然后按照以下4个步骤设计并运行CPU:

步骤1:设计理想流水线CPU,并能够运行无数据相关和转移指令的测试程序(指令存储器加载no_hazard.coe)。

步骤2:设计仅有数据相关检测和处理单元的流水线CPU,并能够运行仅有数据相关的测试程序(指令存储器加载data_hazard.coe)。

步骤3:在步骤2的基础上,增加控制相关检测和处理单元的流水线CPU,并能够运行仅有数据相关和转移指令的测试程序(指令存储器加载hazard_test.coe)。

步骤4:运行测试程序,计算斐波那契—卢卡斯数列,查看时序报告和资源利用率,并与单周期CPU运行结果作比对。

2.5 综合设计

经过前面对CPU部件级设计、汇编语言程序设计、单周期CPU设计、流水线CPU设计及CPU调试技术的实践训练后,学生基本掌握了在FPGA开发板上设计出一个最小计算机硬件系统的方法,并且熟悉了FPGA开发板的外设资源。在本实验课程的最后,课题组安排了综合设计实验。

综合设计实验要求学生分组完成,每组由2名同学分工合作,从而锻炼学生团队协作的能力。实验结果评估采用项目答辩的形式,每个小组选派代表上台,通过PPT和视频展示,介绍项目设计原理和特点,锻炼学生的心理素质;通过问答环节,提升学生主动探索的热情和学习的积极性,增强各个小组之间的对抗性。

3 实验考核评价

实验考核评价是实验教学过程中非常重要的一环,建立科学的实验考核评价机制是保证实验教学质量的重要手段[16]。在单周期和流水线CPU实验的考核过程中,由于系统功能复杂,对实验结果进行科学有效的量化则显得尤为重要。课题组借鉴了部分CPU设计大赛中的评分标准,将CPU实验考核划分为功能测试得分和性能测试得分。

(1)功能测试得分以正确通过CPU测试程序中的指令项数为评价依据。计算方法由式(1)所示:

学生每次测试通过一部分指令即可得到一部分分数,不仅提高了学生对实验的兴趣,而且还能较好地了解学生的完成情况。

(2)性能测试得分以CPU运行测试程序所需的时间为评价依据。在FPGA内部集成1个时钟周期计数器,并将计数值显示在外设数码管上。基本计算方法如下:

课题组设置一个最小和最大执行时间,性能测试分值分别定义为100分和0分,学生成绩映射至[0,100]区间。

程序执行时间的计算方法如式(2)所示:

性能得分计算如式(3)所示:

其中,参数k、b由最大执行时间和最小执行时间决定。

4 教学效果

经过计算机组成原理实验课程的训练后,绝大多数学生能够针对给定的RISC-V指令系统,在FPGA开发板上设计出一个最小计算机硬件系统;通过对编译工具的使用及汇编程序设计,学生能够全面理解计算机系统硬件与软件之间的衔接关系。目前汇编程序设计实验在2021年和2022年春季学期得到实施,学生接受程度较高,增加该部分实验内容的意义是为了帮助学生初步建立计算机系统概念。在2022年春季学期,编译工具使用、单步调试思想结合ILA工具使用和量化实验检查方案的相关实验仅在分级教学中面向CPU设计竞赛选拔的提高班得到初步实施,让提高班的学生提前了解CPU设计大赛的技术方案,提高学生参与学科竞赛的积极性。中国科学技术大学在2020、2021年度参加提高班的学生人数分别是9人和14人,2022年度增加至18人,说明学生参赛的积极性得到提高。

5 结语

课题组经过不断探索挖掘,从计算机组成原理实验课程部分设计内容和考核评价体系方面引入了竞赛元素,将竞赛与教学有机结合,弥补了课程在难度和新颖性方面的不足,引导更多学生积极参与学科竞赛,从而达到了以赛促学、赛教融合的目标。该教学改革方案计划在2023学年同时应用于计算机组成原理实验分级教学中的普通班和提高班。