MEMS陀螺双通道数字接口系统设计*

2023-03-22吴奕铭谭永海綦声波

吴奕铭,谭永海,张 欣,綦声波,李 崇

(中国海洋大学 自动化及测控系·青岛·236000)

0 引 言

微机电系统(Micro-Electro-Mechanical Systems,MEMS)陀螺仪作为一种测量外部旋转角速率的传感器,自投入市场以来就凭借着其自身相较于传统陀螺仪的体积小、功耗低、成本低的独特优势[1-4],被广泛应用于水下设备[5]、无人驾驶汽车[6]、智能机器人与无人机系统等领域[7-8]。但是,如何进一步推动MEMS陀螺迈向可靠产品级的应用,一直是业内公认的难点所在[9]。

近年来,关于MEMS陀螺各个领域的研究应用也越来越多[10]。2021年,姜波等[11]设计了一种内嵌梳齿电容的全对称八质量MEMS陀螺,有希望成为下一代高性能的快速响应陀螺;2022年张志勇等[12]设计了一种高抗振的双质量块MEMS陀螺,通过优化敏感结构大大提高了该型号陀螺的测量精度;2020年,哈尔滨工业大学团队设计了高性能低通ADC数模混合芯片用以开发一种新型的接口电路方案[13];2021年,中国科学院微电子所的范艺晖等[14]采用了Verilog-A硬件语言建立MEMS陀螺仪的接口电路模型并进行了行为级仿真和实验验证;同年,国外的TDK公司发表了MEMS陀螺与专用接口芯片封装一体的设计方案,极大提升了陀螺的零偏稳定性[15]。

目前,许多研究工作主要集中在MEMS陀螺本身的结构设计与配套的接口电路上[16],但随着MEMS陀螺本身性能的不断提高,传统的单通道测试系统局限于自身的接口系统设计,往往只能费时费力地对高性能MEMS陀螺管芯逐一测试,这样效率相对低下的做法已经逐步落后于MEMS陀螺整体产业高效率化的发展趋势,也成为当前MEMS陀螺测控领域的一大痛点。因此,MEMS陀螺整体产业化、快速化发展带来的对批量化测试迫切需求与现有单陀螺接口系统测控效率相对低下之间的矛盾逐渐显现出来,业界急需对多通道接口系统展开研究与落地工作以满足上述产业化需求。

针对上述需求,本文提出了一种新型双通道MEMS陀螺接口电路来满足多个陀螺的实时测控工作的需求。本文工作主要分为三部分,包括对MEMS陀螺基本运行原理进行分析,设计新型的双通道接口电路以及与之配套的FPGA+ARM端数字系统架构。经测试结果表明,本套接口系统能够实现在同样环境下对同一批次两个陀螺进行相互独立的测控工作,为后续MEMS陀螺的产业化测控打下了坚实的基础。

1 MEMS陀螺双通道测试原理

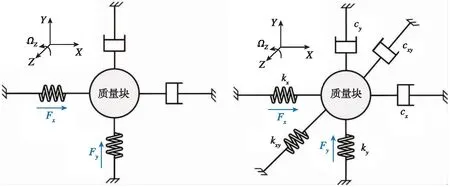

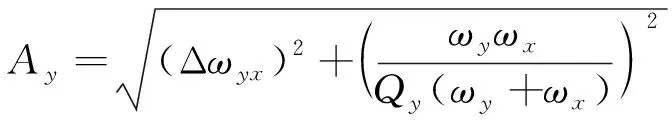

MEMS谐振陀螺的工作原理是基于科里奥利力来实现的,理想陀螺的模型如图1所示,其动力学模型则为

图1 MEMS陀螺仪物理模型Fig.1 Physical model of MEMS gyroscope

(1)

设X模态为驱动模态,Y模态作为敏感模态,考虑如图1左图中非理想条件下不可避免地存在着模态耦合,此时求得的敏感模态稳态解为

(2)

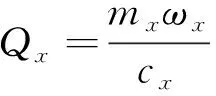

图2 单个陀螺接口电路结构示意图Fig.2 Schematic diagram of a single gyro interface circuit

在陀螺实际测试工作中,MEMS陀螺不可能完全处于理想环境,且其测控调试过程一般极为费时费力,以上文提到的PLL与AGC为例:对PLL来说,首先要进行大范围的扫频工作来找到陀螺两个模态的谐振频率,接着要不断地重复扫频以找到精准的频率值,一般要求在0.01Hz以内,最后还要求在数字系统中设计控制算法以产生该频率的激励信号来对陀螺谐振子进行持续激励,使其一直保持在输出幅值最大、检测敏感度最高的共振状态;而对AGC而言,其复杂之处在于要求陀螺两个模态反复交换来开启该控制环路,以确定AGC的最佳工作方式;除此之外,PLL与AGC两者的控制环路都需要调整各自的PID 参数,来尽量缩小各自的控制环路误差以提高控制精度,但参数调整这类工作,一般都需要经验丰富的专业人员耗费大量时间精力来完成。因此,单个陀螺的测控工作正常情况下是非常消耗时间和人力的,若能同时对两个陀螺进行独立测控,那无疑是提高了一倍的效率,也对推动MEMS测控行业发展极为有利。

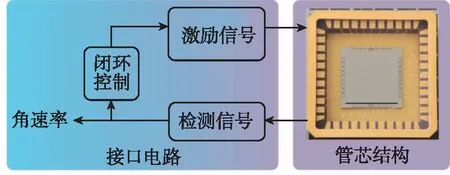

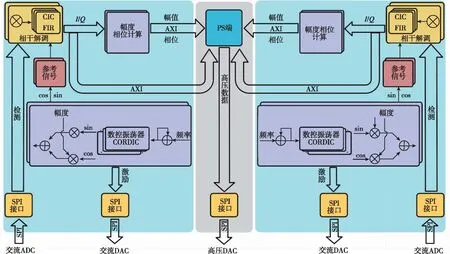

伴随着国内MEMS产线的井喷式发展,对MEMS陀螺测控工作的效率提出了更高的要求。每次仅能对单个陀螺进行测控的MEMS陀螺接口系统已经不能满足科研团队、MEMS生产制造商对大批量高效率测控标定的需求。同时,现有的单陀螺测控系统中也存在着大量的资源冗余,并未对其进行更充分的利用。为了进一步利用系统内冗余资源,提高对MEMS陀螺的批量化测控标定效率,本文提出了如图3所示的数字式MEMS陀螺双通道接口系统。系统电路总体架构可分为五个部分,分别为前端模拟电路(紫色部分)、数字/模拟转换电路(绿色部分)、后端数字系统(蓝色部分)、人机交互终端(黄色部分)与系统供电电路(红色部分)。

图3 MEMS陀螺双通道接口系统总体架构图Fig.3 Overall architecture diagram of MEMS gyro dual channel interface system

2 模拟电路与数字系统设计

2.1 前端模拟电路设计

2.1.1 前端激励信号电路

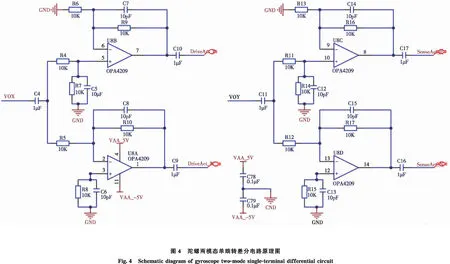

由于本文使用的是双路激励信号,而且采用了差分驱动方式以获得更高的驱动效率和抑制共模干扰效果,但数模转换(Digital to Analog Conversion,DAC)通常为单端输出,所以设计了如图4所示的单位增益单转双电路。图4为1号陀螺的单转双电路,总体分为三部分,以X模态电路为例,其为一个分压同相单位增益放大器与一个反向单位增益放大器组成。图4中取隔直电容C17=1μF,其余阻容大小均为R=10kΩ,C=10pF,此时可以得到其截止频率为

(3)

输出电压则分别为

V+=

15.9Hz≪fV≪1.59MHz

V-=

15.9Hz≪fV≪1.59MHz

(4)

其中,增加电容C是为了增加相位裕度补偿,从而减少实际高频自激状况的发生;电路运放部分则选用的是OPA4209四通道运放来进行陀螺两个模态的单端转差分信号生成。

2.1.2 前端激振缓冲电路

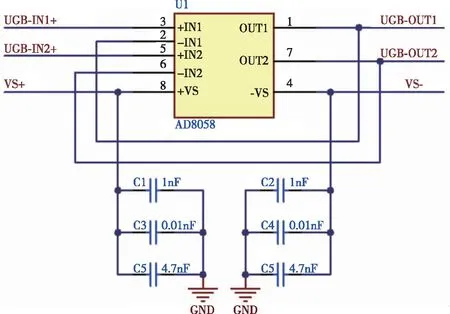

考虑到陀螺表头是容性负载,因此要求施加在陀螺电极上的激励信号需具有一定的带负载能力。所以本套系统采用的激励信号,并不是由DAC产生后直接输入给陀螺,而是经过了一级缓冲电路之后才输入至陀螺对应的激励电极。因此,单位增益带宽(Unity-Gain Bandwidth,UGB)模块的作用仅仅是起到对激励信号缓冲的作用,并不需要对信号进行放大,选择放大器时应更看重其带宽指标;而且要对陀螺的两个振动模态进行激励,所以必须要对两路信号同时进行缓冲处理,放大器也需优先考虑双通道产品。

基于上述原因,本文选择了双通道且低成本的AD8058型号放大器,该型号放大器有很强的容性负载驱动能力,能提供325MHz的-3dB带宽,可完全满足陀螺激励信号的需求。UGB部分电路设计如图5所示,由DAC输入的交流激励电压信号,分别进入IN1+和IN2+,经单位增益缓冲后通过OUT1和OUT2输出。

图5 双通道前端激振缓冲电路图Fig.5 Two-channel front-end shock buffering circuit diagram

2.1.3 前端跨阻放大电路

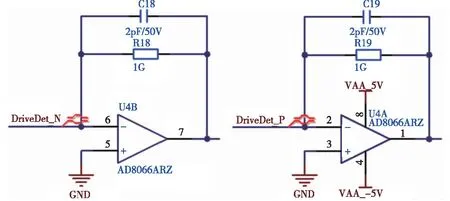

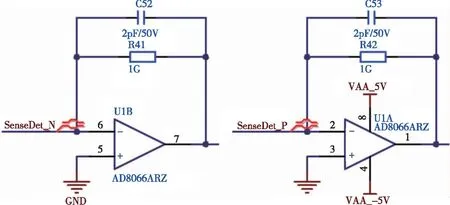

由于陀螺检测电极输出的电流信号幅值非常微弱,在传输过程中极易收到其他强信号的干扰,使用跨阻放大器(Trans-Impedance Amplifier,TIA)则可以放大该电流信号并将其输出转化为电压信号,便于后续信号转换与处工作。本套系统选用了场效应管输入型放大器AD8066,其优点在于可以提供高达145MHZ的-3dB带宽以及180V/μs的压摆率,对于10kHz或者1MHz的放大需求而言完全足够。

驱动模态和敏感模态的TIA电路结构设计分别如图6和图7所示,其中两个模态差分输出共计四路信号,均为相同结构;现在以驱动模态正向检测信号P通道为例,R19与C19为反馈阻容,令其数值分别为R和C,则该电路结构的传递函数可写为

图6 驱动模态双通道TIA电路Fig.6 Drive modal dual channel TIA circuit

图7 检测模态双通道TIA电路Fig.7 Detect modal dual channel TIA circuit

(5)

对于电流来说,该系统表现出一个低通特性,为了降低电路内噪声以及提高放大增益效率,本文选用了1GΩ的反馈电阻和2pF的反馈电容。

2.2 数字系统设计

数字系统总体架构总体分为两部分,可编程逻辑(Programmable Logic,PL)端采用FPGA来实现各种模块设计,可编程系统(Programming System,PS)端则是利用ARM完成对多个陀螺的基带信号的控制闭环与通信协议部分。

2.2.1 FPGA高速算法设计

本文设计的双通道接口系统的PL端,主要包含了以下相关模块:首先是数控振荡器NCO,其在FPGA端由频率字累加器、CORDIC模块、乘法调幅模块和DAC SPI接口模块组成,用来产生频率可变的正/余弦波,从而作为激励信号;然后是数字转模拟信号采用的DAC80502,其数字信号的SPI通信接口模块也是在FPGA上进行设计的;高压DAC选用的是DAC81404,其作用是输出8路正负20V高压信号用于供给两只陀螺的频率调谐,其模拟端口直接作用在陀螺表头,数字端复用了上述的SPI接口;接下来是陀螺的检测信号解析部分,ADC选用ADS8354,将采样到的检测信号数字化便于后续处理,并采用相干解调来得到其中的幅度信息,为保证相干解调的精确度,基于上文NCO的设计,将其生成的激励信号作为相干解调的参考信号,保证其同源度一致,最大限度地抑制频差项的出现;之后是对解调信号进行混频滤波,混频器复用上述乘法器设计,而滤波器则采用了级联积分梳状(Cascaded Integrator-Comb,CIC)滤波器与有限冲激响应(Finite Impulse Response )滤波器的组合形式进行抗混叠降采样,可以将采样率从ADC的250KHZ降至1KHZ,截止频率则低至100HZ,从而满足后续控制需求;最后采用坐标旋转数字计算方法(Coordinate Rotation Digital Computer,CORDIC)的向量模式来计算陀螺的幅值(Amplitude,AMP)与相位θ,方便后续的环路控制。FPGA整体模块设计如图8所示。

图8 FPGA端相关模块设计原理图Fig.8 FPGA terminal related module design schematic diagram

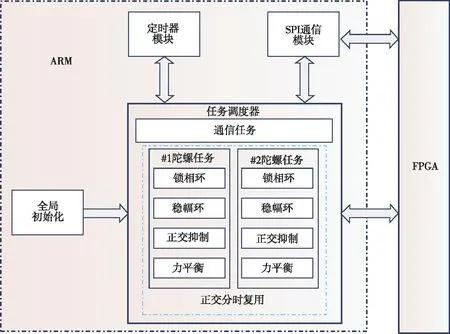

2.2.2 ARM端控制闭环与通信

本文设计的双通道接口系统的PS端,总体架构如图9所示,主要包含了以下相关模块:首先是全局初始化模块,用于初始化PL侧所有的AXI-GPIO模块;定时器模块,用于初始化1ms定时器并用作前后台调度框架的时钟源;SPI通信模块,用于实现PC上位机与PS之间的数据/指令通信;任务调度模块,包含了通信协议任务与两个陀螺的全部顶层业务。其中每个陀螺的任务又包含锁相环任务、稳幅环任务、正交抑制任务和力平衡任务。

图9 PS端程序模块总体设计图Fig.9 PS program module overall design drawing

为了保证系统具有最佳实时性能,程序框架设计上采用了经典的前后台模式:前台任务只有一个,为1ms定时器中断;后台任务为通信任务与陀螺任务。两个陀螺的控制任务变量组相互独立,并以正交分时复用方式运行。闭环任务均采用了经典的PID反馈控制方案,为保证系统的输出无明显跳变在具体实现过程中采用了增量式PID。

通信部分选择四线SPI通信,并利用SPI的同步传输特性,将上行数据与下行指令合并到一起进行传输,减少了任务调用次数。在SPI总线中,PS端的主从关系为从设备,只需要向SPI缓冲区装填数据,而不需要处理中断,最大程度保证了系统的实时性与简洁度,保证了控制环路的稳定性。

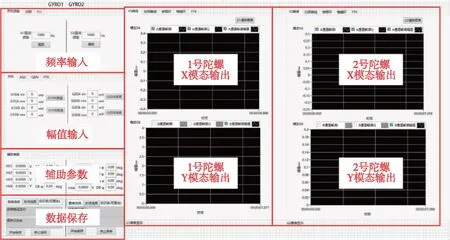

3 双通道接口系统功能展示

本套双通道接口系统调试终端为图10所示的人机交互上位机。其中包含开环驱动、IQ信息、扫频曲线、控制环路及数据保存等多个功能,前端界面整体设计如图10所示。

图10 LabVIEW测试终端前端总界面设计Fig.10 LabVIEW test terminal front-end general interface design

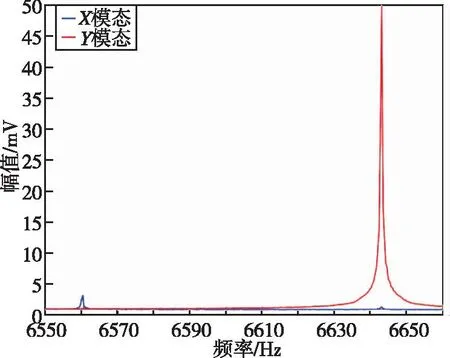

3.1 双通道双工异步扫频

在开环状态下设置1号与2号两个陀螺的扫频范围为6550~6660Hz,得到图11的扫频曲线,根据曲线可得到陀螺两个模态各自的谐振频率与对应峰值,且两个模态间存在一定的频差与耦合。根据扫频步长的不同设置,可以得到不同的扫频结果,继而作为中心频率来进行增量式的比例-积分(Proportional-Integral)计算。

(a) 1号陀螺扫频曲线

(b) 2号陀螺扫频曲线图11 双工异步陀螺扫频曲线图Fig.11 Frequency sweep graph of duplex asynchronous gyro

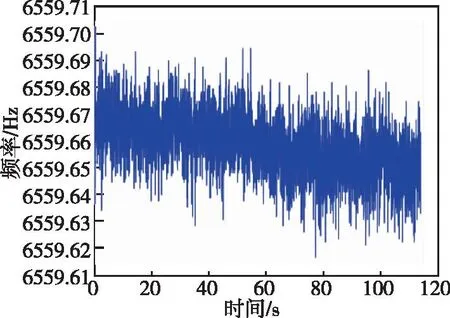

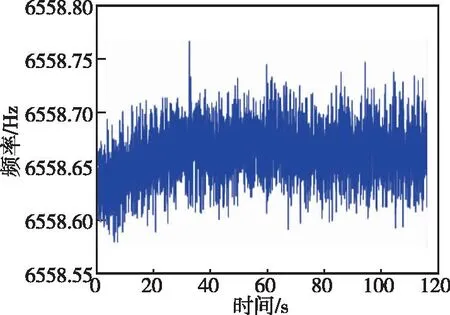

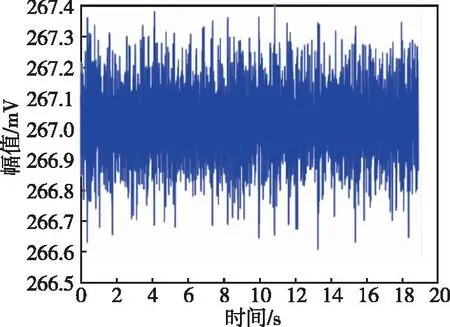

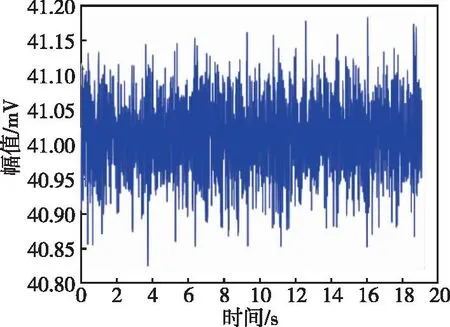

3.2 双通道双工锁相与稳幅

以两个陀螺Y模态来测试器驱动环路的闭环特性,开启PLL与AGC的闭环后,其测试结果如图12所示。以1号陀螺为例,当其Y模态锁相并稳幅后,其输出频率摆幅在(6559.66±50)mHz以内,其检测到的幅值摆幅被控制在(267±0.5)mV以内。

(a) 1号陀螺PLL输出频率

(b) 2号陀螺PLL输出频率

(c) 1号陀螺AGC稳定幅值

(d) 2号陀螺AGC稳定幅值图12 双陀螺驱动环路闭环测试结果图Fig.12 Double gyro drive loop closed loop test results

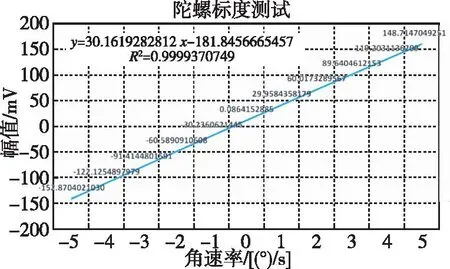

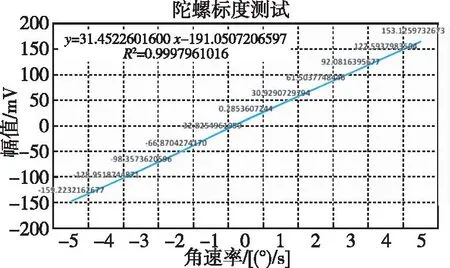

3.3 双通道陀螺线性度测试

进行陀螺线性度测试实验时,将转台角速率设置为-5(°)/s至+5(°)/s(以顺时针旋转为正,逆时针旋转为负),以每1(°)/s为测试间隔,在旋转角速率稳定时,每个角速率停留10分钟并记录敏感模态同相分量稳定后的幅值。由图13可知两只陀螺的标度因数均在30mV/[(°)/s]以上,线性度经计算后则均保持在9.92×10-5% 以下,十分优异。

(a) 1号陀螺标度测试结果

(b) 2号陀螺标度测试结果图13 不同角速率下陀螺敏感模态幅值线性度测试结果Fig.13 Test results of amplitude linearity of gyro sensitive modes at different angular rates

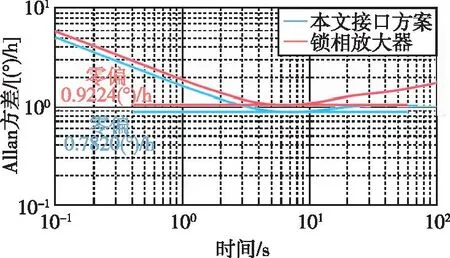

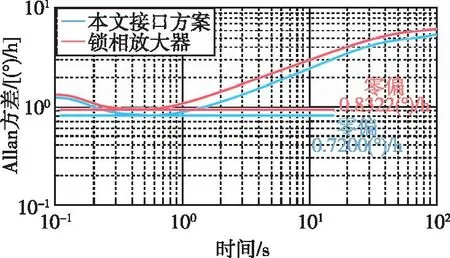

3.4 双通道陀螺艾伦方差

采用本文所提的双通道系统以及锁相放大器,分别记录1号和2号陀螺在静止状态的输出,二者设置相同的采样速率与闭环参数,再分别对输出数据进行Allan方差计算,两个陀螺的零偏对比如图14所示。根据测试结果可见,本文所提的双通道系统相对于锁相放大器,两个陀螺测试时的零偏不稳定性均优于锁相放大器0.1(°)/h。

(a)

(b)图14 双通道系统与锁相放大器零偏对比测试图Fig.14 Zero-bias comparison test diagram of a two-channel system and a lock-in amplifier

4 结 论

本文首先分析了陀螺运行的基本原理,并根据陀螺接口系统需求提出了一套新的双通道陀螺接口测控系统方案。最终实现的双通道陀螺测控系统基本能够实现同时对两个通道陀螺进行测控标定,极大地提高了陀螺的测控效率,优化了陀螺接口电路的硬件需求,且设计的接口系统易于后续二次开发,为后续推广陀螺的测控产业化,提供了一种有价值的方法。但本文所提出系统并未考虑MEMS陀螺自身的各种非线性因素,因此后续将研究非线性控制、多维度参数测控标定等问题,并将其逐步添加集成到双通道接口系统中。