基于遗传算法的抗网表逆向攻击逻辑混淆方法

2023-02-18赵毅强马浩诚张启智何家骥

赵毅强 蒯 钧 马浩诚 张启智 高 雅 叶 茂 何家骥

(天津大学微电子学院 天津 300072)

1 引言

随着集成电路(Integrated Circuit, IC)工艺节点的不断缩小,摩尔定律趋于失效,半导体产业已逐步进入后摩尔时代。硅工艺技术逐渐逼近物理极限,使得不断攀升的芯片性能、功耗、成本需求,已无法单纯依靠提升工艺满足,而要依赖于更为复杂与精巧的设计架构与实现策略。知识产权核(Intellectual-Property core, IP core)的出现,能够在一定程度上缓解高昂的一次性工程成本与漫长的产品开发周期等问题。但是,基于逆向工程技术分析电路并获取芯片原始设计,已成为一项越来越严重的硬件安全威胁,并以此衍生出IP窃取、IC过度生产、IC伪造、硬件木马植入等诸多硬件安全问题。

目前,针对逆向工程的防御技术主要分为IC伪装技术与逻辑混淆技术。IC伪装技术,主要通过虚假连接等方式设计结构相似但功能不同的逻辑单元,从而抵抗攻击者基于物理版图识别门级网表。逻辑混淆技术,主要通过向门级网表中植入混淆单元,从而抵抗攻击者基于门级网表识别逻辑功能,具体分为基于组合逻辑的逻辑混淆与基于时序逻辑的逻辑混淆。基于组合逻辑,Baumgarten等人[1]通过嵌入可重构逻辑块,混淆电路输入到输出的数据路径。Dupuis等人[2]通过插入与门和或门,混淆网表低可控性节点。文献[3,4]基于点函数或比较器逻辑实现逻辑混淆,以抵抗可满足性检查(SATisfiability checking, SAT)攻击。文献[5]采用基于反相器与多路选择器的混淆单元,防止攻击者通过识别单元结构获取密钥,并结合物理不可克隆函数(Physical Unclonable Function, PUF)生成混淆密钥。基于时序逻辑,Chakraborty等人[6]采用Harpoon策略向有限状态机(Finite State Machine, FSM)中引入额外状态以实现逻辑锁定,从而保证电路在未解锁时混淆FSM。Hu等人[7]基于FSM实现对电路不定时的多次认证,从而指数提升针对SAT攻击的抵抗属性。文献[8]针对不同FPGA的PUF响应值生成特定的增强FSM,实现了按设备付费许可的逻辑混淆策略。张会红等人[9]采用版图伪装、异或门混淆、FSM混淆等技术,实现物理-逻辑-行为的3级协同混淆。

然而,随着近年来逆向工程技术的高速发展,基于门级网表的逆向技术为逻辑混淆带来了新的挑战。通过分析网表寄存器的拓扑连接关系与扇入扇出逻辑相似性,基于门级网表的逆向技术可以恢复寄存器传输级(Register-Transition Level, RTL)的词级Reg型变量与变量间运算函数。文献[10,11]通过分析寄存器连接与功能匹配度,实现数据通路词级结构的提取。文献[12,13]基于位片识别与聚合,以及寄存器结构匹配等方式,从非结构化网表中提取移位寄存器、计数器、RAM、加法器等关键组件。文献[14-16]基于寄存器输入结构的相似度区分状态寄存器与数据寄存器,以分割电路控制逻辑,并进一步恢复FSM。Albartus等人[17]采用基于数据流的网表分析技术,通过结合控制信息与结构信息的独立度量结果,在任意展平的网表中提取词级寄存器结构。

基于组合逻辑与FSM的混淆策略,可以很好地实现电路运算函数与状态控制逻辑的混淆,然而其主要混淆了数据寄存器组间用于逻辑运算的组合逻辑、状态寄存器组用于状态切换的组合逻辑,对网表中寄存器网络的拓扑连接关系没有影响。逆向攻击者依然可采用基于门级网表的逆向技术恢复RTL级寄存器词级变量,从而非法获取电路RTL设计架构细节,或识别敏感数据寄存器并嵌入恶意电路。

本文提出一种基于遗传算法的自动化逻辑混淆方法,通过分析寄存器拓扑网络结构,筛选混淆节点对并创建冗余连接,从而混淆寄存器的拓扑相似性特征,可以在低面积开销下,有效地抵抗逆向工具从门级网表中恢复RTL级词级信息、控制逻辑与数据通路,实现良好的门级网表抗逆向攻击效果。主要贡献如下:

第一,针对SM4电路网表正确逆向了其RTL级词级信息,证明了网表逆向攻击对电路存在安全威胁;第二,提出一种基于混淆寄存器拓扑结构的逻辑混淆方法,并证明了该方法抵抗网表逆向的有效性;第三,采用两步式遗传算法筛选混淆节点,提升了本文方法的混淆效率并降低了开销。

具体结构安排如下:第2节介绍门级网表逆向工程的技术原理,第3节介绍本文提出的抗网表逆向的逻辑混淆方法,第4节通过实验分析了本文方法的抗逆向效果、混淆效率、性能面积开销与安全性,第5节对本文内容进行了总结。

2 门级网表逆向工程技术原理

2.1 门级网表拓扑结构

在基于硬件描述语言(如Verilog)的正向设计流程中,设计者通常采用RTL级模型对数字电路进行建模描述:通过定义多比特位宽词级Reg型变量及变量间的运算函数,将数字电路建模为控制逻辑与数据通路两部分。通过翻译、映射与优化,逻辑综合工具将RTL级设计模型转换为门级网表描述:由组合逻辑门与寄存器连接而成的拓扑网表。RTL级描述中的词级Reg型变量被综合为由多个寄存器组成的寄存器组;变量间的转换函数被综合为由多个组合逻辑门组成的组合逻辑云。

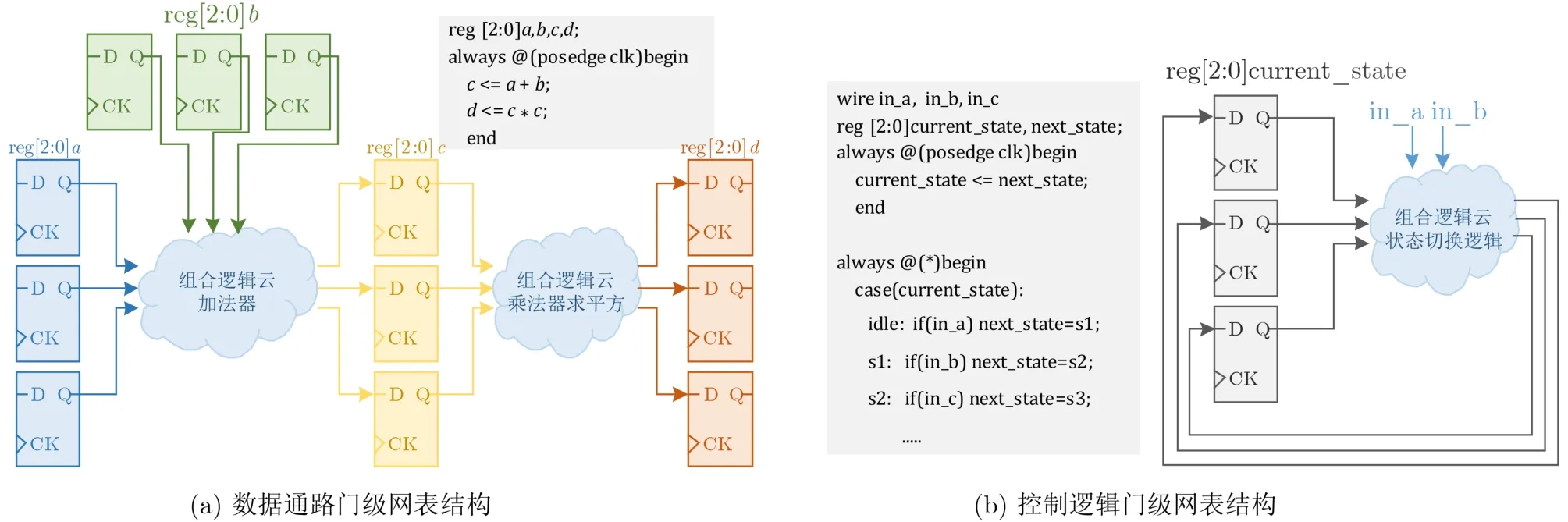

基于此,在门级网表中,数据通路体现为由多个组合逻辑云桥接的多个数据寄存器组,寄存器组实现数据的暂存,组合逻辑云实现数据间运算函数。如图1(a)中,寄存器组a/b/c/d分别暂存其数据A/B/C/D,寄存器a/b与c间通过加法器逻辑桥接,寄存器c与d间通过乘法器逻辑桥接,实现数据A/B的求和、求和结果C取平方的数据流通路。

控制逻辑为由单个状态寄存器组与组合逻辑云实现的自反馈结构,寄存器组实现当前状态的保持,组合逻辑云实现状态切换函数,寄存器组输出经过组合逻辑云运算,结果返回寄存器组输入端作为下个状态。如图1(b)中,寄存器组current_state保持当前状态,状态切换逻辑基于当前状态与输入(in_a/in_b)运算得到下个状态并返回寄存器组输入端,实现3 bit位宽的有限状态机。

图1 逻辑综合与门级网表结构

相较于RTL级设计,由于门级网表中寄存器各自分立,丢失了分组信息,且往往存在复杂的数据交互关系与控制反馈环路,因此攻击者无法通过直接查阅网表获取高层次的设计信息。

2.2 门级网表逆向方法

为了恢复RTL级信息,门级网表逆向技术通过分析分立寄存器的拓扑连接相似性特征,对寄存器进行聚类与合并,从而恢复寄存器组等高层次设计信息。一般基于如下相似性特征规则对网表进行逆向分析,如图2所示,其中圆形代表单个寄存器,箭头代表寄存器间的组合逻辑连接路径,且箭头起始端寄存器被称为箭头末端寄存器的前序寄存器,末端寄存器被称为起始端寄存器的后序寄存器:

(1)有相同前序或后序寄存器的寄存器应属于同一个寄存器组,如图2(a);

(2)前序或后序寄存器处于同一寄存器组的寄存器应属于同一个寄存器组,如图2(b);

(3)相同组的寄存器,其前序寄存器或后序寄存器的数量是相近的,如图2(c);

(4)相同组的寄存器,其与前序寄存器或后序寄存器的间的组合逻辑函数是类似的,如图2(c);

(5)处于相同组的寄存器,数据应该在同一时钟周期同步到达,若同一寄存器出现在两个周期节拍中,则合并两个节拍周期所有寄存器,并在子集内部进行2次分割,如图2(d)。

图2 同组寄存器相似性特征分析规则

为了避免逆向结果与单条特征产生过拟合,两两组合上述5条相似性特征从而得到10条聚类分析规则。分别执行10条规则对寄存器进行分析聚类,并对不同规则得到的所有聚类结果进行多数投票,得到本次逆向结果。迭代地执行该过程,直到聚类得到的寄存器组结果逐渐收敛,最终输出逆向分析的寄存器组聚类结果,以及寄存器组间的连接关系,如图3。

图3 门级网表逆向过程

完成寄存器组恢复后,针对状态寄存器组,分析其后续组合逻辑云以确定状态切换函数,并以复位状态为初始状态,通过遍历不同输入下的下个状态恢复完整状态机;针对数据寄存器组,分析组间组合逻辑云以确定数据运算函数,分析寄存器组间连接关系以获取数据流向图,最终实现从门级网表到RTL级设计的完整逆向过程。

3 基于遗传算法的抗网表逆向逻辑混淆技术原理

为了抵抗逆向工具从门级网表恢复RTL级词级变量、数据通路与控制逻辑,本文提出一种基于遗传算法的逻辑混淆方法,通过筛选不同寄存器组的扇入与扇出节点作为混淆节点对,并植入混淆单元以创建冗余连接,从而混淆寄存器拓扑网络,消除同组寄存器的相似性特征。

具体步骤如下:

(1)基于广度优先原则,对网表进行遍历,提取寄存器拓扑网络与扇入扇出汇聚节点;

(2)基于寄存器拓扑网络结构与扇入扇出逻辑,采用遗传算法筛选各寄存器组的扇出混淆点与扇入混淆点,并组成混淆节点对;

(3)基于混淆节点对选取并植入混淆单元,创建扇出混淆点到扇入混淆点的逻辑通路,从而向寄存器拓扑网络引入冗余连接,同时修改网表单元的实例化名称以混淆语义信息,最终完成混淆网表的自动化生成。

3.1 寄存器拓扑网络与扇入扇出汇聚分析

为了方便进行后续的混淆对筛选与混淆单元植入,首先采用广度优先搜索算法,对网表进行寄存器拓扑网络分析。相较于深度优先,广度优先搜索算法可以避免节点回溯操作,因此具有更快的处理速度。该算法以寄存器端口为起点,通过逐层向后遍历并跳过该寄存器的扇出组合逻辑,从而得到该寄存器的后序寄存器与扇出逻辑节点。具体算法如下,流程图如图4所示:

首先,选取待分析寄存器R。创建扇出逻辑节点集合L,并初始化为寄存器R的输出节点;创建后序寄存器集合Or,并初始化为空;随后,遍历集合L,逐个选取逻辑节点N。针对逻辑节点N,遍历其扇出逻辑单元集合Oc,逐个选取单元C:若该单元为寄存器(电路输出端口也被视为寄存器),则将该寄存器添加到集合Or中;若该单元为组合逻辑门,则将该组合逻辑门的输出节点添加到集合L中。最终,当集合L中所有逻辑节点均被遍历,存储当前集合Or为寄存器R的后序寄存器,存储当前集合L为寄存器R的扇出组合逻辑节点。

同理,通过向前遍历扇入组合逻辑得到该寄存器的前序寄存器与扇入逻辑节点。最终提取以寄存器为节点、以组合逻辑门为连接链的网状拓扑结构。

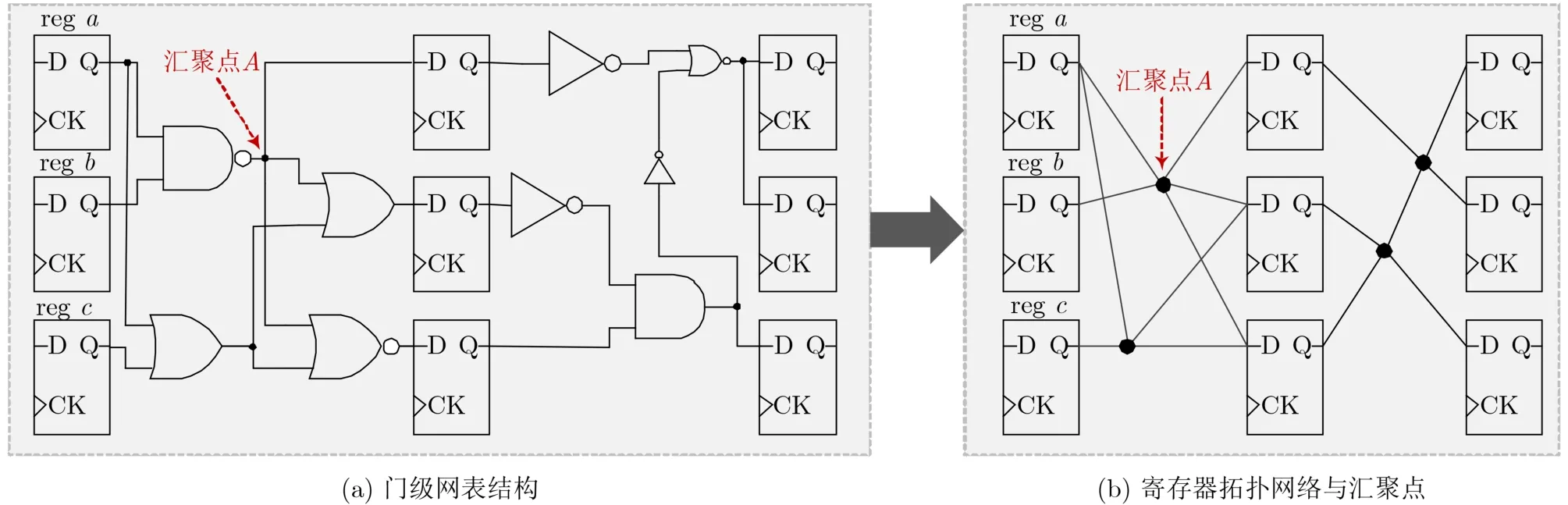

随后针对每个寄存器组,计算各寄存器的扇入或扇出逻辑节点集合L之间是否存在重复节点,从而分析该组寄存器的扇出路径或扇入路径是否存在汇聚,并提取汇聚的扇入逻辑节点或扇出逻辑节点。通过筛选汇聚节点,并在后续混淆节点筛选过程中优先选取汇聚节点,可以有效提高单个混淆节点对引入的冗余连接数,从而提升混淆效率并降低面积开销。

如图4示例所示,通过省略图5(a)所示的门级网表结构中的组合逻辑门,最终得到图5(b)中由寄存器间连接关系构成的寄存器拓扑网络,图5(b)中黑色圆点即表示不同寄存器间数据路径的汇聚节点,汇聚点A即为寄存器a与寄存器b的扇出逻辑路径汇聚点。

图4 寄存器拓扑网络提取算法

图5 寄存器拓扑网络与汇聚节点提取效果

3.2 基于遗传算法筛选混淆节点对

为了混淆同组寄存器的相似性特征,采用如下混淆策略:

首先选取两个寄存器组,并在第1个组中选取扇出逻辑节点、第2个组中选取扇入逻辑节点,组成一个混淆节点对。然后通过将节点对中的扇出逻辑节点连接到扇入逻辑节点上,则可创建两个寄存器组间的冗余连接,如图6所示。迭代地重复上述步骤,以向所有寄存器组引入冗余连接,使得每组的任意两个寄存器之间:前序寄存器数量、后序寄存器数量、前序寄存器归属的寄存器组、后序寄存器归属的寄存器组均不相同,以达成混淆同组寄存器相似性特征的结果。

图6 筛选混淆节点对并创建冗余连接

由于混淆节点对的选取,显著影响着混淆的效果与效率。为了提升混淆效果并降低开销,采用遗传算法进行混淆对的筛选。遗传算法通过模拟遗传学机理与自然选择的进化过程,进行最优解搜索。其首先在求解空间中生成一个初始种群,基于评价函数选择对环境适应度更高的个体,然后通过交叉与变异产生子代。不断重复选择、交叉、变异的过程,直到种群的适应度达到目标阈值,则输出适应度最高的个体作为最优解求解结果。遗传算法主要用于求解离散变量的组合最优化问题,因此很适合在网表中筛选混淆节点对。

本方法两步递进式地采用遗传算法进行混淆节点对筛选,缩小求解空间大小,从而提升算法性能。

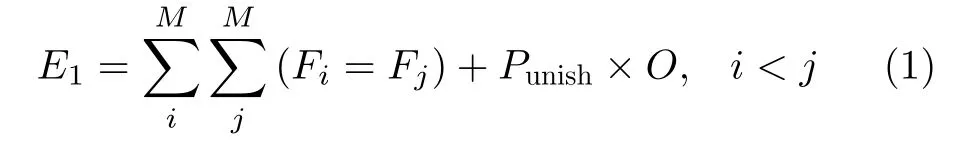

第1步:针对每组寄存器,分别在扇入与扇出逻辑节点中筛选汇聚节点作为混淆节点,使得在给定混淆节点数量N下,各寄存器所连接的混淆节点差异最大化,其中差异采用评价函数E1进行评估。采用的评价函数E1如下所示,函数值越小,代表差异越大,混淆效果越理想,具体为

其中,Fi为混淆后该组第i个寄存器的扇入或扇出混淆节点集合;O为N个混淆节点中出现重复节点的个数,通过与惩罚因子Punish相乘,淘汰出现重复节点的求解结果。本文中遗传算法搜索评价函数的最小值,因此Punish使用正值10000。混淆节点个数N取决于该寄存器组中寄存器数量M,应满足如式(2)的关系,以使评价函数结果存在收敛为理想最优值的最优解

第2步:基于找到的各组混淆节点,选取扇入混淆节点与扇出混淆节点得到混淆节点对,使得混淆后同组寄存器间的前序/后序寄存器数量、前序/后序寄存器所属的寄存器组差异最大化,其中差异采用评价函数E2进 行评估。采用的评价函数E2如式(3)所示,函数值越小,代表差异越大,混淆效果越理想,具体为

其中,Ui为混淆后第i个寄存器的前序或后序寄存器数量,Vi为第i个寄存器的前序或后序寄存器所属的寄存器组集合。

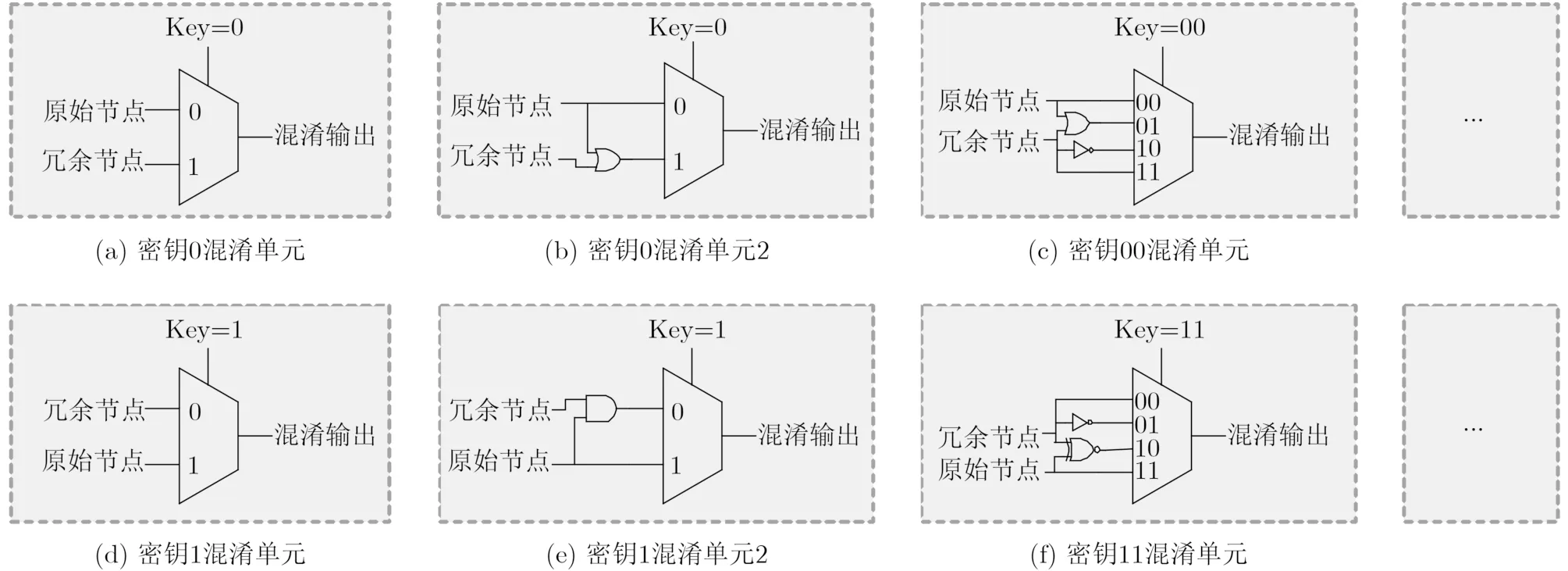

3.3 混淆单元设计与网表自动化混淆

完成混淆节点对的筛选后,通过向网表中植入混淆单元,以完成冗余连接的创建。为了不影响电路原始功能,且避免逆向攻击者通过识别混淆结构攻破混淆,本文设计了多种混淆单元,具有不同的密钥位宽、正确密钥值与逻辑门类型,如图7所示。其中,图7(a)、图7(b)为两种不同结构的密钥为单比特0的混淆单元;图7(c)为密钥为两比特00的混淆单元;图7(d)、图7(e)为两种不同结构的密钥为单比特1的混淆单元;图7(f)为密钥为两比特11的混淆单元。

图7 混淆单元逻辑结构

每个混淆单元都存在密钥输入端,当该输入端被置为正确密钥时,引入的冗余连接被屏蔽,使得电路处于正常工作状态。除密钥输入端外,每个混淆单元存在原始节点输入端与冗余节点输入端。通过将混淆单元植入到原始节点处,则可创建由冗余节点到原始节点后序寄存器的冗余逻辑路径。此外,不同的混淆单元具备不同的组合逻辑结构,通过随机选取不同的混淆单元,可以避免攻击者通过识别特定混淆结构从而定位并删除植入的逻辑混淆单元。在网表的自动化混淆过程中,针对每个混淆节点对,以节点对中扇入混淆节点为原始节点、扇出混淆节点为冗余节点,随机选取混淆单元进行植入。完成混淆单元植入后,随机修改各寄存器的实例化单元名,以隐藏网表中的语义信息,最终输出混淆后的网表。

4 实验与结果分析

本文选定SM4国密算法电路,对其进行门级网表逆向、逻辑混淆与混淆效果评估。基于SMIC 180 nm工艺,使用Design compiler工具对RTL级设计进行逻辑综合,获得门级网表。采用VCS工具对门级网表进行仿真以验证电路的逻辑功能正确性。采用文献[17]中开源逆向工具DANA进行网表逆向攻击。网表规模为200000门级,具有129059个逻辑单元,其中寄存器数量为2432。

4.1 抗网表逆向效果评估

为了评估本文混淆方法的抗网表逆向效果,使用该方法混淆原始设计网表,并分别对原始网表与混淆后的网表进行逆向攻击,最终评估其逆向结果的正确程度差异。针对网表逆向的效果评估,本文基于标准化互信息(Normalized Mutual Information, NMI)指标进行分析。该指标被广泛应用于聚类问题的效果评估,也是当前主流的网表逆向工具评估逆向效果的主要指标[14-17]。该指标值域为[0, 1],值越高代表聚类结果越准确。

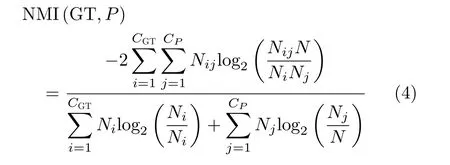

在评估过程中,以真实正确的寄存器分组情况作为标准集GT,以逆向网表得到的寄存器分组情况作为评估集P,通过分析标准集与评估集的相关度,并采用信息熵完成归一化,最终得到网表逆向结果的正确度指标,具体公式为

其中,CGT为标准集中的寄存器组个数,CP为评估集中寄存器组个数,Nij为标准集中第i组与评估集中第j组的重复元素个数,N为所有Nij之和,Ni▪为Nij矩阵中第i行之和,N▪j为Nij矩阵中第j列之和。

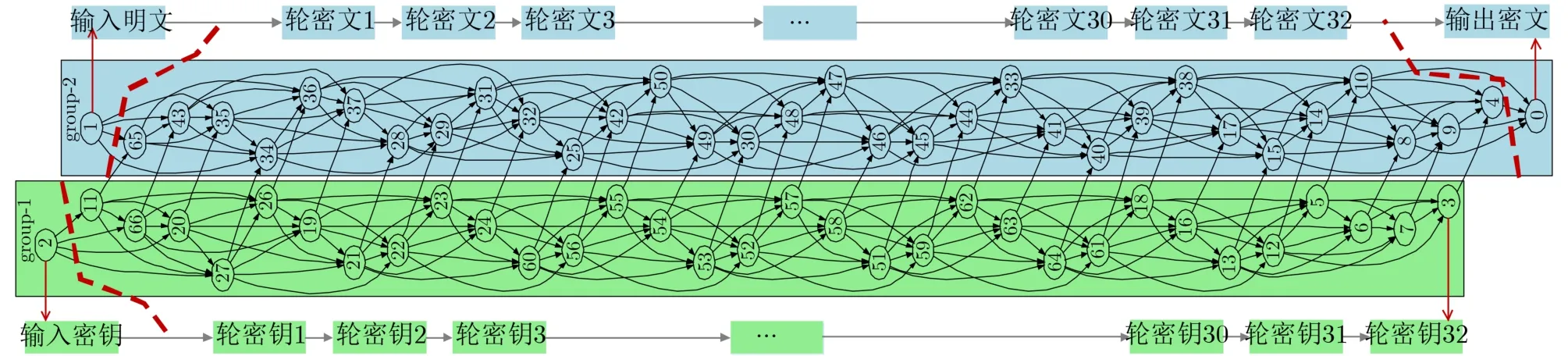

对SM4电路的原始网表进行逆向分析,其评估集P如图8所示:输入密钥、32个轮密钥所对应的共计33个寄存器组被完整地恢复在绿色区域,输入明文、32个轮密文、输出密文所对应的共计34个寄存器组被完整地恢复在蓝色区域。该结果与标准集GT完全一致,寄存器组间的数据流向与运算函数可以得到清晰完整的识别。同时,NMI评估值为1,表明所有的寄存器都得到了正确的分组。因此,对于未经混淆的该原始网表,逆向工具实现了理想的逆向效果,寄存器分组与电路数据流向得到了正确且完整的恢复。

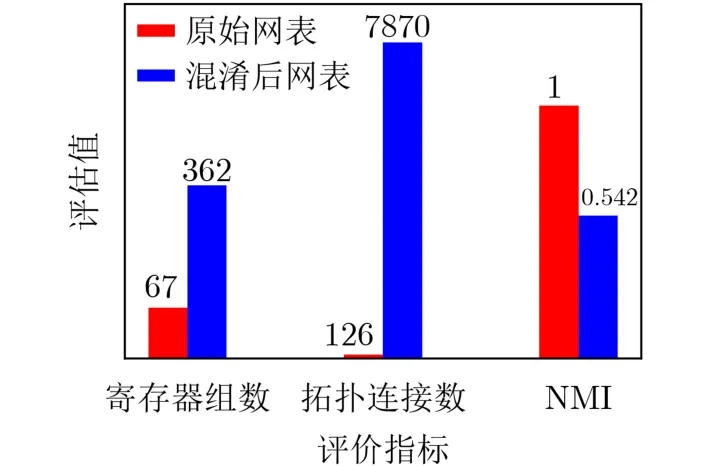

图8 SM4国密算法电路 网表逆向分析结果

采用本文混淆方法对原始网表进行混淆,通过植入280个混淆单元引入280条冗余连接,混淆引入的额外开销为0.216%。对混淆后网表进行逆向分析,结果如图9所示。相较于标准集GT的67个寄存器组,网表寄存器在评估集P中被错误地聚类为362个寄存器组,扩大了4.4倍;寄存器组间的拓扑连接条数由126条变为了7870条,扩大了61.46倍,寄存器组间的拓扑连接复杂度得到了指数提升。同时,NMI评估值为0.542,2432个寄存器中2048个(84.2%)发生了错误的聚类:即逆向得到的每个寄存器组中,各寄存器在标准集GT中都属于不同的寄存器组。只有输入明文、输入密钥、输出密文3个寄存器组,共384个寄存器,因与输入输出端口直接相连而被逆向工具恢复。因此,经本文方法混淆后,寄存器的分组信息完全被隐藏,寄存器组间拓扑复杂度也得到指数提升。

图9 SM4国密算法电路 抗逆向效果分析

4.2 混淆效率与面积评估

由于传统基于组合逻辑或有限状态机的逻辑混淆方法不会创建寄存器间的冗余连接,对于词级寄存器组逆向不具备混淆效果,因此,为了比较并评估本文混淆方法的混淆效率与面积开销,分别使用本文混淆方法、以及随机混淆方法对网表进行混淆,并进行逆向攻击。随机混淆方法随机地从网表中选取逻辑节点并创建冗余连接。如图10为逆向攻击结果的NMI值与面积开销的曲线图。面积开销通过植入的逻辑单元个数进行定量表征。混淆效率通过曲线斜率表征。

图10 面积开销与混淆效率分析

随着混淆开销的增加,NMI值不断降低,并最终逐渐收敛。对于随机混淆方法,当植入单元个数达到579时,NMI值逐渐收敛为0.65,面积开销为0.3874%;而本文方法在植入单元个数达到280时,NMI值收敛为0.54,面积开销为0.216%。可将本文方法混淆效率拟合为0.0016428/每单元,随机方法混淆效率拟合为0.0006045/每单元,因此本文方法效率为随机方法的2.718倍。同时如表1所示,相较于随机混淆方法,随着混淆效果的提升,本文方法的面积开销优势逐渐凸显。当NMI值为0.65时,本文方法面积开销为169,随机混淆面积开销为579,开销降低了70.8%。此外,对比两种方法的NMI收敛值,本文混淆方法相较于随机混淆方法下降16.9%,因而具有更好的的混淆效果。

表1 面积开销对比

4.3 性能开销评估

数字电路性能主要体现为电路可正常工作的最高时钟频率,其主要受限于电路中时序关键路径(即寄存器与寄存器间的延迟最大的连接通路)的延迟。延迟越高,电路最高时钟频率越低。在本文混淆方法中,混淆单元被植入原有的时序路径中,同时混淆单元也引入了新的时序路径。采用Design compiler或Primetime工具,对混淆后的门级网表进行时序分析。分析混淆单元对原始时序路径的影响,提取网表中含有混淆单元的时序关键路径:其中混淆单元延迟为0.42 ns,其余单元时序延迟为18.93 ns,则混淆单元对部分时序路径引入的时序性能开销最大为2.21%。

分析混淆单元引入的时序路径,当混淆密钥被赋值为正确值后,可等待多个周期再执行电路的正常功能,因此该时序路径并不影响电路运行的实际性能。在数字开发流程中,可以直接使用如宽松的多周期路径时序约束、或直接禁用该条路径的时序弧(timing arc),以禁止EDA工具分析优化该条路径的时序属性,从而避免该条路径的时序影响。

此外,针对文中算法的性能,随着电路规模的逐渐增大,基于建立时间对寄存器间的组合逻辑延迟的时序约束,电路规模的增加体现为寄存器组与组合逻辑云数量的增加,单个组合逻辑云的逻辑门数量规模不变。而本文提出的拓扑分析与混淆节点对筛选算法针对单个组合逻辑云进行逐个分析,因此随着电路规模的逐渐增大,本文算法的时间开销线性增加。

4.4 密钥安全性分析

逻辑混淆密钥,主要受到暴力攻击、故障敏化攻击与SAT攻击。暴力攻击通过穷举所有可能的密钥值并判断电路功能是否正常,从而获取正确密钥。而本文设计提出的每个混淆单元均可引入至少1 bit密钥,因此仅在100个逻辑门的硬件开销下,密钥搜索空间可达2100,不可接受的时间开销将使暴力攻击不再现实。

故障敏化攻击通过寻找特定输入模式,使单比特输出值的正确性只对单比特密钥敏感,从而根据单比特输出结果获取该比特密钥的正确值[18]。而本文方法通过创建寄存器拓扑网络的冗余连接,可明显提升密钥各比特间的相关性,从而使得各输出位均受多比特密钥值影响,指数提升攻击需要搜索的密钥空间。针对SM4电路进行实验,结果分析表明,当基于本文方法植入门数量为390时,各密钥输出节点的扇入路径中所存在的密钥比特数平均为43.49,最大值为180,因而能较好地抵抗故障敏化攻击。此外,当植入门数量为150时,随机混淆方案对应的密钥比特数平均值为10.62,本文混淆方法为24.08,相较于随机混淆方法提升1.27倍,因而相较于随机混淆,本文混淆方法在提升密钥相关度时具有更高的效率。

SAT攻击将求解组合逻辑电路密钥的问题视作求解布尔函数的可满足性问题,通过正确输入输出对迭代排除错误密钥集合,以最终获取正确密钥。针对时序逻辑电路,SAT攻击需通过创建电路副本展开时序反馈环路,从而将时序逻辑电路展开为等效的组合逻辑电路[19]。目前,如文献[7]等已提出了相关的基于时序逻辑混淆的不定时多次认证方案,可针对SAT攻击实现指数的安全性提升。然而,基于时序逻辑混淆的抗SAT攻击方案依然存在一定的不足之处。第一,流水线的电路结构可以被简化,从而降低SAT攻击需展开的时序周期轮数,缩减展开后电路的布尔函数复杂度与等效密钥位宽。而本文方法创建的冗余连接可引入大量时序反馈环路,从而破坏流水线结构特征。针对全流水线SM4加密电路的实验结果表明,在未经混淆的全流水线结构中不存在时序反馈环路,而经本文方法植入390个混淆单元后,除首末级外的共2048个寄存器中,2022个寄存器处于时序反馈环路中,流水线结构破坏比率为98.73%。第二,攻击者可基于状态寄存器恢复电路有限状态机[20],以获取解锁过程状态跳转路径对应的激励序列。而本文方法混淆了状态寄存器与数据寄存器,且引入的时序反馈环路将使得部分数据寄存器在混淆状态下并入状态寄存器反馈环路,消除了同组寄存器的相似性特征与扇入扇出特征,因而无法通过恢复电路有限状态机的方式攻破基于时序逻辑的混淆策略。如4.1节实验结果分析表明,在植入门数量为280时,寄存器网络拓扑复杂度提升61.46倍,NMI评估值下降46%,状态寄存器特征得到了有效混淆。

5 结束语

针对传统逻辑混淆方法无法混淆寄存器间拓扑关系的局限性,本文提出一种基于遗传算法的逻辑混淆方法,通过创建冗余连接,混淆词级寄存器相似性特征,从而抵抗网表逆向技术恢复RTL级词级Reg变量、控制逻辑与数据通路。针对SM4基准电路的实验中,本文方法使得逆向结果的正确度下降46%,拓扑复杂度提高61.46倍,开销仅为0.216%。同时,相较于随机混淆方法,本文方法混淆效率提升为2.718倍,面积降低70.8%,因此能为超大规模芯片在低面积开销水平下提供有效的网表逆向防护。