微光像增强器纳秒级荧光屏余辉时间测试系统

2022-12-06陈益新姜云龙苏天宁刘倍宏钱芸生

卢 杰,常 乐,陈益新,姜云龙,苏天宁,刘倍宏,赵 航,钱芸生,刘 健

(1. 南京理工大学 电子工程与光电技术学院,江苏 南京 210094;2. 北方夜视技术股份有限公司,云南 昆明 650217;3. 南京美乐威电子科技有限公司,江苏 南京 210094)

引言

微光夜视技术[1-3]是当代拓宽人类裸眼有效视力的主要技术之一,其主要核心器件为微光像增强器。微光像增强器的主要功能是完成入射电子的倍增,使原来观察不清晰的辐射图像转化为人眼可以清晰分辨的辐射图像。自第一代像增强器问世以来,像增强器便得到快速发展,发展方向主要包括提高光电阴极的灵敏度[4]、增强微通道板的增益[5]及研究荧光屏的时间特性[6]等。荧光屏作为夜视技术中显示部分的重要一环,其时间特性是评判像增强器质量的重要指标之一。日前英国PHOTEK 公司[7]设计出一款全新像增强器,该像增强器最大优势在于具有超快光学现象的特点,荧光屏余辉时间达80 ns,属于超快光学时间范畴。在国内,微光夜视技术国防科技重点实验室也在积极研究基于P47 荧光粉的具有超快光学特征的像增强器。目前,我国颁布实施的国军标通用规范荧光屏余辉试验方法主要有2 种方式[8-11]:第1 种是控制光源的发射,通过控制光源的通断来控制荧光屏的亮度情况;第2 种是控制像增强器中光电阴极的门控脉冲电压,通过控制门控脉冲电压实现光源的通断。然而,以上2 种方案均存在器件响应速度过慢的问题,在测量超快光学器件时均具有一定局限性,无法准确测量纳秒量级的荧光屏余辉时间。

针对目前现有的荧光屏余辉时间测试技术还不足以测试此类像增强器的现象,本文基于传统的荧光屏余辉时间测试方案,利用响应速度极快的信号发生器产生光源信号,结合FPGA[12-13]优异的高速数据处理性能,利用Visual Studio 软件开发平台对采集到的数据完成数据处理,以及对各仪器实现程序控制,设计一套可以测量超快光学特征的像增强器荧光屏余辉时间测试系统,并对该测试系统进行实验,验证了该测试系统的可行性。

1 测试系统组成及工作流程

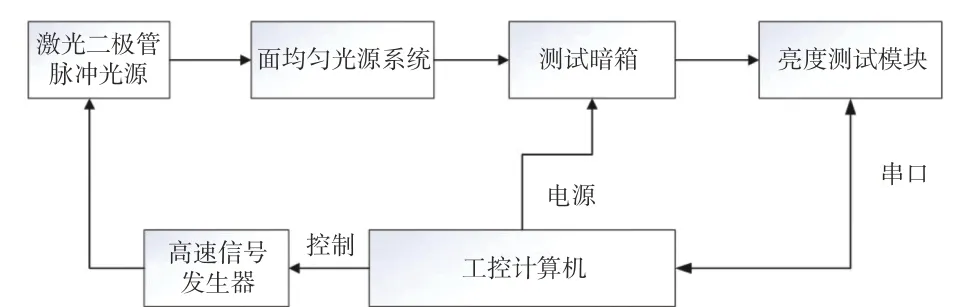

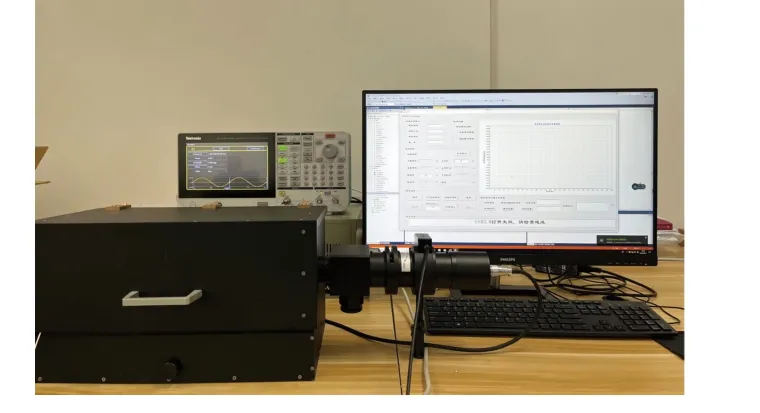

荧光屏快速余辉时间测试系统主要由激光二极管脉冲光源、高速信号发生器、面均匀光源系统、测试暗箱、亮度测试模块、工控计算机组成。图1 为荧光屏快速余辉时间测试系统结构框图,图2 为荧光屏快速余辉时间测试系统实物图,图3为暗箱内部结构实物图。

图1 荧光屏快速余辉时间测试系统结构框图Fig. 1 Structure block diagram of rapid afterglow time test system for fluorescent screen

图2 荧光屏快速余辉时间测试系统实物图Fig. 2 Physical drawing of rapid afterglow time test system for fluorescent screen

图3 暗箱内部结构实物图Fig. 3 Physical drawing of rapid afterglow time inner structure of camera obscura

其具体工作流程为:工控计算机通过控制高速信号发生器驱动激光二极管光源产生符合测试条件的光脉冲,光脉冲经过面均匀光源系统后传递至暗箱,暗箱中放置待测像增强器,直流稳压电源用于给像增强器整管及负责荧光屏光信号采集的光电倍增管提供3 V 和5 V 的工作电压,荧光屏上的亮度信号输入亮度测试模块中,工控计算机通过发送指令的形式向亮度测试模块中索要荧光屏亮度信息,经过数据处理和分析等过程,最终在上位机中显示余辉曲线图像,计算出待测像增强器的荧光屏余辉时间。

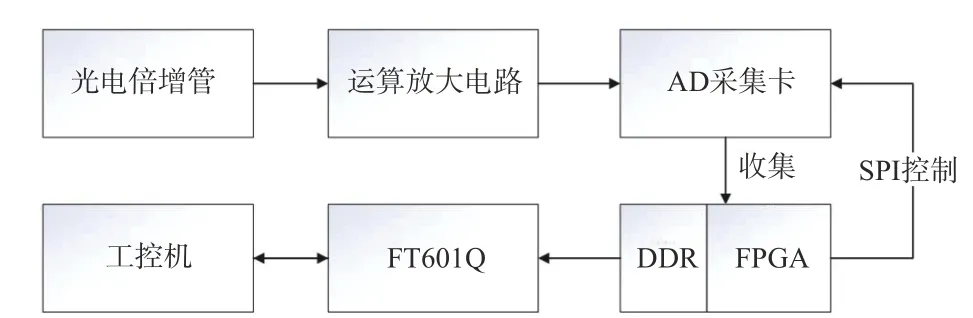

2 基于FPGA 的亮度信息高速采集硬件设计

为提高数据的采集速率,增加数据采集的工作效率,研制了基于FPGA 的荧光屏亮度信息高速采集模块,其整体结构图如图4 所示,实际硬件图如图5 所示。模块的主要硬件电路包括光电倍增管采样电路、放大及单端转差分电路、A/D 转换电路、高速采集与传输控制电路、USB3.0 接口电路。光电倍增管采样电路基于日本滨松H10720 型号的光电倍增管进行设计,其下降时间仅为0.57 ns,可在很大程度上降低纳秒级余辉过程的测量误差。放大电路采用LTC6229 芯片,能够完成对μA量级的微弱光电流信号的20 倍放大,为满足进入AD 的输入模式,使用ADI4939 芯片完成电信号的单端转差分过程。A/D 转换电路采用AD9684 芯片,其采样率高达500 M,可以实现对荧光屏亮度信号的高速采集。在FPGA 的控制下,荧光屏亮度模拟信号首先被光电倍增管采集完成光电转换,转换为微弱的电流信号,电流信号经过放大及单端转差分电路,进入A/D 转换模块进行模数转换,得到数字信号后与FPGA 的BANK 口相连进入FPGA内部。

图4 亮度测试模块具体结构框图Fig. 4 Structure block diagram of luminance test module

图5 亮度测试模块硬件图Fig. 5 Hardware physical drawing of luminance test module

高速采集与传输控制电路的设计主要集中在FPGA 上,FPGA 的主要作用是在ADC 芯片和USB3.0 之间形成有效的缓冲和控制,将ADC 接口与USB3.0 接口进行连接,并实现数据的采集、缓存、传输等功能。FPGA 通过外扩DDR4 SDRAM存储器,单片存储容量大小为512 MB,可以保存采集到的临时数据。之后,通过上位机发出的指令需求,数据通过USB3.0 高速传输接口传递至PC中,在PC 上进行数字信号处理,最终获取荧光屏余辉曲线。

3 荧光屏快速余辉时间测试系统软件设计

为方便实现对各个仪器的程控目的,荧光屏快速余辉时间测试系统选用的软件平台是基于Visual Studio 2013 开发环境,利用MFC(microsoft foundation classes)编写而成的。通过MFC 程序设计,实现了在一个操作界面内完成数据采集、荧光屏余辉数据处理、测试结果显示、测试设置、测试结果保存等功能,其程序界面如图6 所示。

图6 荧光屏快速余辉时间测试系统程序界面Fig. 6 Program interface of rapid afterglow time test system for fluorescent screen

3.1 亮度信号的卡尔曼滤波去噪算法[14]

荧光屏亮度数据通过USB3.0 高速传输协议到达上位机中,但由于信号在传输过程中伴随着巨大的电磁噪声干扰,这些电磁噪声干扰会对荧光屏的余辉过程造成误判,因此需要对通过USB3.0传输的荧光屏亮度数据进行滤波操作。通过分析数据噪声的特性可知为随机噪声,且服从高斯分布,同时亮度信息存在一定的变化趋势,故采用卡尔曼滤波算法对荧光屏亮度数据进行滤波操作。该算法的原理是,通过观测值与理论实际数据融合得到当前最佳预估值。滤波包含2 个阶段,预测阶段和更新阶段。预测阶段根据前一时刻的状态估计值推算当前时刻的状态变量先验估计值和误差协方差先验估计值;更新阶段负责将先验估计值和新的测量变量结合,构造改进的后验估计值作为滤波后的数据结果,其算法迭代图如图7 所示。

图7 卡尔曼滤波算法迭代图Fig. 7 Iteration diagram of Kalman filtering algorithm

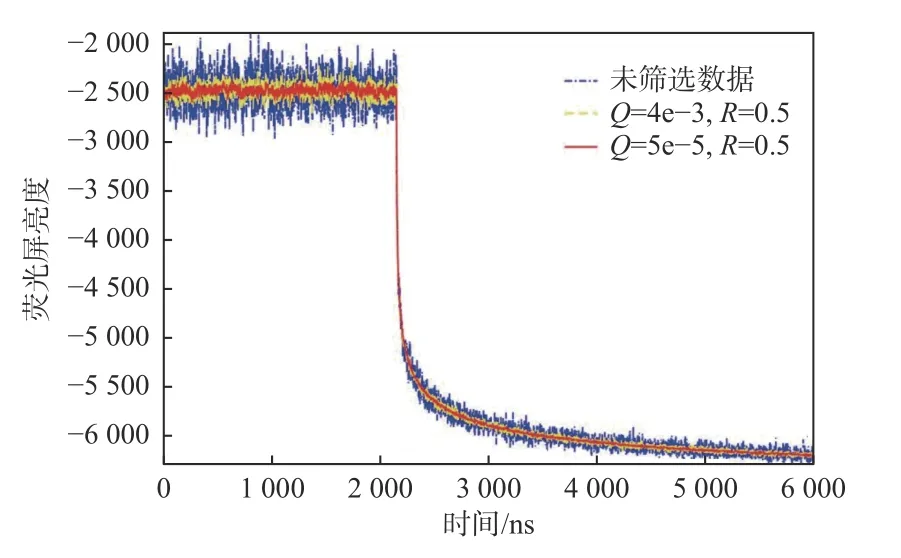

在算法中需要对2 个参数进行调整,分别为Q和R,其含义分别为过程噪声协方差值和测量噪声协方差值。两值的取值不同,则代表对模型预测值和实际测量值的权重不一致,会对卡尔曼滤波效果产生不同程度的影响。经过不同参数取值的卡尔曼滤波示意图如图8 所示。

图8 不同参数值的卡尔曼滤波示意图Fig. 8 Schematic diagram of Kalman filter with different parameter values

3.2 亮度信号收集过程

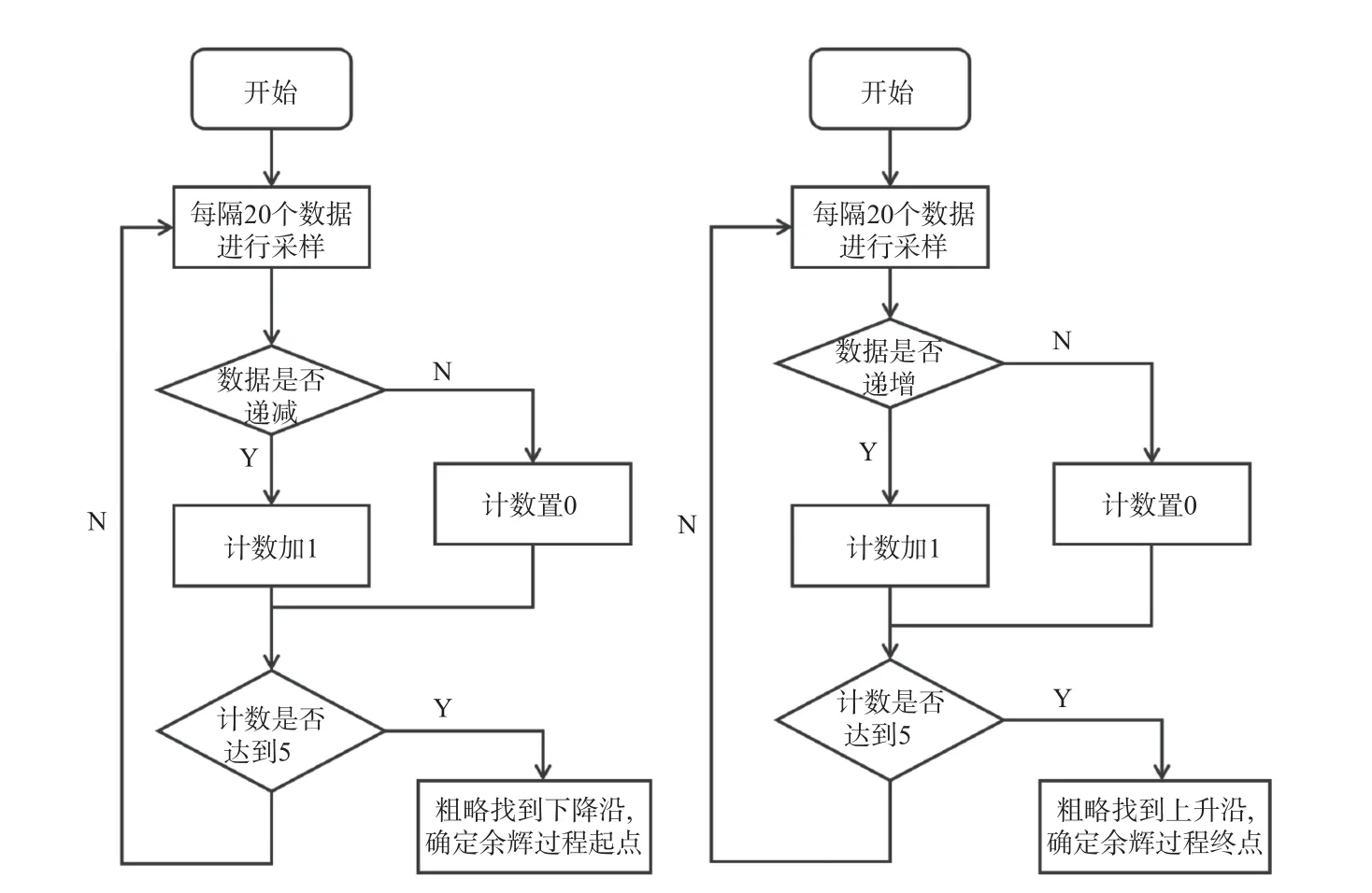

由于数据在一个周期内数量十分巨大,因此在上位机上不能直接显示。为清晰描述待测像增强器的荧光屏余辉过程,选取亮度数据在一个周期内的跳变沿进行收集。为提高测试系统的测试时间,提出一种基于降采样的快速寻找跳变沿算法,具体算法流程图如图9 所示。

图9 基于降采样的快速寻找跳变沿算法流程图Fig. 9 Flow chart of fast finding jump edge algorithm based on downsampling

对采集到的数据通过降采样方式每隔20 个数据进行遍历,若遍历的连续5 个数据均呈现出单调递减趋势,则认为此时已经进入了余辉过程,从而确定余辉过程起点,同理可以获取到余辉过程终点。将余辉过程的数据保存到在堆区创建好的数组单元内,通过遍历方式得到当前余辉过程的最大值与最小值点。根据GJB 7351-2011《超二代像增强器通用规范》[15]中对待测像增强器余辉时间的测量规定—“脉冲激励停止后荧光屏的亮度下降到停止激励的10%所经历的时间”,从而可以将余辉曲线显示在上位机中,并计算出余辉时间。

4 测试结果与分析

4.1 测试参数选择

实验所选取的光源属高速激光二极管光源,其发出的光为绿光,波长为520 nm,正常工作时功率为10 mW,实验前为满足GJB 7351-2011《超二代像增强器通用规范》中对于荧光屏余辉测试的照度条件,对光功率计进行标定,设定信号发生器的高电平电压在1.70 V~1.80 V 可调。

测试系统中所用的高速信号发生器选取Tektronix 公司型号AFG31251 的信号发生器,该发生器工作频率为250 MHz,可产生至少周期为4 ns 的脉冲方波。为了满足测量超快像增强器余辉时间的需求,利用该高速信号发生器产生一脉冲方波,用于驱动激光二极管发光,可尽量减小因光源自身响应速度太慢造成的对荧光屏余辉时间测量上的误差。设定脉冲方波的上升时间和下降时间均为高速信号发生器所能设置的最小值。设该脉冲方波的参数为:频率100 kHz,振幅1.70 V~1.80 V 可调,占空比50%~90%可调,上升时间与下降时间均为2 ns。该脉冲方波的具体参数如表1 所示。

表1 高速信号发生器产生信号参数设置Table 1 Signal parameter setting of high-speed signal generator

4.2 测试流程

本文对微光夜视技术国防科技重点实验室研制的超快像增强器进行余辉时间测试。像增强器荧光屏上的荧光粉基质由P47 荧光粉组成,理论余辉时间达到100 ns,用一般的余辉测试设备无法准确测量其余辉时间。

在实验开始前打开高速信号发生器开关、FPGA 电源开关和直流电源开关,其中直流电源需要给像增强器、光电倍增管、光电倍增管增益电路、光阑供电,通过上位机设置高速信号发生器相关参数驱动激光二极管。在上位机中创建512 MB的数据空间,用于对高速数据进行采集,经上位机发出收发指令后,接收来自DDR4 缓存的数据,在Visual Studio 上完成数据滤波及寻找下降沿过程,将余辉曲线图像显示在上位机上,获取待测像增强器的荧光屏余辉时间。

为减少电路上的噪声对实验结果造成干扰,共采集150 个下降沿过程进行余辉时间计算,最终取这150 个下降沿余辉时间的平均值作为当前测试条件下待测荧光屏余辉时间。

实验前为排除光源及硬件电路对测试余辉时间造成的影响,最初在暗箱内部不放置像增强器,在上位机端采集此时的亮度数据信号,获取到基础的下降沿时间。

4.3 结果分析

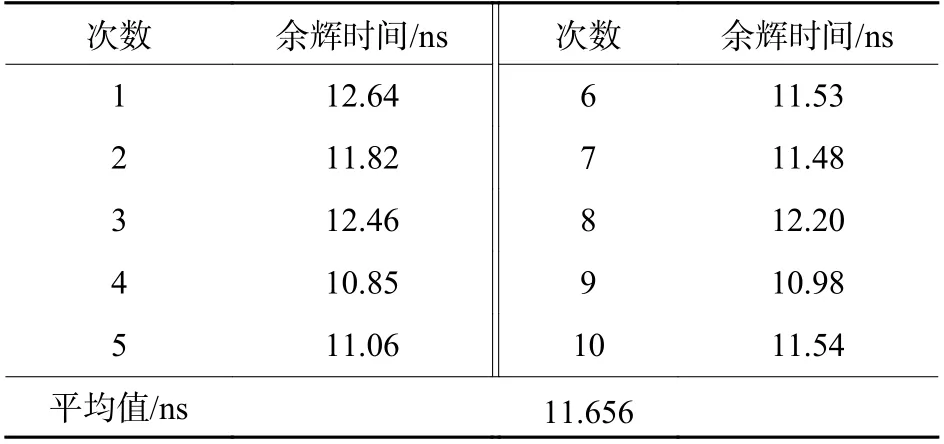

测试首先在占空比为60%,高电平电压为2.20 V,光电倍增管增益电压为0.90 V,不加入像增强器的条件下连续测试10 次,得到的余辉测试结果如表2所示,余辉下降曲线如图10 所示。

表2 空管条件下的光源余辉测试结果Table 2 Test results of light source afterglow under emptytube conditions

从表2 和图10 中可以看出,激光二极管发出的光信号在经过亮度信息高速采集硬件后,存在平均时间为11.656 ns 的下降沿时间,这个下降沿时间会对加入像增强器后采集到的余辉时间造成一定影响。

图10 空管条件下光源余辉曲线Fig. 10 Afterglow curve of light source under empty-tube conditions

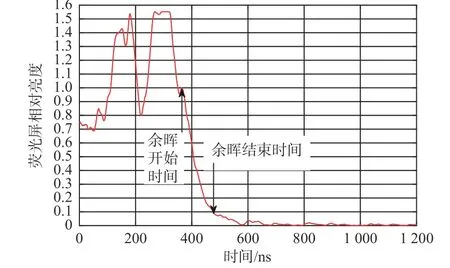

随后在占空比为60%,高电平电压为1.75 V,光电倍增管逐级增益电压为0.70 V 情况下连续测试10 次,得到的余辉测试结果见表3 所示,余辉曲线如图11 所示。

表3 单一模式下的余辉测试结果Table 3 Afterglow test results in single mode

图11 荧光屏余辉曲线示意图Fig. 11 Schematic diagram of afterglow curve of fluorescent screen

从表3 和图11 可以看出,待测像增强器的荧光屏余辉测试时间大致在113 ns~123 ns 区间之内,计算出余辉时间平均值为118. 094 4 ns,重复度为2.08%,证实了该测试系统具有较强的测试稳定性,可以相对精确地测量出具有超快光学特征的像增强器特性。

结合图11 与图10 余辉曲线可以看出,由于电路板及光源自身存在下降沿问题,导致即便不添加像增强器情况下,也会造成平均时间11.656 ns 的下降沿时间,这个下降沿时间会反映在将待测像增强器添加至暗箱中的测试结果上。根据表3 的测试结果可以看出,单一模式下测试得到的P47 荧光屏余辉时间,基本满足P47 荧光屏余辉理论时间与光源及电路本身的固有下降沿时间之和。

关于单一模式下余辉测试结果不稳定的原因,主要是信号在传递过程中,在亮度测试模块硬件中存在噪声过大导致的。由于在放大电路端为尽可能减少电容带来的充放电时间的延时作用,将电路板中绝大部分电容拆去,这虽然减少了亮度测试模块带来的下降沿延时时间,但也保留了原来信号的噪声特性,因此反映在图10 中,亮度信号在光源关闭前存在大幅振荡的情况,这也证实了表3 中单一模式下余辉测试结果不稳定的原因。

为验证测试系统在不同条件下的稳定性,改变信号发生器输给光源的高电平值,以改变光电阴极面上的辐照度及改变光电倍增管的增益电压,然后对P47 荧光屏重新进行测试。将光电倍增管的增益电压调整至0.68 V 和0.72 V 重新进行测试,测试得到的荧光屏亮度曲线如图12 所示。

图12 不同增益电压下荧光屏亮度曲线示意图Fig. 12 Schematic diagram of luminance curves of fluorescent screen under different gain voltages

从图12 中可以看出,对光电倍增管的增益采取不同的电压后,信号的波形在进入余辉过程之后呈现出相同的趋势,通过计算算出在3 种不同驱动电压下荧光屏余辉时间为106 ns、110 ns、106 ns,均较准确地测量出待测像增强器的荧光屏余辉时间,证实了本测试系统的测量值不受光电倍增管增益的影响,具有良好的稳定性。

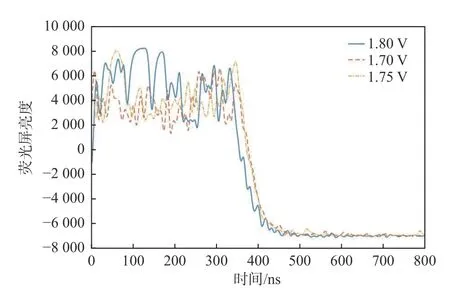

固定光电倍增管的逐级电压为0.70 V,对信号发生器施加不同的高电平电压,改变光源的辐射强度,随之改变阴极面的辐射照度,对像增强器重新进行测试,测试得到的荧光屏亮度曲线如图13所示。

图13 不同光源强度下荧光屏亮度曲线示意图Fig. 13 Schematic diagram of luminance curves of fluorescent screen under different light source intensities

从图13 中可以看出,对信号发生器施加不同的高电平电压,改变光源的辐射强度后,荧光屏亮度信号的下降趋势均相同,通过计算算出在3 个不同高电平电压下荧光屏余辉时间为112 ns、120 ns、116 ns,均较准确地测量出待测像增强器的荧光屏余辉时间,证实了本测试系统的测量值不受光源辐射强度的影响,具有良好的稳定性。

5 结论

针对当前缺乏超快余辉测试技术问题,本文基于传统荧光屏余辉时间的测试方法,设计了一套可以测试像增强器纳秒级余辉时间的测试系统,实现了荧光屏亮度信息高速采集、存储、传输、余辉时间计算、保存余辉时间等多项功能。在设置信号发生器占空比60%、高电平电压1.75 V,光电倍增管增益电压0.70 V 的工作条件下,对微光像增强器纳秒级荧光屏余辉时间连续测试了10 次,可达到118. 0944 ns,重复度为2.08%。此外,通过改变光电倍增管增益电压和光源电压大小,获得了相应的荧光屏亮度曲线示意图。测试结果表明,改变外界条件不会影响待测像增强器的荧光屏余辉时间,证实了该测试系统具有良好的稳定性,从而为测试具有超快光学特征的像增强器的荧光屏余辉时间提供了一种有效手段。