基于ZYNQ处理器的EtherCAT从站通信系统设计

2022-12-02王成杰史世友付建国

李 益,王成杰,史世友,付建国

(中车株洲电力机车研究所有限公司,湖南 株洲 412001)

0 引言

随着工业领域自动化程度的加深,普通现场总线通信速率已达瓶颈,无法满足工业控制系统对现场总线的需求。风电领域常用CANopen现场总线,其通信速率最高为1 Mbit/s,每帧数据为8个字节,存在通信速度慢和传输数据量小的问题,无法满足风电领域更高的现场通信实用性需求。目前工业控制领域现场总线技术开始向实时以太网的方向发展。相较于常规现场总线,实时以太网具有成本低、带宽大、通信速率快、安全性高及抗干扰能力强等优势。Modubus/TCP,Ethernet/IP,EtherCAT,Ether-net PowerLink,EPA,PROFINET IRT和SERCOS III是较常用的工业实时以太网技术。其中,EtherCAT具有高速、高有效数据率和低延时的特点,其网络拓扑结构灵活,且在协议中封装了IP/UDP,不需要IP协议就能实现通信,适应性强,因此受到广泛的关注。

EtherCAT由一个主站设备和多个从站设备组成[1]。传统以太网通信需要主站和从站不停地收发数据,EtherCAT与之不同,其使用相同的物理和数据链路层。EtherCAT中,主站是唯一允许发送帧的节点,子站只能转发帧;数据帧就像火车一样,从主站开出,途经各个子站,把对应子站的数据放下或者带上,最后回到主站。这种方法有助于确保操作的实时性并避免延迟,从而满足工业领域低延时、高响应需求。主站设备使用标准的以太网控制器,具有良好的兼容性,任何具有网络接口的计算机和具有以太网控制功能的嵌入式设备都可以作为EtherCAT的主站[1],因此,通信系统设计的核心在于从站的设计。目前,从站的实现方式一种是在现场可编程逻辑门阵列(field programmable gate array,FPGA)中集成IP-Core,这需要在控制器上新增FPGA芯片;另一种是在微处理器芯片内实现EtherCAT从站功能,此方式虽然硬件集成度高,但软件实现复杂、开发周期长。本文选用LAN9252型芯片作为从站控制芯片实现EtherCAT数据链路层协议来处理EtherCAT数据帧,为从站控制器提供数据接口[2]。从站微处理器核心芯片选用ZYNQ7000型芯片来解析通信信息、实现设备控制[2],同时采用VxWorks实时操作系统来构建嵌入式平台,以实现高实时性通信。该方案针对不同领域,可通过更换微处理器方式实现EtherCAT从站的快速移植。太网电缆或光缆,采用以太网全双工通信技术构成主从站通信方式。

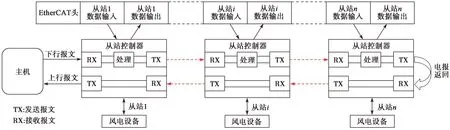

EtherCAT系统运行原理如图1所示,其主要步骤如下:

图1 EtherCAT系统原理Fig.1 Schematic diagram of EtherCAT system

(1)EtherCAT通信由主站发起,主站发出一包数据帧依次传输到各个从站;

(2)各从站监测到数据帧后,从主站分配给它的数据帧偏移地址处读取数据,将其待发送数据装载到数据帧上,并标识该从站已处理该报文;

(3)当网络中最后一个从站节点处理完数据帧后,将数据帧转发回主站,主站捕获返回的数据帧并对其进行处理,从而完成一次通信过程。

在该系统中,完成一次数据帧传输大概需要几纳秒时间,弥补了传统以太网系统因先对数据包进行解析再复制成过程数据而造成通信效率低的缺陷。

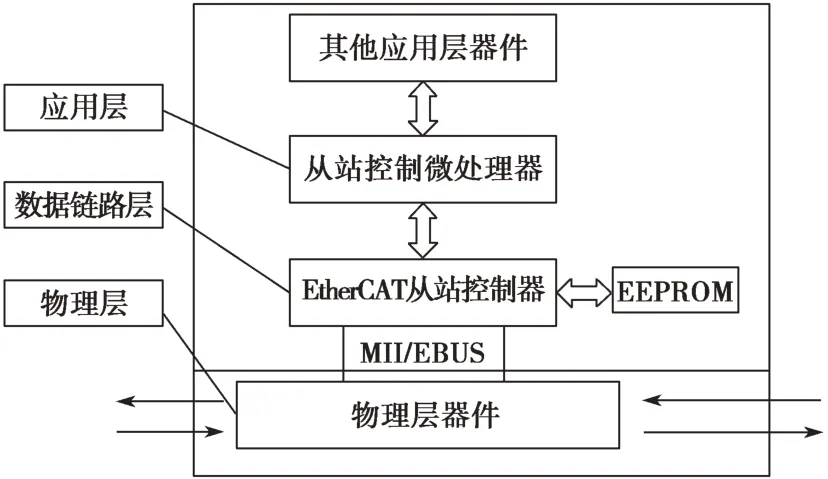

2 EtherCAT从站硬件设计

EtherCAT从站硬件主要由从站微处理器和从站控制器等组成(图2)。本文采用ZYNQ7000型芯片作为从站微处理器,其负责实现应用层功能;采用EtherCAT协议栈芯片LAN9252实现数据链路层与物理层之间的数据交互。LAN9252从站物理层接口有MII和EBUS两种,其中MII接口是标准的以太网物理层接口,EBUS是倍福公司定义的数据传输标准接口。

图2 EtherCAT从站系统框图Fig.2 Block diagram of EtherCAT slave system

1 EtherCAT简介

EtherCAT是一种以以太网为基础的开放架构的现场总线系统,其可以支持线形、树形和星形设备连接拓扑结构,物理介质可以选100Base-TX标准支持的以

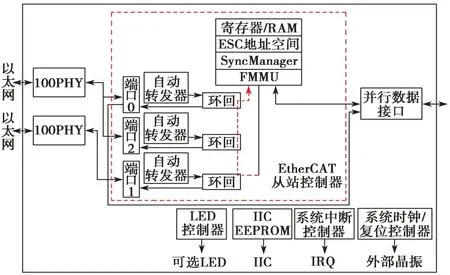

2.1 EtherCAT从站控制器

本文中EtherCAT从站控制器采用LAN9252型芯片,其集成了两个以太网物理层(physical layer,PHY),具有3个端口;每个以太网PHY包含一个全双工100BASE-TX收发器且支持100 Mbit/s(100BASETX)工作速率[2](图3)。LAN9252包括一个EtherCAT从控制器,此控制器具有4 kB双端口存储器(DPRAM)和3个现场总线存储器管理单元(FM‐MU)[2],每个FMMU均执行将逻辑地址映射到物理地址的任务。EtherCAT从控制器还包括4个存储管理通道,允许在EtherCAT主器件和本地应用之间进行数据交换[2]。每个存储管理通道提供缓冲模式和邮箱模式两种。在缓冲模式下,从站微处理器和EtherCAT主器件可同时写入数据。LAN9252中的缓冲区始终包含最新数据。如果新数据在旧数据被读出前到达,则旧数据将丢失。在邮箱模式下,从站微处理器和EtherCAT主器件通过握手方式来访问缓冲区,从而确保不会丢失任何数据[3]。

图3 LAN9252内部结构Fig.3 Internal structure of LAN9252

2.2 从站硬件接口设计

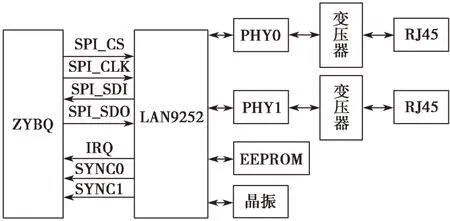

本设计的从站微处理器采用ZYNQ7000型芯片,其核心集成了ARM双核Cortex-A9处理器以及FPGA全可编程硬件,运行速率高达1 GHz;且具有512 kB L2高速缓存和256 kB片上存储器,可容纳整个实时操作系统。该处理器提供了搭建EtherCAT从站所有必要的通信接口。LAN9252的过程数据接口(process data inter‐face,PDI)一般是通过并行IO接口或串行外设接口(serial peripheral interface,SPI)两种方式而实现的。

本设计采用SPI接口与LAN9252通信,其硬件接口如图4所示。LAN9252的IRQ引脚被连接至ZYNQ7000的外部中断引脚。由于LAN9252通过SYNC0和SYNC1引脚为从站提供精确的同步脉冲,因此也需将SYNC0和SYNC1引脚连接至ZYNQ7000模块的外部中断引脚。

图4 从站硬件接口图Fig.4 Interface diagram of the slave hardware

3 Ethercat从站软件设计

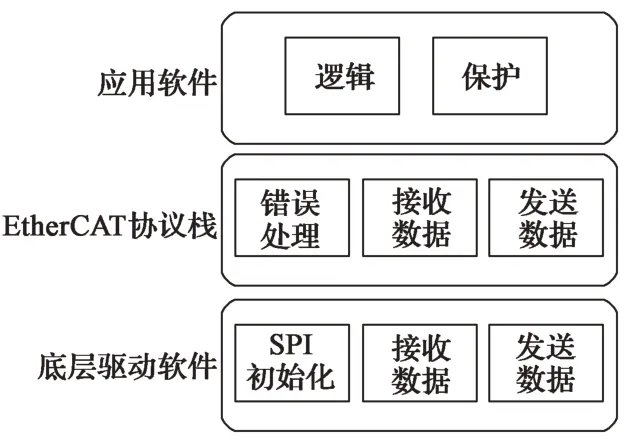

EtherCAT从站软件主要分为底层驱动软件、Ether‐CAT协议栈以及应用层(图5)。驱动层提供所有硬件的驱动函数,主要完成ZYNQ7000与LAN9252之间的数据交互。EtherCAT协议栈实现主从站之间的数据交互,通过配置存储在EEPROM存储器中的EtherCAT从站控制器(EtherCAT slave controller,ESC)模块配置文件实现该功能。应用层软件主要由微处理器完成协议解析和数据处理等工作。

图5 从站软件架构Fig.5 Architecture diagram of the slave software

3.1 软件架构设计

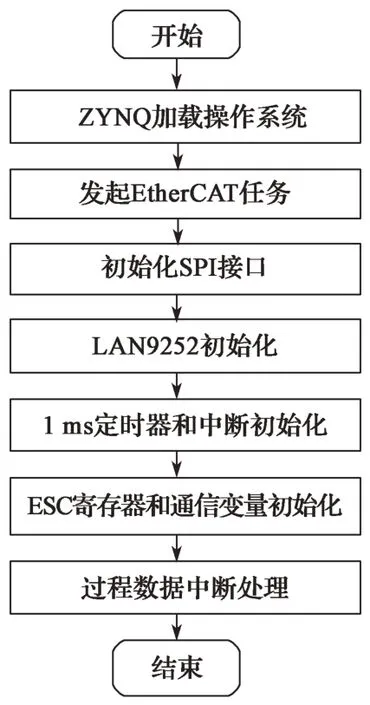

采用ZYNQ7000型微处理器作为EtherCAT从站控制器,其与从站控制芯片LAN9252采用SPI通信进行数据交互。ZYNQ7000首先进行SPI通信初始化,再对LAN9252中ESC寄存器进行初始化以及通信状态机处理,以便完成通信初始化,最后配置好周期性数据的处理逻辑,进行过程数据通信,进而满足应用层协议的需求。软件框架流程如图6所示。

图6 软件框架流程Fig.6 Flow chart of the software framework

3.2 SPI通信接口设计

LAN9252寄存器分为直接寻址寄存器和间接寻址寄存器。直接寻址寄存器分为系统控制和状态寄存器、过程数据RAM访问寄存器。间接寻址寄存器分为PHY寄存器和EtherCA T内核控制状态寄存器(control and status register,CSR)。

访问直接寻址寄存器的读写操作如下:

(1)读处理以每个时钟1位的方式输入指令代码和字节地址,并以每个时钟1位的方式输出数据。其首先将使能信号置为有效,接着写入读指令(03H),后面跟两个地址字节(低地址在前,高地址在后),最后输出该寄存器内容。

(2)写处理以每个时钟1位的方式输入指令代码、地址和数据字节。首先写入写指令(02H),其后跟两个地址字节,该地址字节用于指定器件内的字节地址,地址字节后跟数据(32位数据)。

对于LAN9252寄存器的读写操作,首先必须完成SPI对字节顺序的测试,如果回读到返回值为“0x87654321”,即可认为接口处于正确工作状态。

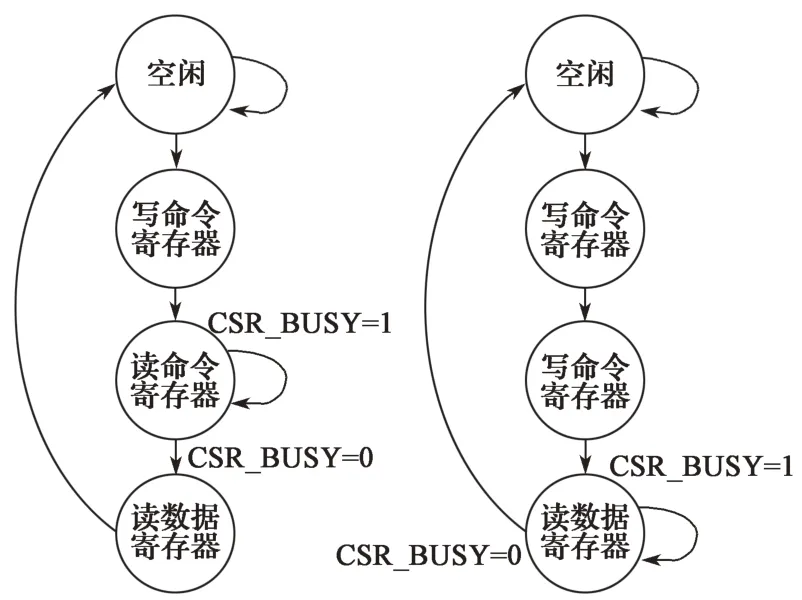

访问EtherCAT间接寻址寄存器,必须通过以下方式进行读写操作:首先将CSR接口命令写入寄存器(0x304H);接着将CSR地址字段设置为所需寄存器地址;最后将CSR大小字段设置为所需大小,若将读写位“置1”,则完成读周期,若将读写位清零,则完成写周期,具体如图7所示。

图7 间接寻址读写流程Fig.7 Indirect addressing read and write process

3.3 EtherCAT协议栈设计

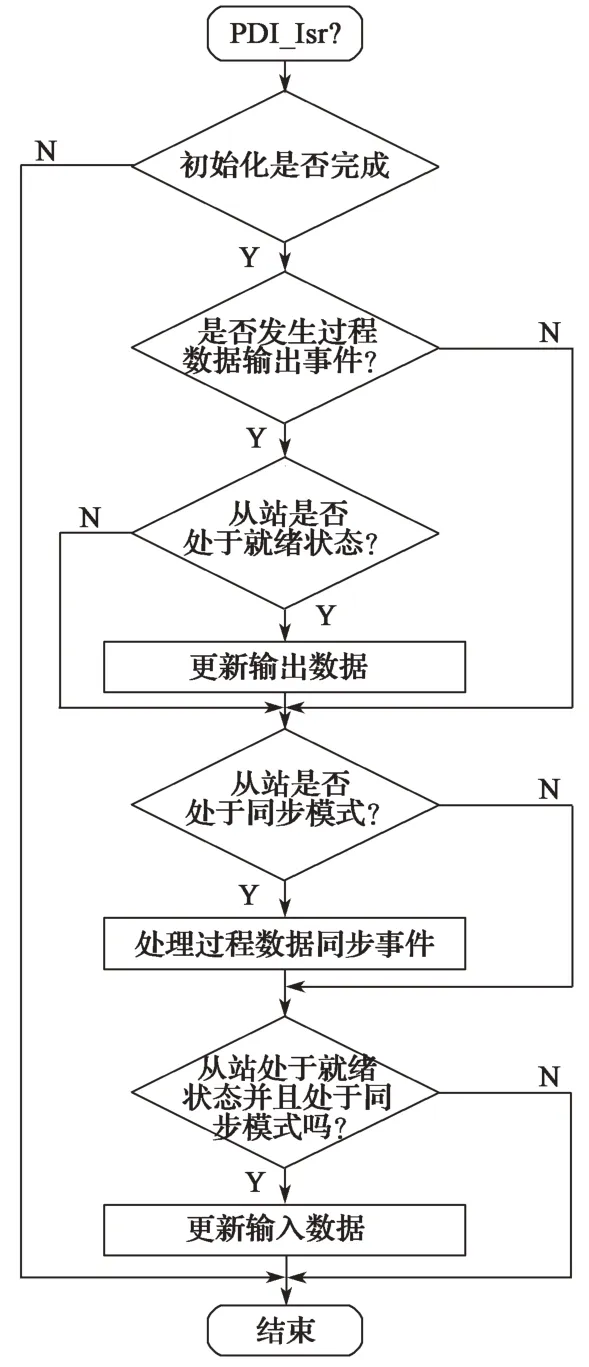

协议栈驱动软件主要完成EtherCAT数据的接收和发送以及错误处理任务。在过程数据处理中,检查本地计时寄存器,采用VxWorks辅助定时器sysAux‐ClkRateSet进行1 ms定时,用于检查EtherCAT看门狗时间,以便实现多从站节点通信同步。PDI_Isr中断函数是整个从站设计的关键,也是开发应用程序的主要目的,用于与主站进行信息交换并进行数据处理,实现从站命令所要求的功能。当从站处理器检测到有过程数据输入时,触发该中断。进入中断后,首先判断初始化是否完成,若完成,则判断应用程序是否触发过程数据输出事件,若条件满足,再判断从站是否处于就绪状态,若该条件也满足,则向主站发送数据,完成数据发送流程;接着再判断从站是否处于同步模式,若条件满足,则处理过程数据同步事件,再判断从站是否处于就绪状态,若条件满足,则接收主站下发数据,完成数据接收流程。收发数据流程如图8所示。

图8 收发数据流程Fig.8 Flow chart of sending and receiving data

4 系统测试

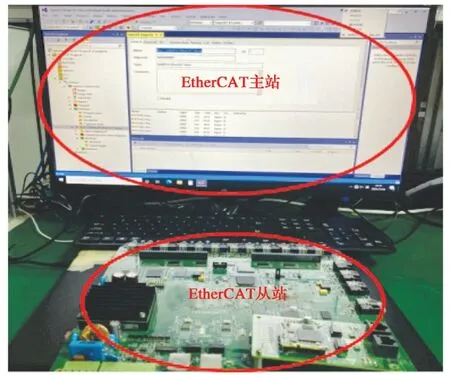

为了验证本设计EtherCAT从站控制系统的可行性,搭建了一主一从网络测试系统。主站是一台装有EtherCAT测试软件的PC机,从站为搭载LAN9252从站控制芯片的风电主控板,PC机与所设计的从站控制器通过以太网网线相连,从而构成主从站系统,如图9所示。在此环境中,分别进行了通信周期为1 ms,5 ms和10 ms的通信测试,以验证该EtherCAT从站控制系统的实时性和稳定性。

图9 测试平台Fig.9 Testing platform

在EtherCAT测试软件上先扫描EtherCAT器件,扫描成功后运行测试软件,确认主站运行状态正常后,开始填写主站发送数据,同时接收从站数据。

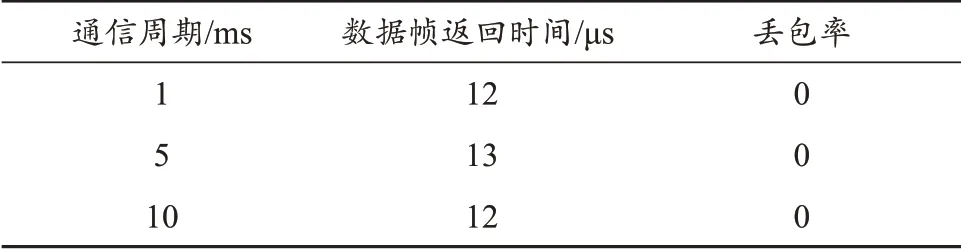

使用网络封包分析软件测试数据帧传输时间,从抓取报文分析可知,相邻两帧报文分别为主站发送报文和从站响应报文,相邻两报文时间间隔即为通信响应周期;通过对抓包30 000帧数据进行统计分析,结果如表1所示。3种通信周期下从站响应周期大约为12μs,均未超过20μs。由此可知,该EtherCAT从站系统通信响应速度快、实时性强,满足风电领域通信需求。

表1 EtherCAT从站系统测试结果Tab.1 Test results of the EtherCAT slave system

在上述3种通信周期下,利用EtherCAT测试软件主站监测从站实时状态的功能,监测通信过程中发送帧、丢包帧、发送/传输错误数。对3种通信周期,均监测30 000个数据帧,测出系统的丢包率均为0,由此可知,该EtherCAT从站系统通信稳定性高。基于此测试结果,最终配置的EtherCAT通信周期为3 ms,数据量为360字节,满足目前风电领域通信需求。

5 结语

为了解决风电领域CANopen现场总线运行速率慢和传输数据量小的问题,本文设计了一种微处理器ZYNQ7000搭载EtherCAT从站控制器LAN9252的EtherCAT数据通信从站系统,并针对过程数据处理进行了软件驱动解析。搭建了测试系统对该从站通信系统进行测试,结果显示,该从站系统通信稳定性高、实时性较强、通信周期短且数据量大,通信周期由原来的10 ms缩短到3 ms,通信数据量由96字节扩充到360字节,更好地满足了风电领域通信需求。本研究目前只完成了单EtherCAT从站节点系统的搭建和性能测试,后续将针对多节点EtherCAT组网系统的通信实时性和稳定性等特性进行研究。