基于双极工艺的高速MOSFET栅驱动电路

2022-10-29邱旻韡屈柯柯李思察

邱旻韡,屈柯柯,李思察,郭 刚

(1.中国电子科技集团公司第五十八研究所,江苏无锡 214035;2.中国原子能科学研究院,北京 102413)

1 引言

功率集成电路是集成电路中非常重要的一类。目前常用的功率器件主要有3种:双极型晶体管、金属-氧化层-硅-场效应晶体管(MOSFET)以及绝缘栅双极型晶体管(IGBT)。双极型晶体管性能较差,已不是主流的功率器件;IGBT虽然性能优良,但是价格较高;而MOSFET在性能和价格方面做到了很好的平衡,应用最为广泛。目前,功率MOSFET的驱动电路主要采用互补金属氧化物半导体(CMOS)工艺实现[1-4]。在高压功率驱动电路中,采用CMOS工艺实现功率驱动电路中的驱动器件时,高压MOSFET器件的阈值电压较高,导致器件的导通电阻较大,器件的导通损耗较大。当驱动电路长时间工作时,较大的导通损耗会增加驱动电路的温升,降低器件的工作寿命。与此同时,被驱动的功率MOSFET器件寄生电容较大,栅极-漏极寄生电容还要考虑密勒效应,导致寄生电容进一步增加。为了高速驱动功率MOSFET器件,驱动电路的高侧/低侧驱动器件必须能够瞬间输出大电流,但是MOSFET器件输出电流与器件栅极-源极电压的平方成线性关系,因此器件输出跨导的效率不高,为了能够提高驱动速度,驱动器件面积都较大,这会增加驱动电路的芯片面积,抬高经济成本。此外,文献[1-3]提出的驱动电路高侧驱动器件与低侧驱动器件采用NMOS器件,为了降低高侧驱动器件的导通电阻,需要在片外集成栅极自举电容,外围应用较为复杂;文献[4]提出的高侧驱动器件与低侧驱动器件分别采用PMOS与NMOS器件,电路工作时,驱动管的过驱动电压接近电源电压,需要工艺提供栅极-源极耐高压的厚栅氧器件,对于设计工艺的依赖较大。

常温下双极工艺NPN/PNP器件的基极-发射极阈值电压只有0.6 V(MOSFET器件普遍在1 V以上),因此与CMOS工艺的驱动电路相比,双极工艺驱动电路拥有更低的导通损耗和更长的使用寿命;同时双极型器件输出电流与基极-发射极电压成指数关系,器件输出跨导效率相比MOS器件显著增加,同等面积下可以比MOS器件得到更大的输出电流,因此采用双极工艺实现的驱动电路可以有效减小芯片面积,提高经济效益。国内外已经研制出了多种基于双极工艺的栅驱动电路[5-7]。文献[5]采用级联达林顿结构驱动功率管,但并没有内置死区时间控制电路,可靠性不高;文献[6]采用双极互补金属氧化物半导体(BiCMOS)工艺,工艺复杂、成本较高;文献[7]采用甲乙类推挽输出驱动结构,在过零翻转点附近存在明显的交越失真,驱动器整体性能不够理想。

为了解决CMOS工艺功率驱动电路驱动能力弱、可靠性不高的问题,本文提出了一种基于双极工艺的功率MOSFET驱动电路,大幅提升了功率驱动电路的驱动效率,并保证了优良的电路可靠性。

2 双极工艺功率栅驱动电路设计

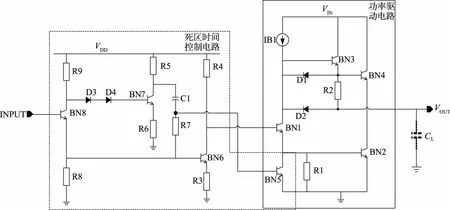

本文提出的基于双极工艺的功率栅驱动电路结构如图1所示。本电路主要由2部分构成:死区时间控制电路和功率驱动电路。死区时间控制电路采用低压电源(5 V)供电,以降低该模块的功耗;功率驱动电路可以在更宽的电源电压条件下(5~35 V)工作,使得栅驱动输出信号可以匹配更多的功率器件。电源电压VDD=5 V,VIN为功率驱动电路电源电压,VOUT为功率驱动电路的输出电压,CL为负载电容。

图1 本文提出的双极工艺功率栅驱动电路

2.1 死区时间控制电路设计

死区时间控制电路设计的目的是防止功率驱动电路中的驱动管BN4和BN2同时导通。因为一旦出现这种情况,电源会直接接地形成短路,使得BN4和BN2因为流过大电流而烧毁失效。

在本文提出的死区时间控制电路中,主通路为BN8、R8、R9与BN6、R3、R4构成的级联传输链路,两者级联后形成达林顿级联驱动结构,以便高速控制功率驱动电路;死区时间控制电路的核心部分由R5、BN7、R6、C1、R7、BN5构成;二极管D3、D4用于设定BN7基极的偏置电压。

2.2 功率驱动电路设计

功率驱动电路将直接驱动功率MOSFET器件,其驱动能力对于驱动器性能尤为关键。本文提出的功率驱动电路高/低侧核心驱动器件BN3、BN4、BN1、BN2均为高电流增益NPN型三极管。为了实现更强的驱动能力,BN3、R2、BN4与BN1、R1、BN2均为达林顿结构,电流增益为两级电流增益之积,驱动效率大幅提高。电流源IB1用于给高侧驱动电路提供基极偏置电流,同时还作为低侧驱动电路第1极的有源负载。高/低侧驱动电路版图采用对称式结构布局,保证高/低侧电路驱动电流能力足够的匹配度。

2.3 全电路工作原理

INPUT上升沿:BN8、R8、R9构成的射随器通过R7连接到BN5基极,将BN5基极电位迅速配置成高电平,此时BN5类似一个开关,迅速将BN2基极拉至低电位,使得低侧驱动管可以快速关断。在低侧驱动管关闭之后,BN6、R3、R4构成的共射极放大电路会将BN1的基极电位拉低,BN3、BN4由电流源IB1驱动,使电路输出高电平。BN5的基极信号只经过BN8、R8、R9一级延迟,BN1的基极信号需要经过BN8、R8、R9与BN6、R3、R4两级延迟,这就保证了低侧驱动管先关断再开启高侧驱动管,防止了高/低侧驱动管同时导通。

电阻R5、电容C1构成一个自举电路。在INPUT上升沿到来之前,R5与C1上极板相连节点的电位为低电平;在INPUT上升沿到来后,BN7基极电位由于BN8和R9构成的共射级放大器作用被迅速置为低电平,R5与C1上极板相连节点被上拉至VDD,电容两侧电压不能突变,C1下极板与R7相连节点电压也会抬升且产生与C1上极板等同的感应电荷,并注入BN5基极,因此可以在开关瞬间增加BN5基极输入电流,加速BN5的开启,进一步加快低侧功率管关断的速度[5]。

INPUT下降沿:在这种状态下,BN7基极被配置成高电平,BN7射极串联电阻R6构成射极负反馈,降低了BN7和R5构成的共射级放大器增益,这将延长BN5基极电位翻转为低电平的时间。在这段时间内,BN1作为开关并开启,BN5构成一个电流漏,分别对高侧驱动管BN3和BN4的基极放电,迅速关断高侧驱动管。高侧驱动管关断的同时,BN5作为BN1的射极负载,减少流入BN2基极的电流,推迟低侧驱动管开启的时间。待高侧驱动管完全关断后,BN5基极电位才逐步变为低电平,低侧驱动电路开始正常工作。通过这种时序设置可有效避免高/低侧驱动管同时导通,并提高驱动速度。

2.4 关键参数设计

电路的关键指标为传输延迟时间,传输速度由电路的时间常数决定。不考虑死区时间对传输延迟时间的影响,电路主通路由4级电路构成:第1级由R9、BN8、R8构成;第2级由R4、BN6、R3构成;第3级由IB1、BN1、BN5构成;第4级由BN3、BN4、BN2构成。

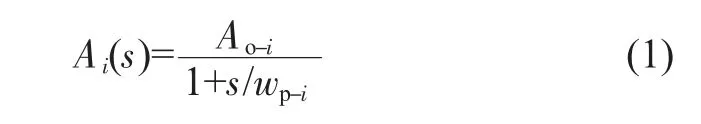

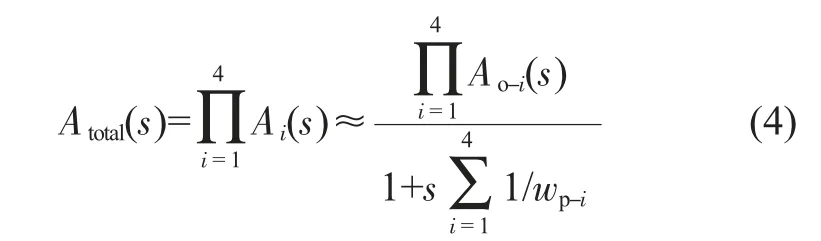

单级的传输函数Ai(s)可以近似表示为:

式中Ao-i为第i级的直流增益,wp-i为第i级的-3 dB频率,s是复频域中的变量。单级的单位增益频率wti为:

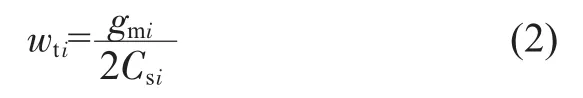

式中gmi为每一级的输入跨导,Csi为每一级节点的寄生电容。所以:

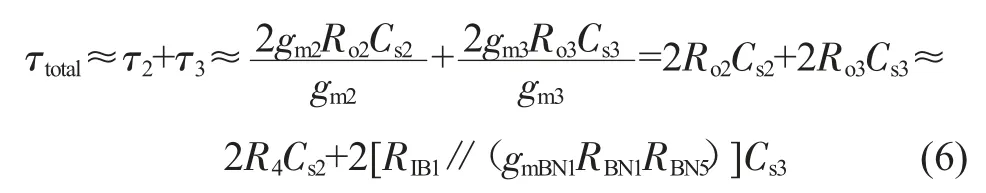

wp-i约为单级单位增益频率的1/2与该级直流增益的商。考虑4级级联,总的传输函数Atotal(s)为:

因此,可以得到总时间常数τtotal为:

由此可见,本电路的传输延迟近似等于单级的时间常数之和,而每1级的时间常数正比于该级的直流增益、节点寄生电容,反比于输入跨导。本电路中第2级、第3级为共射级放大器结构,具有较大的直流增益,对总传输延迟的贡献很大;第1级与第4级直流增益较小,对总传输延迟时间影响很小。因此,降低传输延迟时间需重点设计第2级与第3级。

进一步推导可得:

式中gm2、gm3分别为第2级、第3级的输入跨导,Ro2、Ro3分别为第2级、第3级的输出电阻,Cs2、Cs3分别为第2级、第3级的输出节点电容,RIB1为电流源负载的等效电阻,gmBN1、RBN1分别为三极管BN1的输入跨导和集电极-发射极电阻,RBN5为三极管BN5的集电极-发射极电阻,R4为R4的阻值,Ro2≈R4,Ro3=RIB1//(gmBN1RBN1RBN5)。IB1采用PNP器件构成的电流漏实现,RIB1为PNP管集电极-发射极电阻阻值,远大于第2级输出电阻R4,所以第3级的时间常数对整体传输延迟时间影响最大。

在实际电路设计过程中,还需考虑传输函数二阶效应等非理想效应的影响,因此在数学推导的基础上,需要利用仿真器不断迭代,最终得到电路所要求的传输延迟时间值。

3 仿真验证

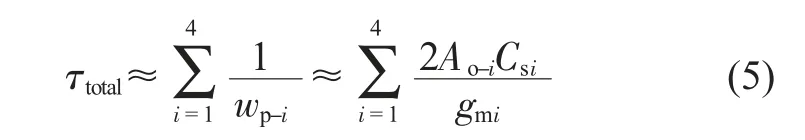

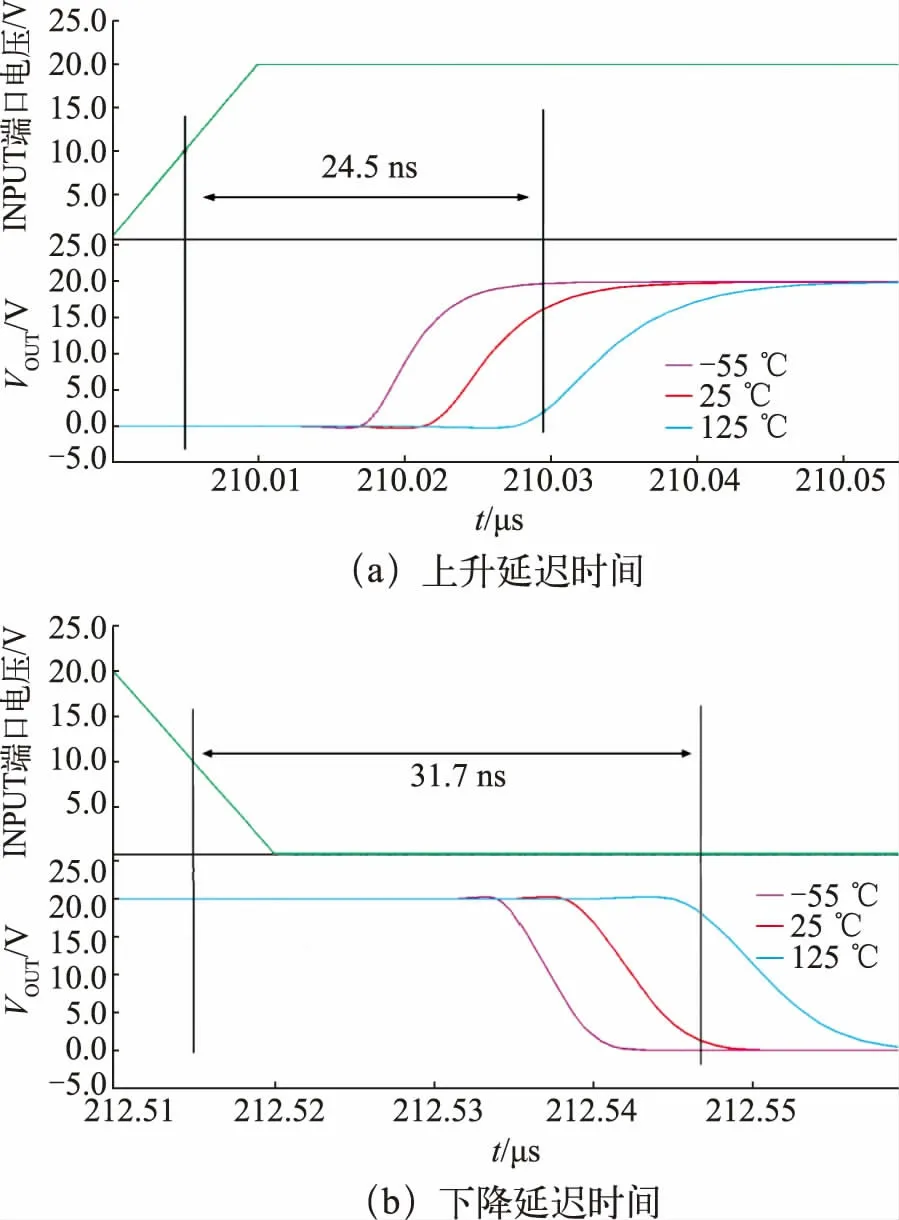

本文提出的功率驱动电路传输延迟特性仿真曲线如图2所示。在VDD=5 V、VIN=20 V、CL=2.2 nF、温度为-55~125℃时,VOUT上升延迟时间不超过25 ns,VOUT下降延迟时间不超过32 ns。

图2 传输延迟时间仿真波形

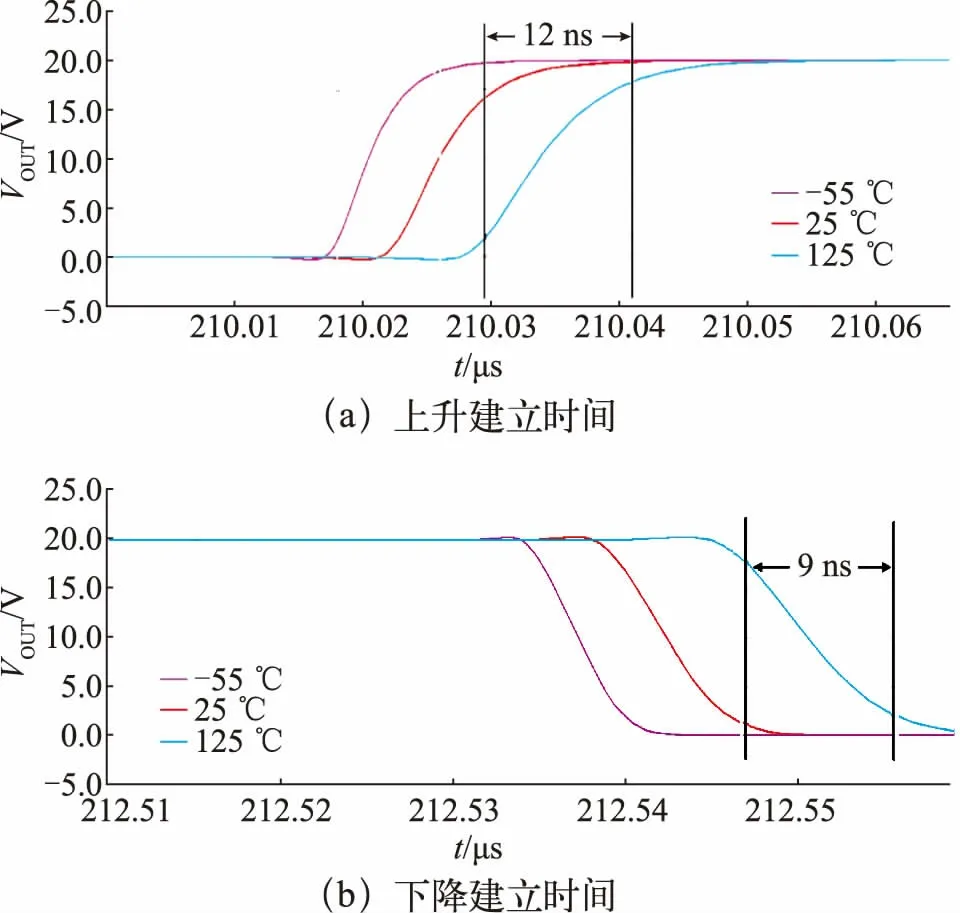

本电路的上升、下降建立时间仿真波形如图3所示,在VDD=5 V、VIN=20 V、CL=2.2 nF、温度为-55~125℃时,VOUT上升、下降建立时间均不超过12 ns。

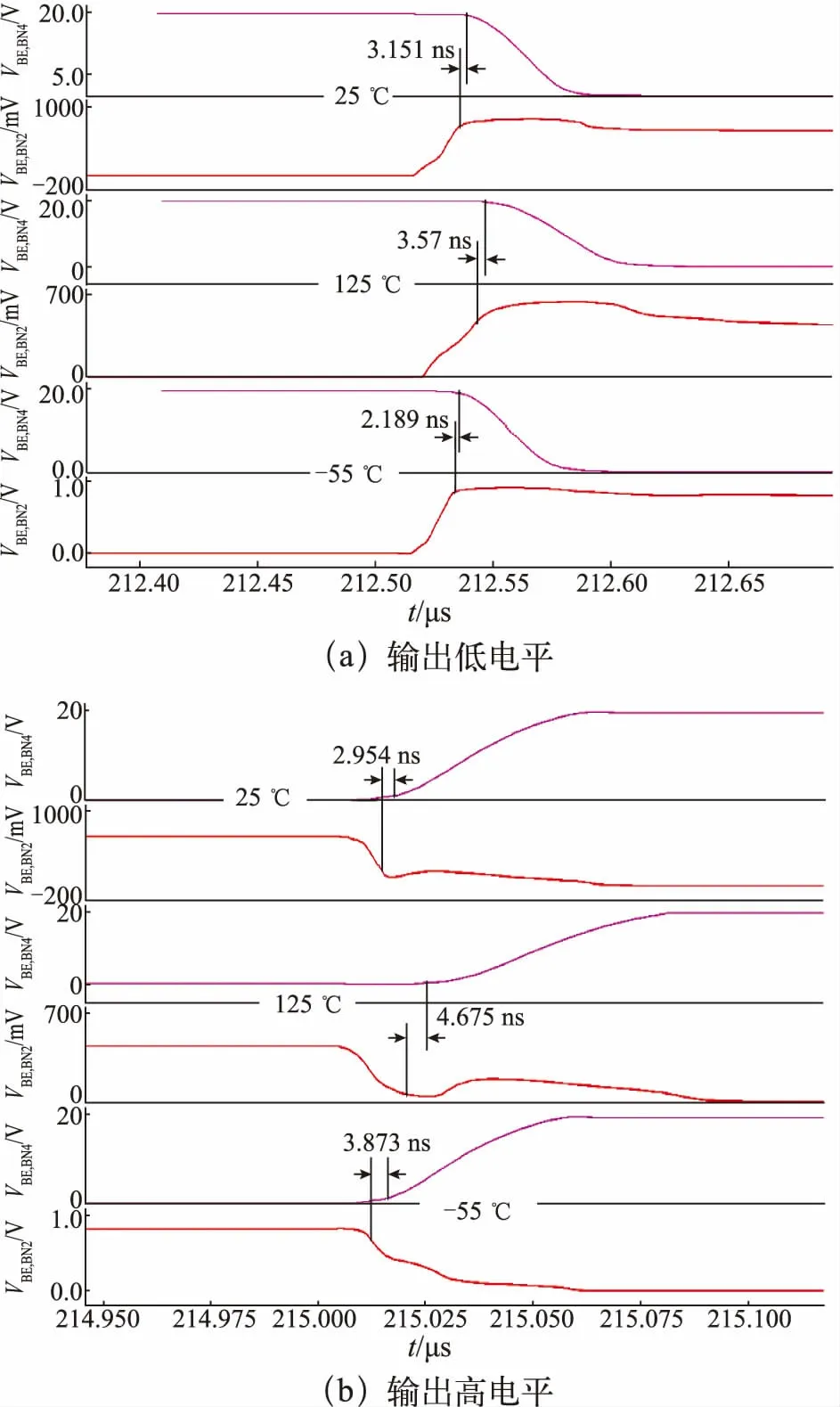

在输出低电平和输出高电平条件下,本电路高/低侧驱动管的死区时间仿真波形如图4所示,图中VBE,BN4和VBE,BN2分别是三极管BN4和BN2的基极电压。在VDD=5 V、VIN=20 V、CL=2.2 nF的条件下,电路在-55~125℃范围内都有充足的死区时间冗余,避免了电路工作时出现高/低侧驱动管同时导通的情况,既提高了电路工作的可靠性,也降低了电路的工作电流。本电路实际工作时电流不超过45 mA。

图3 建立时间仿真波形

图4 死区时间仿真波形

仿真结果证明所设计的电路性能优良,能够满足高速栅驱动电路的需要。电路版图如图5所示。

图5 高速栅驱动电路版图

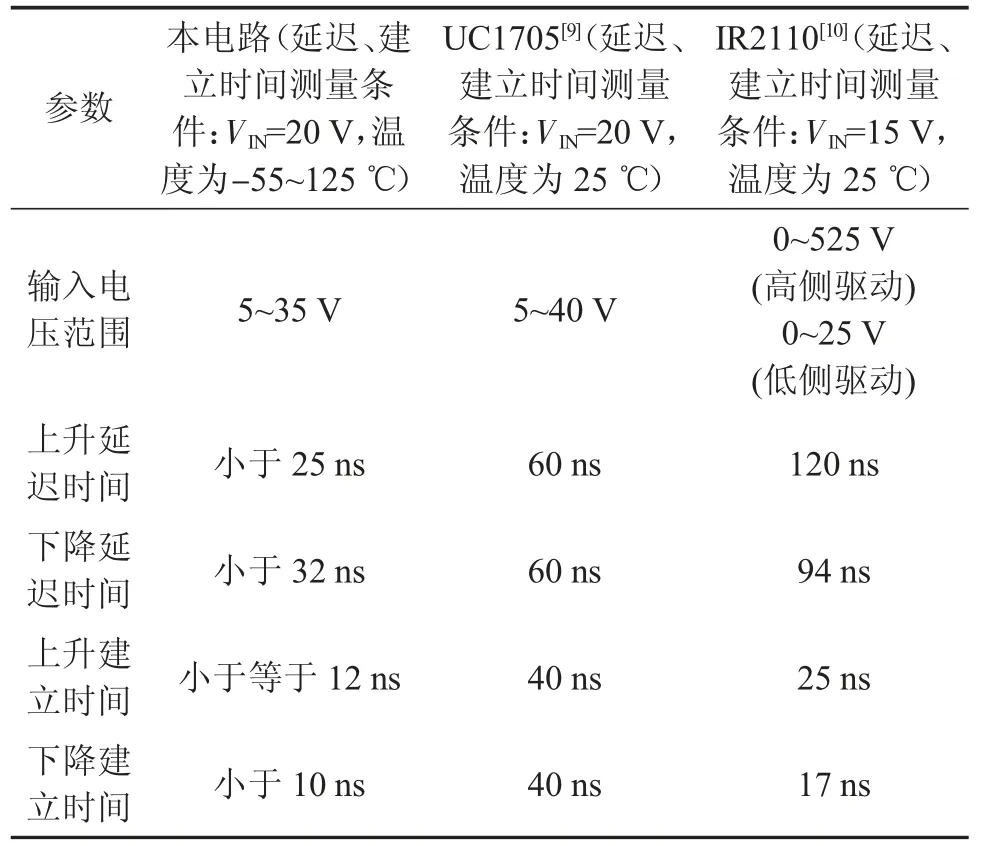

本电路与同类型功率栅驱动电路的主要指标对比如表1所示。本文提出的栅驱动电路的输入电压范围与同类产品UC1705基本相当。IR2110虽然高侧输入电压范围更宽,但是需要外部自举电容才能正常工作,且高/低侧驱动电路输入电源不同,增加了片外应用方案的复杂性。在栅驱动电路核心的传输延迟时间与建立时间方面,本电路明显优于同类电路。

表1 不同栅驱动电路主要指标对比

4 结论

针对大功率MOSFET栅极驱动电路实际需求,为提高栅驱动电路的速度和稳健性,本文提出了一种基于双极工艺的新型高速栅驱动电路。该栅驱动电路工作电压范围为5~35 V,在-55~125℃的温度范围内,传输延迟时间控制在32 ns以内,上升、下降建立时间控制在12 ns以内。