高层综合中面向运算器电源门控技术的低能耗调度算法

2022-08-29姚蔓婷柳宜川袁伟娜

姚蔓婷, 邱 源, 柳宜川, 袁伟娜, 汪 楠

(1. 华东理工大学信息科学与工程学院,上海 200237;2. 上海航天计算机技术研究所,上海 200233)

在摩尔定律的引领下,集成电路的复杂度成倍地提高,工艺节点快速进步至纳米级,芯片设计的复杂度大幅增加,高性能、低功耗架构逐渐成为主流设计要求。尤其是工艺发展至65 nm 及以下时,漏电功耗开始迅速增大[1],加之便携及移动设备的广泛应用,使得漏电功耗成为集成电路中日趋重要的问题[2]。

电源门控技术是工业界常用的一项低功耗技术,它通过关断模块的电源来减少该模块的漏电功耗。电源门控技术首先需要将设计分为不同的电压域,基于电压域的门控称为粗调电源门控。当门控模块需要关断时,该模块的状态将被保存至状态保持寄存器(Retention registers)中以便再次唤醒该模块。王磊磊等[3]通过求解一组线性规划获得最佳接入时间序列来优化电源门控技术中的电压噪声问题。Sumanta[4]尝试在模块切换睡眠模式与活跃模式的过程中重新调度电源门控指令来减少因为电源门控带来的电流涌入问题。Mohankumar 等[5]针对因电源门控技术带来的芯片面积增加的问题,提出了合并触发器来减少门控单元,进而降低面积的增加。Sathanur 等[6]在算法中引入“簇”的概念,并在电路面积及处理速度的约束下,较大幅度地减少了漏电功耗。Kahng 等[7]设计了适用于电源门控设计的状态保持寄存器,使得电路在工作状态下拥有较低的漏电功耗及较小的电路面积。Sinkar 等[8]将温度对电路造成的影响纳入考虑范畴,使得电路在减少10%漏电功耗的同时,还减少了3.7%的动态功耗。Reimann等[9]将电源门控技术在工业设计生产中所面临的诸多因素纳入考虑范围,并在处理速度约束下采用基于拉格朗日松弛的方法,有效地降低了电路的漏电功耗。

然而,随着电路工艺节点技术的快速发展,漏电功耗在总功耗中所占的比重越来越大。因此,为了进一步减少电路的漏电功耗,一种运算器级别的细粒度电源门控技术成为了近期研究的热点。该技术根据各个运算器的工作时间,独立地开关各个运算器的电源电压。Rele 等[10]通过分析各个运算器可能的空闲时段来确定运算器电源的开关时间。Hu 等[11]从电路结构上分析了运算器电源门控技术所能获得的漏电功耗优化结果。Henry 等[12]设计了NEMS 电源门控开关,并建立了采用该电源门控开关电路的能耗模型。Yeh 等[13]提出了一种有效的唤醒策略,可最小化开关运算器电源所带来的工作时延的增加。Kannan 等[14]通过设置运算器漏电传感器,设计了一种基于温度以及处理进程的运算器电源门控方法。此外,诸多研究者[15-16]还尝试通过软件代码分析来计算运算器电源的开关时间,在保证系统性能的同时减少了硬件电路的漏电功耗。

虽然运算器电源门控技术已经成为近期的研究热点,但许多研究者开始尝试从多个角度来减少运算器的漏电能耗。由于在调度过程中无法确定操作的调度及绑定结果,因此目前鲜有人在高层综合中对运算器电源门控技术进行研究。由于高层综合中存在着较多的漏电功耗优化可能性,并且调度是高层综合中最为重要的任务,因此通过合理的调度能够优化后期各个运算器的空闲时段,从而大幅减少电路的漏电能耗。本文在高层综合的调度中对采用运算器电源门控技术的ASIC 电路漏电能耗进行分析,提出了一种启发式算法以实现电路在工作时延以及电路面积不变的前提下优化漏电能耗。

1 电源门控运算器的能耗分析与优化问题

电源门控电路如图1 所示。由输入信号、组合逻辑单元、状态保存触发器、隔离电路、输出信号组成。 PMU( Power-gating Manager Unit) 单 元 产 生Sleep 信号给脚门控单元来控制Vssv。

图1 电源门控电路示意图Fig. 1 Schematic diagram of power gating circuit

1.1 电源门控运算器的能耗分析

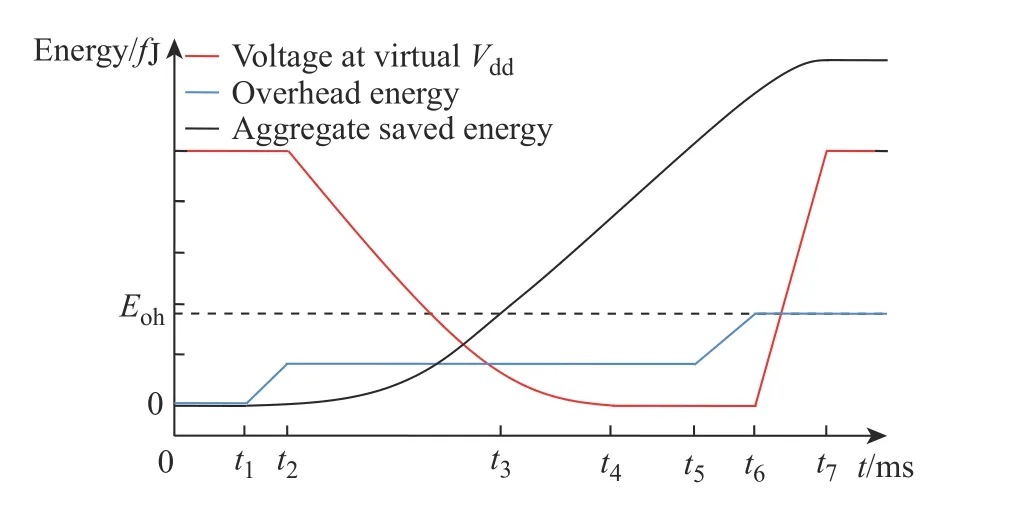

本文所讨论的电路均采用头门控开关(Header device),对于采用脚门控开关的电源门控电路,本文的结论同样适用。图2 示出了开关运算器电源时的能耗-时间关系。

在t=t1时刻,控制电路决定将该运算器的电源关闭,“Sleep”信号被使能并于t=t2时刻送至头门控开关,该过程所需的额外能耗为Eoh1。当头门控开关接收到“Sleep”信号时,电路的虚Vdd(标记为Vddv)开始降低,并于t=t4时刻完全放电。

图2 开关运算器电源时的能耗分析Fig. 2 Energy consumption analysis of power gating a functional unit

设运算器需要在t=t5时刻开始唤醒,“Sleep”信号也将被禁能,相应会产生的额外能耗为Eoh2。在t=t6时,头门控开关已完全打开,Vddv开始充电,并在t=t7时刻完成充电。在平衡点(Break even point)t=t3时,通过降低Vddv减少的运算器漏电能耗等同于开关头门控开关时的额外功耗(Eoh=Eoh1+Eoh2)。平衡时长(Break even cycle count)tbe=t3-t1,表示从关闭电源到平衡点所需的时长;唤醒时长tcu=t7-t6为Vddv的充电时间。运算器需要提前tcu周期开始对Vddv进行充电,以便该运算器能够按时进行操作的运算。所以只有当运算器的空闲间隙的长度tidle>tbe+tcu时,在该空闲时间段内关闭该运算器的电源电压才能减少漏电能耗。

令运算器的电源门控收益均衡时间为toh=tbe+tcu。当tidle=toh时,开关该运算器既不会减少也不会增加运算器的能耗;当tidle<toh时,开关该运算器会产生额外的能耗;而当tidle>toh时,开关该运算器能够减少能耗。因此能够通过关闭电源获得电源门控收益,收益量与tidle-toh成正比。

设IIi表示第i个空闲间隙,根据空闲间隙所处的位置,将其分为以下3 类:(1)运算器上相邻两个操作之间的空闲间隙;(2)在程序开始之前及第一个操作之间的空闲间隙;(3)在最后一个操作及程序结束之间的空闲间隙。如果空闲间隙的长度为0,同样认为该空闲间隙是存在的,因此空闲间隙的数量等于操作的数量与运算器数量之和。

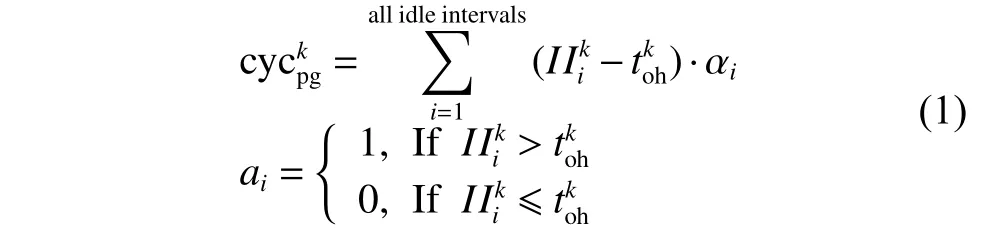

操作类型为k的运算器中空闲间隙内的收益时长表示为,定义如下:

则该运算器减少的漏电能耗为ERk,其计算方法如下:

对于所有操作类型为k的运算器,其所有的空闲间隙的总收益时长表示为 c ycpg,因此,开关该类型运算器所能减少的漏电能耗为ER。

1.2 电源门控运算器的问题描述

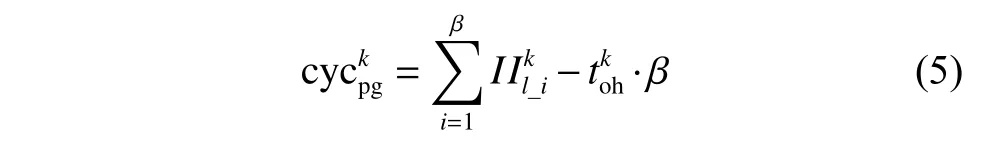

为了直观地展示高层综合中的调度过程对电路漏电能耗的影响,图3 示出了一个数据流程图(Data Flow Graph, DFG)(图3(a)),并针对此数据流程图给出了2 种不同的调度及绑定结果(图3(b),3(c))。

图3 中所需的ALU(Arithmetic and Logic Unit)数量均为1,乘法器数量均为3,时间约束为12 个时钟周期,其中乘法器的收益均衡时间为=8 周期,ALU 的收益均衡时间=3 周期。图3(b)示出的是先采用List scheduling 算法进行调度再使用Left edge 进行绑定的高层综合结果,其对应的=2周期。而在图3(c)中所示的例子中,=6 周期,因此该结果将获得更多的漏电能耗优化。

问题的输入:DFG,时间约束tc,资源约束;

优化目标:对每个操作进行调度,从而最大限度地优化运算器的漏电能耗(Energy reduction)。

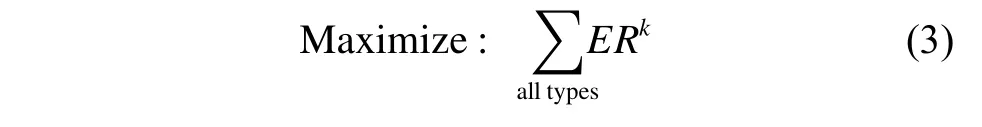

目标函数可以表述为

2 基于空闲间隙的漏电能耗优化算法

2.1 空闲间隙分析

运算器中空闲间隙的长度直接决定了运算器所能优化的能耗,因此需要首先分析运算器中各个空闲间隙的长度。

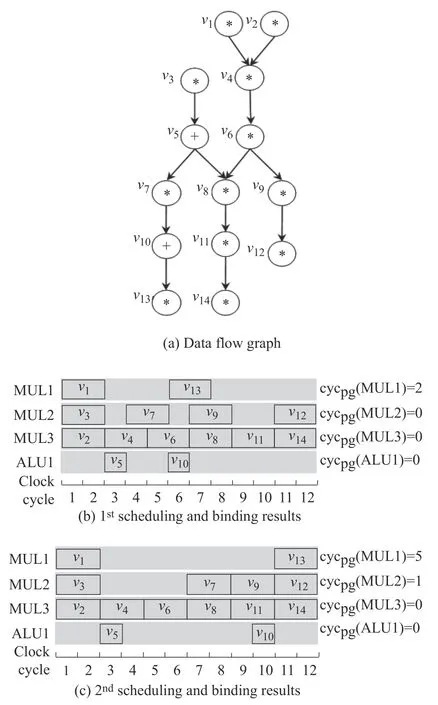

k类运算器中所有空闲间隙的总长度可以用如下公式表示:

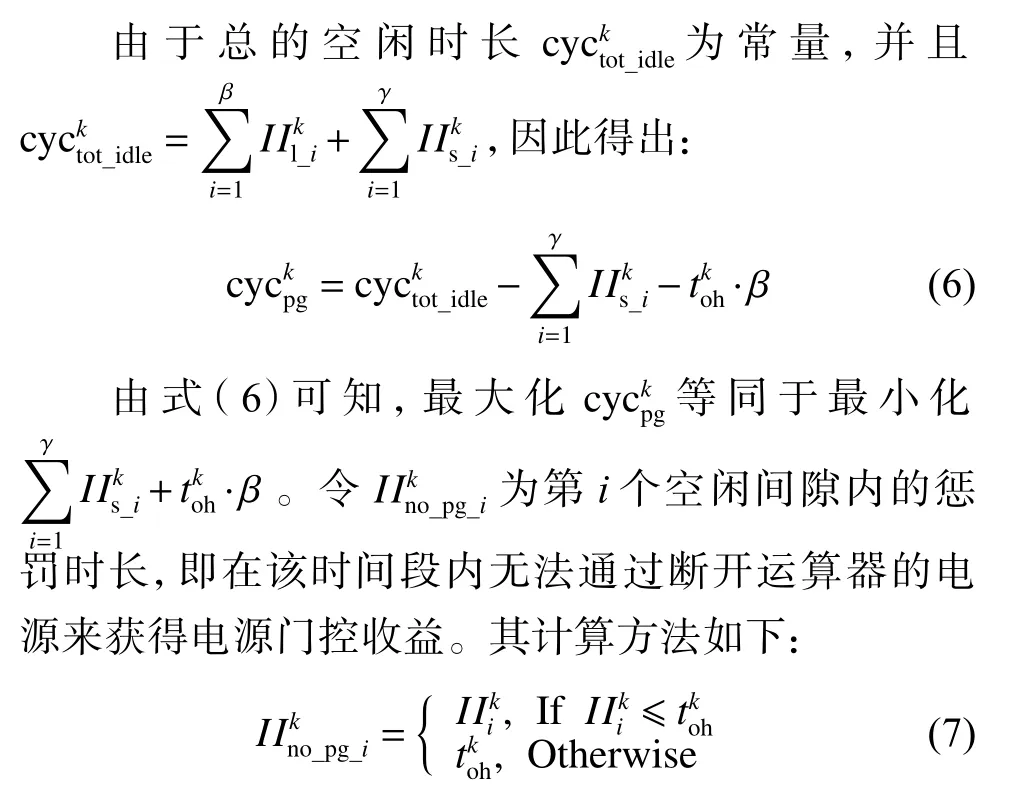

根据空闲间隙的长度,将空闲间隙分为两类:(1)长空闲间隙IIl,即IIl>toh;(2)短空闲间隙IIs,IIs≤toh。设长空闲间隙的数量为 α ,短空闲间隙的数量为 β ,则有 α +β=+nk。式(2)显示,最小化运算器的漏电能耗等同于最大化,而由式(1)可得:

图3 调度结果对电源能耗的影响Fig. 3 Influence of scheduling results on power consumption

则所有k类型运算器上的空闲间隙的惩罚时长之和为 c ost_cyck,

因此,最小化漏电能耗问题就可以转化为最小化所有运算器上空闲间隙内惩罚时长之和的问题。

2.2 基于空闲间隙的调度算法

在进行调度前,需要对所有的操作分别进行资源约束下的ASAP (As-Soon-As-Possible)调度以及ALAP (As-Late-As-Possible)调度以确定各个操作在可调度空间(Mobility)。操作vi的可调度空间表示为M(vi)=[Ms(vi),Me(vi)] ,其 中Ms(vi) 表 示调 度 开始 时刻;Me(vi) 表示调度结束时刻。

只有当两个操作能够被绑定至同一个运算器上,它们之间才可能存在空闲间隙。能够被绑定至同一运算器的两个操作称为操作间相互兼容,本文将根据操作的可调度空间来判断两个操作是否兼容。操作vi与vj兼容,则它们的操作类型相同,并且M(vi)∪M(vj)≥d(vi)+d(vj) 。操作vi的兼容集C(vi)为所有与vi兼容的操作构成的集合。

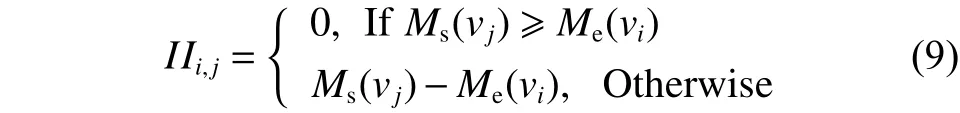

在实际调度中,由于操作在其可调度空间中存在多个可能的调度结果,因此需要首先计算出操作之间空闲间隙的长度。现有操作vi与vj,并且vj∈C(vi) ,则操作vi与vj之间的空闲间隙长度表示为IIi,j,其计算方法如下:

IIi,j中无法获得电源门控收益的时长为IIno_pg_i,j,其计算方法为

本文算法步骤如下:

输出:操作的调度方案

在调度过程中,每个操作的不同调度结果都会改变DFG 中其他操作的调度空间,从而直接影响着操作的调度结果以及绑定结果,因此无法在调度的过程中确定各个运算器的工作以及休眠时间。而针对运算器休眠时长进行功耗优化的电源门控技术也无法确定电源的开关时间,所以无法直接在高层综合中对采用细粒度电源门控技术的能耗优化结果进行评估。针对此,本文通过将能耗优化问题进行规约成为求解最小惩罚时长的问题,并采用基于贪婪算法的调度算法实现问题的快速准确求解。

本文提出的基于贪心策略的启发式算法,每次针对未被调度的操作遍历其所有可能的调度方法,计算惩罚时长,选取当前状态下最优解,直至所有操作调度完成。本文算法的时间复杂度为O(n2),能够对DFG 实现快速的计算,得到近似最优解。

3 实验结果及分析

3.1 实验配置

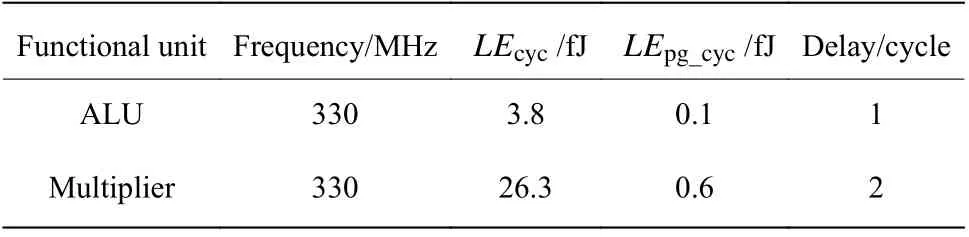

为验证本文算法的有效性,实验中对6 个数据流程图进行了操作调度,这些流程图有些是由已有算法抽象而得(ar, ellip, mpeg, fft), 有些则是随机生成的(ran0,ran1)。为了简化实验,只选择了ALU 以及乘法器这两种运算器进行实验,其单位时钟周期内的漏电能耗是采用Synopsys Design Compiler,并利用65 nm standard cell library 对32 bit 的ALU 以及乘法器进行综合仿真得到的。各类型运算器的漏电能耗仿真结果如表1 所示。其中LEcyc表示运算器单位时钟周期内的漏电能耗,LEpg_cyc表示使用电源门控后一个周期内运算器漏电能耗。Delay 表示运算器的延迟周期数。

由于高层综合中操作的调度及绑定结果无法确定,所以鲜有研究者在高层综合中对运算器电源门控技术进行研究,而大多都集中在逻辑综合及版图综合中。因此,为了验证本文算法在优化能耗问题上的性能,选取了在高层综合中经典的操作调度算法-力驱动调度算法(Force-Directed Scheduling,FDS)进行能耗优化结果的对比。同时考虑到温度对运算器的均衡时间toh会产生较大影响,因此本实验将测试两组不同的运算器均衡时间:(1)=3 周期,=8 周期;(2)=5 周期,=12 周期。此外,由于不同的硬件资源约束同样会对调度的结果产生影响,因此还针对每组数据流程图测试两组不同的资源约束。

表1 运算器漏电能耗仿真结果Table 1 Simulation results of leakage energy consumption of functional units

3.2 实验结果

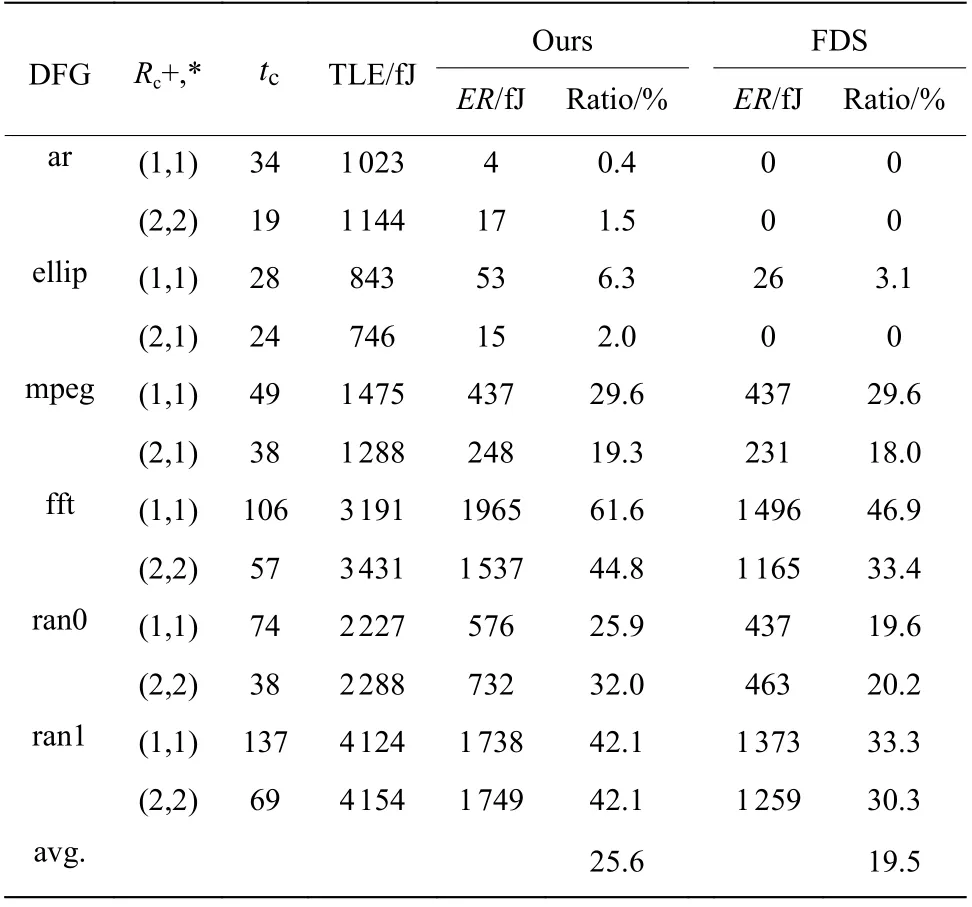

当运算器的均衡时间设置为=3 周期、=8周期时,实验结果如表2 所示。其中tc为电路的性能约束,本文将tc设置为数据流程图在相应的资源约束下所需的最小调度时长;Rc表示ALU 和乘法器两种不同的资源约束;TLE 表示未对运算器进行电源门控时总的漏电能耗;ER表示使用电源门控后两种算法降低的漏电能耗;Ratio 表示降低的漏电能耗占总漏电能耗的比率。实验结果显示,采用传统的力驱动调度算法所得的调度结果仅能优化27.4%的能耗,而采用本文算法,则能够优化30.8%的能耗。

当运算器的均衡时间设置为=5 周期、=12 周期时,相应的优化结果如表3 所示。该结果显示,采用FDS 算法进行面向细粒度的电源门控技术的调度时,可以减少19.5%的漏电能耗;而采用本文算法能够进一步减少漏电能耗至25.6%。

表2 =3 时钟周期,=8 时钟周期时的能耗优化结果Table 2 Optimation results of leakage energy reduction when=3 cycle, =8 cycle

表2 =3 时钟周期,=8 时钟周期时的能耗优化结果Table 2 Optimation results of leakage energy reduction when=3 cycle, =8 cycle

DFG Rc+,* tc TLE/fJ Ours FDS ER/fJ Ratio/% ER/fJ Ratio/%ar (1,1)(2,2)34 19 1 023 1 144 16 31 1.6 2.7 0 22 0 1.9 ellip (1,1)(2,1)28 24 843 746 77 52 9.1 7.0 77 26 9.1 3.4 mpeg (1,1)(2,1)49 38 1 475 1 288 591 358 40.1 27.8 591 334 40.1 25.9 fft (1,1)(2,2)106 57 3 191 3 431 2 134 1 762 66.9 51.4 1 866 1 493 58.5 43.5 ran0 (1,1)(2,2)74 38 2 227 2 288 728 765 32.7 33.4 617 676 27.7 29.6 ran1 (1,1)(2,2)137 69 4 124 4 154 1 957 2 053 47.5 49.4 1 810 1 893 43.9 45.6 avg. 30.8 27.4

表3 =5 时钟周期, =12 时钟周期时的能耗优化结果Table 3 Optimation results of leakage energy reduction when=5 cycle, =12 cycle

表3 =5 时钟周期, =12 时钟周期时的能耗优化结果Table 3 Optimation results of leakage energy reduction when=5 cycle, =12 cycle

DFG Rc+,* tc TLE/fJ Ours FDS ER/fJ Ratio/% ER/fJ Ratio/%ar (1,1)(2,2)34 19 1 023 1 144 4 17 0.4 1.5 00 00 ellip (1,1)(2,1)28 24 843 746 53 15 6.3 2.0 26 0 3.1 0 mpeg (1,1)(2,1)49 38 1 475 1 288 437 248 29.6 19.3 437 231 29.6 18.0 fft (1,1)(2,2)106 57 3 191 3 431 1965 1 537 61.6 44.8 1 496 1 165 46.9 33.4 ran0 (1,1)(2,2)74 38 2 227 2 288 576 732 25.9 32.0 437 463 19.6 20.2 ran1 (1,1)(2,2)137 69 4 124 4 154 1 738 1 749 42.1 42.1 1 373 1 259 33.3 30.3 avg. 25.6 19.5

4 结束语

电源门控技术能够有效地减少电路的漏电能耗,本文算法通过对操作进行合理的调度来最小化运算器开关的惩罚时长从而对电路的漏电能耗进行优化。首先将能耗优化问题转化成为调度的空闲间隙问题,随后对不同调度结果下的惩罚间隔时长进行评估,并选择最小的惩罚间隔进行调度,最后实现电路的能耗优化。实验结果验证了本文算法的有效性,并表明该算法可较好地应用于星载平台的低功耗电路设备的设计。