高精度Sigma-Delta ADC芯片设计研究

2022-08-09刘庆一孙艳杰孙文海刘瑞华赵义强

刘庆一 孙艳杰 孙文海 刘瑞华 赵义强

1.大唐半导体科技有限公司 山东省青岛市 266100 2.齐鲁工业大学(山东省科学院)山东省科学院自动化研究所 山东省济南市 250014

1 引言

近年来,随着传感器技术的发展,各类传感器广泛应用于工业及汽车电子产品等领域。模数转换器(ADC)作为传感器信号数字化的重要电路单元,对其精度及速度要求较高。Sigma-Delta ADC 利用过采样和噪声整形技术,可以提高信号的信噪比,提升转换精度。

本文专注于高精度模数转换器芯片的设计,研究面向车规级传感器信号采集应用的16-bit高精度、低噪声微弱电信号采集和模数转换电路的架构设计技术,以及低噪声设计技术、失调消除技术、高性能信号缓冲器轨到轨输入级设计技术。设计高精度、数据率可调Sigma-delta调制器,低通带纹波降采样滤波器设计技术,低噪声参考电压产生技术、电源和共模干扰抑制技术,实现高可靠高精度Sigma-Delta型模数转换器芯片。

2 总体方案

总体架构如图1所示,由多位Sigma Delta调制器、重建滤波器、可编程抽取滤波器、FIR滤波器以及输入缓冲器、控制逻辑等构成。片内集成基准电压驱动缓冲器以及用于输入信号缓冲、电平转换的差分放大器,形成高度集成的紧凑型数据采集器件,消除复杂模拟前端信号处理电路设计需求,简化ADC使用。

图1 Delta sigma ADC系统架构示意图

3 电路实现

3.1 Delta sigma调制器

Delta sigma调制器结构如图2所示,为满足高精度高速性能需求,将采用带有双采样积分器的3阶5-bit多比特量化高阶调制器结构。调制器电路基于离散时间的开关电容电路实现,包括三个开关电容积分器、一个5-bit异步时序逐次逼近量化器、动态元件匹配电路、32级的开关电容DAC等。

图2 基于3阶5-bit多比特量化的调制器结构示意图

在5-bit量化器中,第一级、第三级的采样电容和反馈电容均分成31个单元,用来完成32级数模转换(DAC),并通过对第一、第二、第三级的单位电容进行优化设计降低开关KT/C噪声。

差分输入由调制器以最高40MSPS的采样速率进行采样,可在64倍过采样率下实现最高625kSPS的转换速率。所有的控制信号由双向不交叠时钟产生,避免电荷注入带来的误差。第一级积分器的输入采样开关采用自举开关,消除采样开关的非线性导通电阻带来的失真;内部采样和反馈开关,由于传输电平幅度变化较大,为保证良好的导通性使用互补CMOS开关。图3为双采样积分器与时序示意图。

图3 双采样积分器与时序示意图

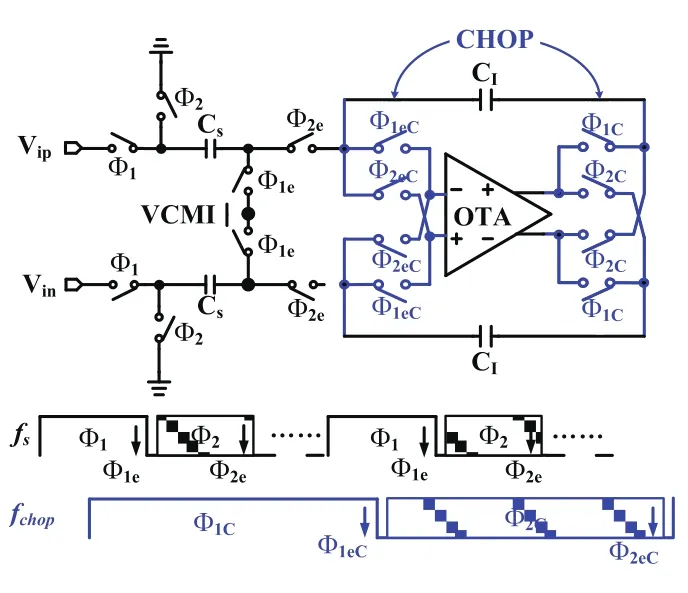

在第一级积分器内部跨导放大器(OTA)的输入和输出端使用斩波技术来消除OTA的1/f噪声和失调,图4为积分器中斩波技术示意图。通过选择斩波动作与时钟相的关系,减小对时序的要求。通过优化斩波频率,降低过快的时钟翻转带来的额外开关噪声和功耗。

图4 积分器中斩波技术示意图

量化器前拟采用一种新型的模拟加法器结构,消除传统的模拟加法器带来的幅度衰减,避免补偿运放或者降低参考电压带来的消耗,减小功耗,降低电路实现难度。

调制器采用一种5-bit异步时序的逐次逼近的量化器,相比基于传统的Flash结构的5-bit量化器,有明显的面积和功耗优势。采用异步时序逻辑,相比同步时序,不需要高速的外部时钟,减小功耗代价。和前级积分器采用同一时钟,简化电路实现。

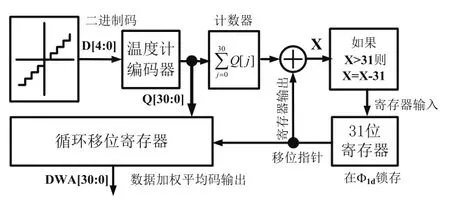

量化器通过一个温度计译码器,转换成温度计码。然后通过动态元件匹配(DEM)模块,转换成DAC的控制信号,完成DAC反馈。DEM采用一种基于数据加权平均(DWA)算法的方式实现,具有实现简单、硬件代价较低的优点。

3.2 运算放大器设计

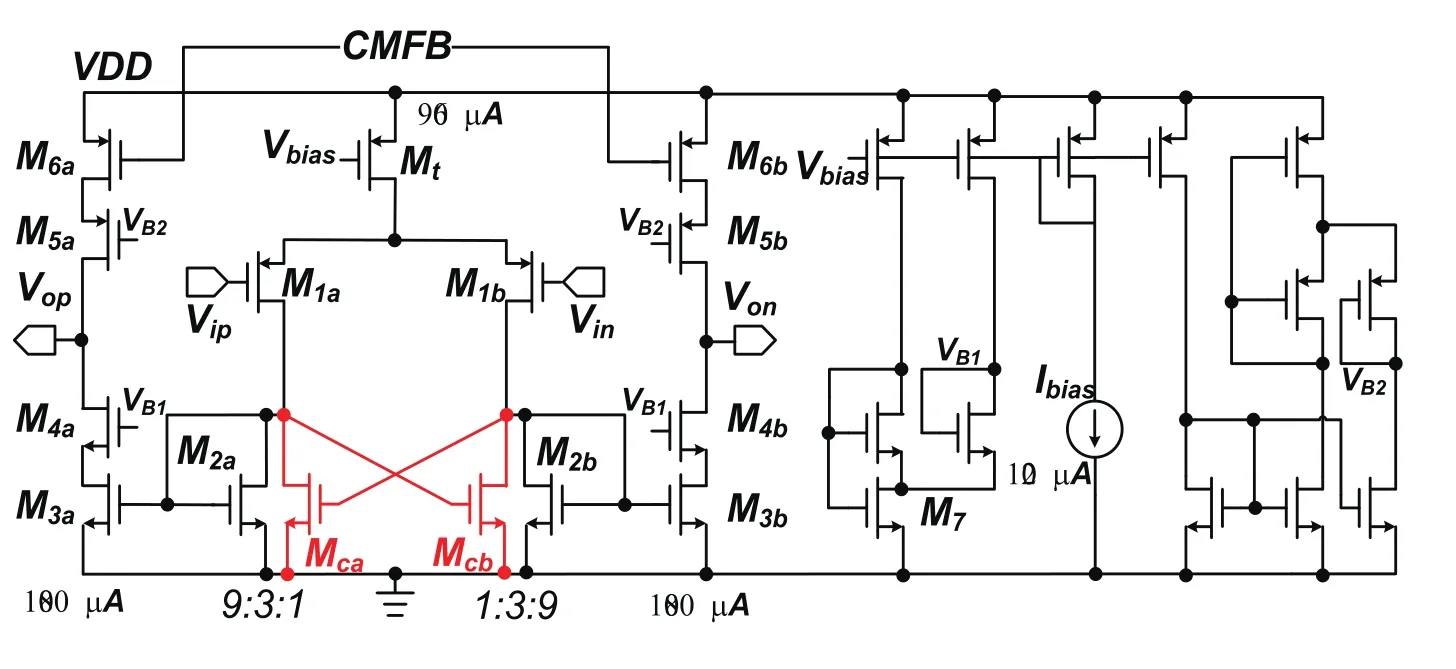

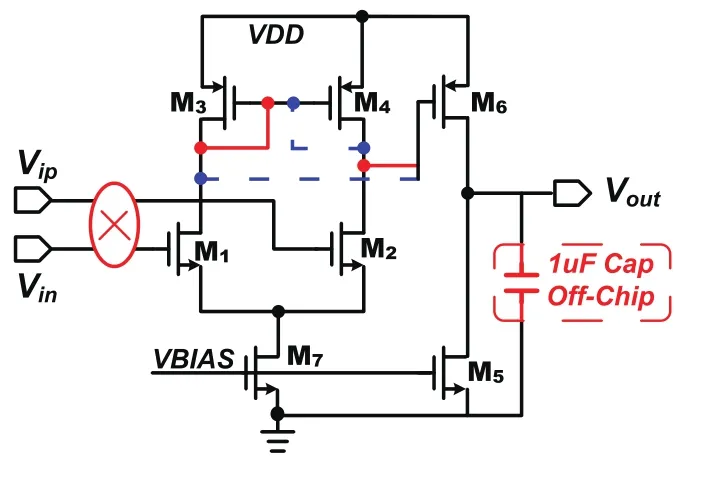

由于采用多阶积分器结构,后级引入的噪声会被环路抑制。第一积分器内部OTA必须被仔细设计,才能避免OTA引入的噪声和非理想因素严重恶化调制器性能。OTA的有限增益会对积分器引入增益误差和NTF的极点误差,造成量化噪声泄漏,此外OTA的非线性增益也将造成量化噪声混叠,从而增加带内噪声能量。第一级积分器内部OTA原理图如图5所示。

由于采用前馈结构和多比特量化,积分器的输出摆幅有很显著的缩减,因此增益非线性的影响被弱化很多,如图5所示,第一级积分器将采用电流镜运放结构。输入管采用PMOS输入,用来减小OTA贡献的1/f噪声,此外PMOS独立的N阱也可以屏蔽数字电路到模拟电路的耦合噪声串扰,输出级采用cascade结构用来提高增益。电流镜运放结构的优点是主级点和非主极点相距甚远,OTA的相位裕度接近90度,接近为一个单级运放,当闭环工作时,稳定性非常强。同时,电路采用电流消去技术,将非主极点的从高频往低频处推,进而可以使OTA的相位裕度下降到60度附近,此时积分器建立特性最为理想。

图5 第一级积分器内部OTA原理图

3.3 5-bit SAR量化器设计

采用的5-Bit异步时序控制SAR量化器的结构、时序以及控制逻辑如图6(a)所示。整个SAR量化器共包括三大模块:开关电容阵列、比较器和异步时序逻辑。开关电容阵列采用二进制的方式分布,开关电容阵列所有的电容在积分相为第三级积分器的负载,因此对电容值进行优化设计,保证第三级积分器完全建立的同时降低工艺引起的电容失配影响。比较器采用一种动态比较器实现。图6(b)为SAR量化器的工作时序。

图6 (a)5-Bit异步时序SAR量化器结构 (b)工作时序

3.4 动态匹配逻辑设计

将采用基于数据加权品均算法(DWA)的动态匹配(DEM)技术来消除多比特DAC引入的非线性失真,该算法DWA具有实现简单,消除DAC非线性效果好的优点。图7给出基于DWA算法的DEM实现框图。SAR量化器在Φ相时,对输入信号进行量化、然后将输出的二进制码输入温度计编码器,产生温度器编码。温度计编码放入一个循环移位寄存器,等待31位寄存器的移位指针的控制信号,来进行输出。温度计编码输出进入计数器,进行一个求和,后级处理保证和不能大于31,然后将这个数送入寄存器。最终产生移位指针给循环移位寄存器产生DWA的31位输出。数据加权平均码由Φ控制,用来产生调制器中的开关,实现DAC反馈。

图7 动态元件匹配逻辑结构示意图

3.5 Bandgap和参考电压产生电路

Bandgap和参考电压产生电路对高精度ADC设计至关重要,设计中将片内集成参考电压缓冲级,由于为栅极高阻输入,因此电阻串分压即可完成参考。如图8所示的两级放大器为片内参考电压缓冲级,第一级采用五管差转单电路,后接一级共源放大器输出。由于参考缓冲级引入的噪声不能被调制器环路抑制,将直接叠加到输入信号上,需对参考电路进行低噪声设计与优化。

图8 电压参考缓冲级

除了热噪声的影响,低频1/f噪声也必须被抑制到足够低的水平。运放采用简洁结构,尽量减少噪声来源。电路将采用斩波技术,用来消除低频失调和1/f噪声。

3.6 滤波器设计

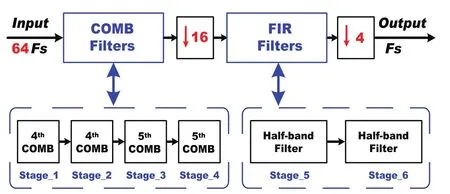

采用的降采样滤波器结构如图9所示,将采用六级级联结构减小滤波器设计难度。滤波器的前四级由于过渡带较宽,对性能要求相对较低,因此采用容易实现的组合(Comb)滤波器,前两级和第三第四级分别为四阶和五阶Comb滤波器。后两级由于过渡带非常窄,而且对整个降采样滤波器的性能起着决定性作用,因此采用2个高阶FIR结构的半带滤波器实现。每一级滤波器对信号完成2倍的降采样,因此整个半带滤波器完成64倍降采样。

图9 降采样滤波器的系统结构

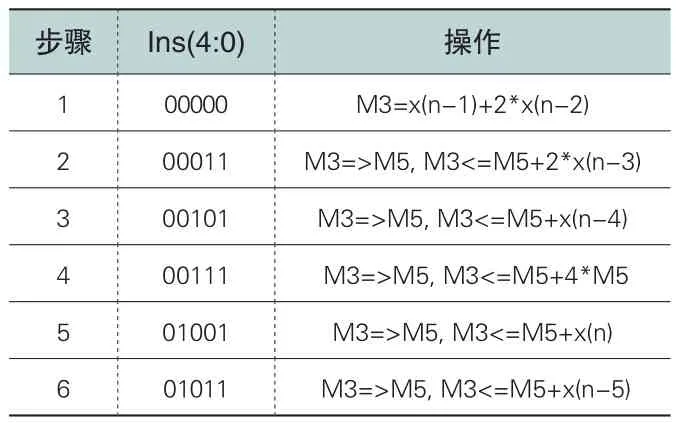

前四级组合(Comb)滤波器采用级联积分梳状(Cascaded Integrator Comb,CIC)滤波器,属于线形相位FIR滤波器,由工作在高抽样率的级联理想积分器和低抽样率的级联微分器组成。CIC滤波器的主要特点是:实现简单且速度高,仅利用加法器、寄存器以及多路选通器就可以实现,因此实现代价小。第一、二级采用四阶结构,而第三、四级采用五阶结构。前四级Comb滤波器的实现方法比较相似,图10给出第四级5阶Comb滤波器结构示意图,其工作在1/16芯片主时钟频率,可以采用时分复用的方式来减小硬件代价。通过采用时分复用,本级滤波器只需一个多位加法器即可实现。表1为第四级Comb滤波器工作时序示意。

表1 第四级Comb滤波器工作时序示意

图10 第四级Comb滤波器结构

整个降采样滤波器最后两级将采用线性相位的FIR半带滤波器实现,其决定着整个降采样滤波器的性能。为了达到24-Bit的精度,高频噪声必须要被衰减到足够低的程度,加上此时滤波器过渡带十分窄,因此半带滤波器阻带衰减至少要大于100dB,此外还需要尽量窄的过渡带。由于采用FIR结构,要求高阶数滤波器。传统方式实现,高阶滤波器将占据十分大的芯片面积和功耗。拟采用一种高效的110阶级联子滤波器结构的FIR半带滤波器,同时采用时分复用和滤波器系数CSD编码的实现方法,从而达到低功耗、低面积消耗的高阶滤波器实现。两级半带滤波器将采用同样的结构实现,如图11所示,图中F2为级联的子滤波器,子滤波器F2结构如图12所示。

图11 半带滤波器结构

图12 子滤波器F2结构

4 结束语

本文基于正向设计和反向参考,采用中芯国际0.13um CMOS工艺,离散时间sigma-delta架构,模拟前端着重改善噪声性能,优化差分匹配和通道匹配,增强通道隔离;在数字域使用数字滤波,滤除50/60Hz工频噪声,提高了信噪比。