基于IEEE 1588 精密时钟同步系统的设计*

2022-06-02景金荣范正吉洪应平

景金荣,范正吉,洪应平

(中北大学仪器科学与动态测试教育部重点实验室,山西 太原 030051)

实时性是分布式控制系统协同作业的重要体现,由于各节点时钟在物理上具有分散性导致线路延时问题以及晶振长时间使用易出现时钟漂移现象[1-3],二者共同作用导致各节点时钟不统一。尤其是航空航天对时钟同步要求严苛的领域[4-6],分布式系统要对各节点回采数据进行整合分析,任一节点出现问题,都会导致数据无法精准融合,导致协同作业失败,系统数据无效的后果[7-9]。

要实现时间同步,关键在于提高时钟同步的精度,时钟同步又由时间戳的精度决定[10-11]。为解决上述分布式系统时钟无法统一问题,本文设计一种基于IEEE 1588 精密时钟同步系统,该系统通过软件标记时间戳和硬件标记时间戳的方法,通过双重标记,大大提高时间戳的精度,从而大大提高时间同步的精度。

1 时间同步模型

常见的时间同步模型有三种:网络时间协议(Network Time Protocol,NTP)、GPS 时钟同步、精确时间协议(Precision Time Protocol,PTP)。NTP 虽应用广泛,但其精度较差,只能达到毫秒级;GPS 时钟同步设备价格高昂;PTP 协议同步精度可达纳秒级,除此之外,在当前主时钟失效情况下,可以重新配置主从时钟角色,因此广泛应用于高精度场合,本次设计是基于PTP 协议实现的。

该协议原理是通过主从设备发送PTP 报文的链路延时和主从时钟的时间差来调整从时钟的时间,使从时钟能实现时钟同步。具体交互原理如图1 所示。

图1 主从时钟交互流程

主时钟给从时钟发送Sync 同步报文,记录报文发出时间t1;发完Sync 报文后,会把t1放入Follow_Up 跟随报文里,然后发往从时钟,从时钟收到Sync报文后,记录收到报文时间t11;收到Follow_Up 报文后,从Follow_Up 报文里取出t1时间,此时从时钟知道了t1和t11时间。

为计算主从时钟的链路延时,从时钟收到Sync报文后,向主时钟发送Delay_Req 延时请求报文,同时记录发出报文时间t2,主时钟收到该报文后,记录收到时间t22,并把该时间装入该报文给从时钟。从时钟收到报文后,取出时间戳t2。此时,从时钟知道了t1,t11,t2和t22四个时间。

假设主时钟到从时钟的时间偏差为toffset,路径延时为tdelay,则可以得到如下等式:

二式联立便可计算出主从时钟的时间差和链路延时,如下式所示:

2 整体设计

本文进行了基于IEEE 1588v2 协议的时间同步系统的设计,并将该协议成功运用于片上系统STM32F407。在总体设计上,采用一主一从的系统设计,主机即主时钟,从机即从时钟,主从时钟之间需要通过基于PTP 同步帧的数据收发来完成从机与主机的时间对准。

如图2 所示,系统构建的时间同步的应用层,负责具体的时间同步工作,例如定时发送SYNC 同步帧、解析时间同步帧、运算线路延时、更新本地时间、通过Announce 帧确定主从时钟等;LWIP 协议栈提供数据链路层、网络层、传输层软件构建;采用了IEEE 1588 高精度时间同步协议收发器DP83640 作为网络通信的PHY 芯片,对于STM32F407 控制芯片而言,该芯片负责以太网时间同步帧收发及对DP83640 的寄存器控制这两个方向的任务。STM32F407 控制系统与PHY 芯片之间采用双接口通讯,采用RMII 接口来连接以太网物理层和链路层;采用MDIO 接口完成对DP83640 寄存器读写,并在此基础上抽象出PTP 协议控制层,完成时间戳读写,以太网口配置,时钟相位调整。该系统通过在PTP 控制层的软件时间戳标记A 与在DP83640 时间同步控制器的硬件时间戳标记B 来增加时间同步。

图2 系统总体设计

3 硬件设计

系统硬件上主要完成对DP83640 的电路设计,STM32F407 的电路设计以及通讯接口设计。以下主要对这三个模块进行说明。

3.1 基于DP83640 的以太网物理层电路设计

DP83640 Precision PHYTER 器件是德州仪器基于IEEE 1588 标准的精确时钟同步芯片。设备支持的关键功能是:对时钟同步数据帧进行自动识别并在物理层实现时间戳标记;支持以太网链路层数据包的时间戳标记;可灵活配置时钟分频、相位等关键参数;支持RMII,MII 两种接口,可在硬件层面连接多种上层设备并具有通信最大带宽为100 Mbit/s。具体电路设计如图3、图4 所示。

图3 DP83640 外围电路

图4 DP83640 相接的以太网口设计

3.2 基于STM32F407 的控制电路设计

STM32F407 系列MCU 是当前较为流行的微控制器。该芯片具有以太网RMII/MII 接口,这是本设计采用该芯片的最为重要的原因。本设计中所用的处理器外围电路主要有MDIO 和RMII 接口,UART串口,LED 灯,复位电路,时钟晶振等,电路中STM32 外围的电路原理图设计如图5 所示。其中,左侧板为STM32F407ZGT6 核心板,右侧两个板为DP83640 芯片及其接口电路。核心板引出串口线,通过串口转USB 连接于电脑上位机,系统总体由电脑供电,供电电压为5 V。

图5 以太网控制电路搭建

3.3 接口电路设计

3.3.1 MDIO 接口

在本设计中对PHY 芯片的读写通过MDIO 接口来实现,该接口包括MDC 和MDIO 两条信号线,用来管理配置PHY 芯片,通过读写寄存器来获取网卡芯片的状态以及MDC 时钟信号。

3.3.2 RMII 接口

MII 即“媒体独立接口”,也叫“独立于介质的接口”,它是IEEE-802.3 定义的以太网行业标准。该接口是以太网物理层和链路层的一种连接方式,而RMII 接口是MII 的简化版,它减少了接口个数同时提高了时钟速率。图6 为RMII 接口电路设计。TX_EN:发送使能信号,置高有效;TXD[1:0]:发送数据端口,当TX_EN 信号无效时,PHY 忽略传输的数据;CRS_DV:此信号是RX_DV 和CRS 复用信号,用作接收数据的触发信号;RXD[1:0]:接收数据端口,数据在CRS_DV 信号有效时使能;MDC,MDIO:即以太网管理接口(MDIO),上文已有提及这里不再详述;REF_CLK:收发数据使用的时钟信号。

图6 RMII 的接口设计

3.3.3 串行接口

上位机和控制系统在本文中使用异步串行通信接口,在实际设计采用TTL 正逻辑电平(3.3 V),并通过USB 转串口模块连接于电脑。设置波特率为115 200 bit/s,停止位为1 bit,数据位为8 bit,无奇偶校验位。

4 软件设计

4.1 整体流程设计

控制系统运行于RTOS 操作系统,内部通过LWIP 协议栈完成PTP 时间同步帧的发送接收,同时,DP83640 的初始化分为两个部分:以太网接口的初始化和PTP 协议相关内容的初始化,两部分内容都通过MDIO 配置DP83640 相关寄存器完成。DP83640 的以太网接口的初始化包括获取以太网接口初始状态、调整以太网工作模式为100 Mbit/s、MAC 接口配置为RMII。对于PTP 协议相关内容的初始化,包括使能PTP 时钟、配置DP83640 时钟为内部时钟(125 MHz,分频系数为250)、使能时钟输出、使能UDP/IPv4 的Sync 同步帧发送时间戳标记、使能UDP/IPv4 的时间戳接收事件触发、基于单个GPIO 事件对DP83640 内部时钟进行初始的相位调整。

当上述工作完成后,控制系统开始对PTP 协议进行初始化,配置PTP 运行的具体细节,包括主从时钟分配、主时钟发送Sync、Announce 帧的时间间隔并开启相关定时器、配置PTP 运行状态机的初始状态。在此之后,下位机创建PTP 处理线程,该线程通过运行一个具有多个状态的状态机,并通过UDP 数据帧接收触发和上述定时器触发两种方式来运行状态机的状态切换和时间同步。

图7 STM32F407 运行程序的整体流程

4.2 LWIP 以太网协议栈搭建及测试

LWIP 协议实现的重点是在保持主要功能的基础上减少对RAM 的占用。一般它只需要很小的内存空间即可运行,这使LWIP 协议栈适合于小型嵌入式设备。用该协议实现UDP 通信测试。

4.2.1 基于LWIP 的电脑端UDP 通信测试

本文对LWIP 的UDP 通信进行了测试,搭建了一对一UDP 通信测试方案。电脑端IP:192.168.1.1 端口:8089 UDP 传输;STM32 IP:192.168.1.100 端口:8089;测试方法:用STM32 向电脑端重复发送数据0x97,一次数据包大小为1 024 byte,用电脑的任务管理器记录网速。网速测试数据见表1,平均速率为98.0 Mbit/s,基本达到DP83640 带宽极限。

表1 电脑端数据传送网速

4.2.2 基于LWIP 的STM32 一主一从UDP 通信测试

STM32 主IP:192.168.1.1 端口:8089 UDP 传输;STM32 从IP:192.168.1.100 端口:8089;测试方法:主对从重复发送数据0x97,一次数据包大小为1 024 byte,用STM32 记录每974×10 240 个数据包的时间,并向电脑端串口发送状态,(共10 Mbyte,每次包含50 byte 帧头)。测试数据见表2,由此可得接收数据平均网速:63 Mbit/s。

表2 一对一数据传送网速

4.3 DP83640 PTP 相关参数获取及修改

4.3.1 DP83640 时间戳获取及修改

时间戳读写功能可通过DP83640 的Page4 的PTP_TDR 寄存器实现,对于时间戳读写,需要先在PTP_CTL 中开启读或写,此时读或写的时间戳即为此时的时间,由于PTP_TDR 寄存器仅为16 位,读写需要分四次进行,以依次读写纳秒低16 位,纳秒高16 位,秒低16 位,秒高16 位。

对于PTP 协议而言,仅读写时间戳是不够的,为此DP83640 有专门的寄存器存储发送接收的时间戳和记录发送和接收PTP 消息帧的时间。

4.3.2 DP83640 时间戳标记功能的配置

DP83640 可以识别Sync 和Delay_Req 同步帧,并在发送同步帧的同时修改报文的时间戳。该功能可以在以太网物理层给Sync 和Delay_Req 帧打上时间戳,从而消除在链路层、网络层、传输层上组帧的时间延时,极大地提升时间同步的精度。该功能可通过配置PTP_TXCFG0 寄存器来实现,本次设计时,将PTP_TXCFG0 寄存器的Bit0 位设为1,使能发送时间戳标记功能,Bit4,Bit3,Bit2,Bit1 四位置为0010,表明采用IEEE 1588v2 版本;Bit7,Bit6,Bit5:分别使能为链路层,IPv6,IPv4 各层的PTP 同步帧打时间戳,将Bit15 置1 在Sync 帧中打入发送的时间戳;将Bit13 置1 在Delay_Req 帧中打入发送的时间戳;其余保持默认配置。

4.4 PTP 协议帧的发送及接收处理及数据抓取

PTP 时间同步,首先要实现PTP 报文的组帧、发帧和解帧。时间同步的发送接收可通过先由STM32 完成组帧,再由DP83640 完成时间戳记录和写入对应PTP 帧的时间戳位置。当时间同步帧准备好后,对于发送时间同步帧,则调用LWIP 协议栈的UDP_Send 函数将上述内容发送出去即可。对于接收时间同步帧,则需要使用将相应的接收函数以回调方式绑定在UDP_PCB 中。

为了更直观地观察PTP 帧数据,本文采用WireShark 软件进行数据抓取,由于PTP 时间同步帧在IPv4 层采用组播方式,主从端及电脑监控端接入交换机即可抓取数据帧。抓取到的结果如图8 所示,里面记录了详细的数据包信息。

图8 抓取数据包信息

5 测试及结果分析

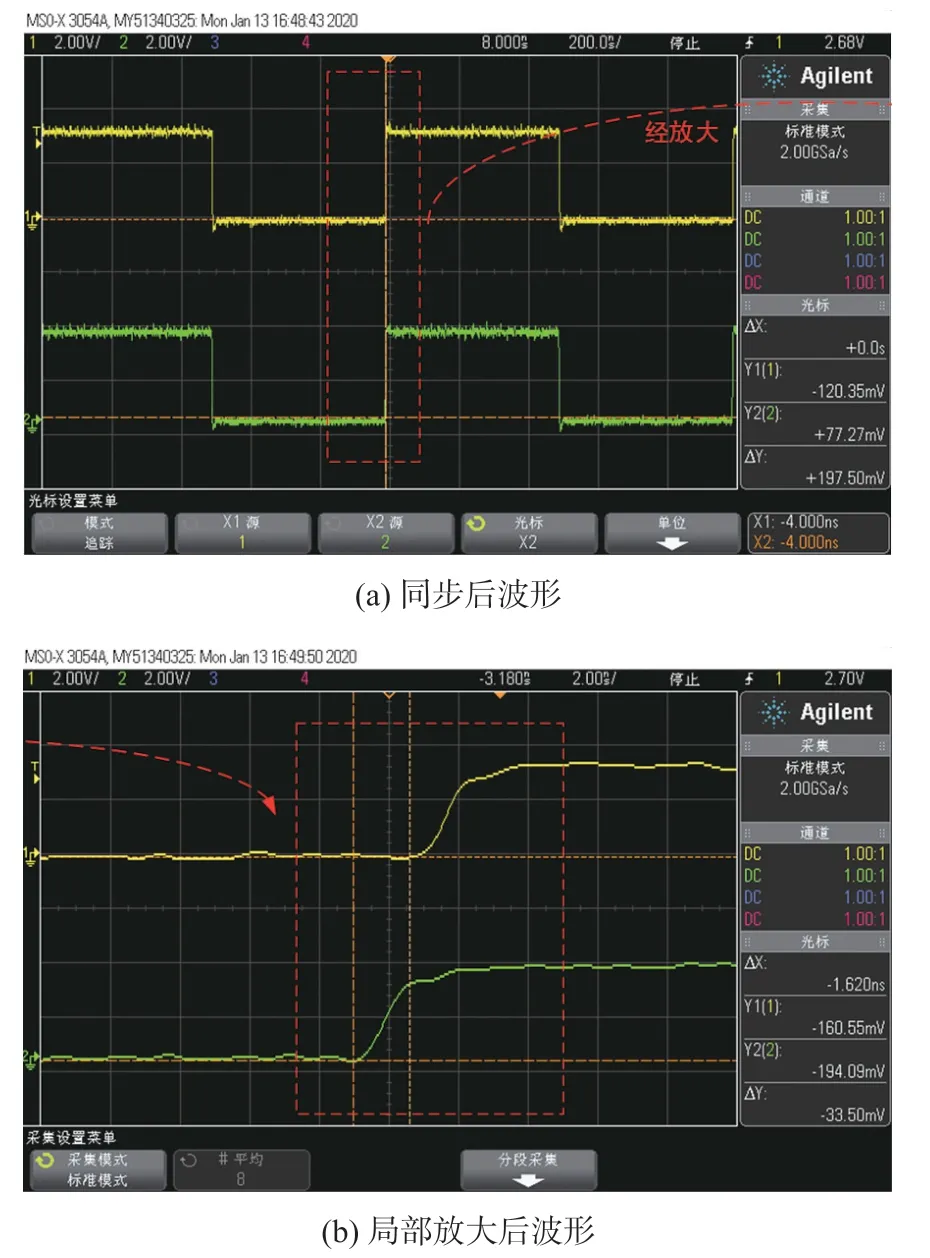

搭建系统如图9 所示,主从时钟作为两个节点,二者均通过网线相连于交换机,连接上电源,分别烧录没有设置时间戳和设置时间戳的程序,用示波器探头对准主从时钟的DP83640 的时钟输出管脚,记录有无时间戳时二者的对比,如图10 所示为没有烧录时间戳时的主从时钟输出,可看出此时主从时钟的时间差为170 ns,记录完之后,再将加了时间戳的程序烧录,用示波器测二者的时钟差,结果如图11所示,可看出,同步之后,主从时钟的时间差仅有1.62 ns,相比于未同步前的有大大提高。

图9 测试系统搭建

图10 未同步前波形

图11 同步后波形

6 结论

本文从分布式系统实时性测试需求出发,设计了基于IEEE 1588 精密时钟同步系统,分别通过软件标记时间戳和硬件标记时间戳的方法,大大提高了时钟同步的精度,同时也提高了分布式系统的可靠性。本文所介绍的时钟同步系统工作稳定,已投入到实际使用中,具有较好的实用价值。