基于CPLD 的FPGA 多重配置方法实现

2022-05-30韩留军郝国锋

韩留军,姚 尧,郝国锋,赵 参

(1.无锡华普微电子有限公司,江苏无锡 214035;2.中科芯集成电路有限公司,江苏无锡 214072)

1 引言

无线通信系统中,由于应用环境的改变,系统常常要运行在多种不同的工作模式下,这使得现场可编程门阵列(Field Programmable Gate Array,FPGA)的功能设计复杂度和资源使用率越来越高。对FPGA 进行多重配置,根据需要在不同工作模式下的FPGA 中运行相应的程序,可以使有限资源的FPGA 利用率提高,程序功能设计的复杂度降低,系统运行更加灵活[1]。一般利用中央处理器(Central Processing Unit,CPU)或数字信号处理器(Digital Signal Processor,DSP) 读取Flash 中的数据加载到FPGA 中,这样会提高硬件设计成本,增加功耗。本文提出了使用复杂可编程逻辑器件(Complex Programmable Logic Device,CPLD)对FPGA 进行多重配置的方法,CPLD 作为主控芯片,把多套配置文件存储到Flash 中,同时读取里面的配置文件加载到FPGA 中,该方案使得对FPGA 的配置文件升级方便快捷,大大提高了FPGA 的资源利用率,节约了设计成本[2]。

2 系统总体设计

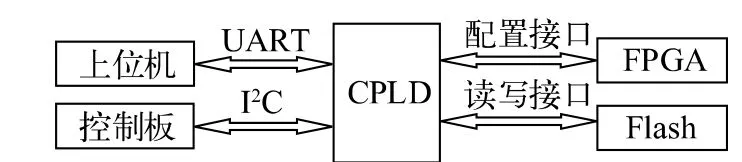

2.1 系统设计

系统设计总体架构如图1 所示,系统主要由CPLD、FPGA 和Flash 芯片组成,本系统使用的是Xilinx 公司的CPLD 和FPGA 芯片,CPLD 使用的是CoolRunner II 系列芯片,FPGA 使用的是Virtex4 系列芯片,Flash 为国微的256 Mbit 芯片。CPLD 通过串口接收上位机发送的指令和要存储的配置文件,CPLD解析指令后判断对Flash 的哪一段存储区域进行擦除,擦除完毕后,把发送过来的配置文件存储到擦除后的Flash 区域中。Virtex4 系列的XC4VSX55 芯片对应的配置文件大小为2.71 MB,Flash 中最多可以存储11 个FPGA 的配置文件。控制板通过集成电路总线(Inter-Integrated Circuit,I2C)和CPLD 进行通信,发送配置指令信息,CPLD 接收到指令后,读取对应的Flash 存储区域内的配置文件加载到FPGA 中,完成对FPGA 的重配置[3]。

图1 系统总体框图

2.2 配置模式和流程

FPGA 根据不同的设计需求,提供了不同的配置模式可供选择,主要有主串模式、从串模式、主SelectMAP 模式、从SelectMAP 模式、联合测试工作组(Joint Test Action Group,JTAG)模式、主SPI Flash 模式和从SPI Flash 模式等。本文使用的是从SelectMAP模式,此模式的配置速度相对来说比较快,配置时钟和数据都由CPLD 提供,数据位宽为8 位[4]。

尽管有不同的配置模式,但FPGA 的配置启动流程是一样的。FPGA 的配置步骤包括:器件上电、清除配置存储器、采样模式引脚、同步、器件标识号(Identity Document,ID)检测、加载配置数据、循环冗余校验(Cyclic Redundancy Check,CRC)和启动序列。在加载配置数据阶段,主要是通过CPLD 提供配置时钟和8 位宽的配置数据给FPGA 的专用配置管脚,把配置文件加载到FPGA 中[5]。

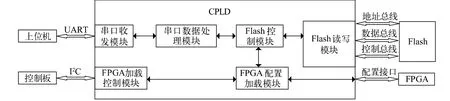

3 设计实现

系统设计框图如图2 所示,CPLD 是整个配置过程的核心,CPLD 通过串口与上位机互连,通过I2C 接口与控制板互连,Flash 的地址总线、数据总线和控制总线连接到CPLD 上,CPLD 可以擦除、读和写Flash。FPGA 的专用配置管脚连接到CPLD 上,上电后,CPLD 通过控制板接收的指令,把对应的Flash 中的配置文件通过FPGA 的专用配置管脚对FPGA 进行加载配置[6]。配置文件大小为2.71 MB,配置时钟为25 MHz,配置加载时间为1 s 左右。按照功能说明,CPLD 中主要包括串口收发模块、串口数据处理模块、Flash 控制模块、Flash 读写模块、FPGA 加载控制模块和FPGA 配置加载模块。图3 为系统的控制状态转换框图,从图中可以看到数据流的状态[7]。

图2 系统设计框图

图3 控制状态流程

串口收发模块主要是实现与上位机进行串口数据的交互。上位机通过串口发送、接收指令和配置数据,串口收发模块完成串转并和并转串的功能。

串口数据处理模块的接收部分解析串口传输过来的数据,按照接收指令进行相应的操作。比如接收到存储地址的指令,就把接收过来的配置文件和要存储的位置一起发送给Flash 控制模块,以便顺利存储数据。发送部分是把反馈的状态信息回传给上位机,上位机通过状态信息,判断发送的指令和数据是否正确。

Flash 控制模块主要是完成对Flash 读写模块下发擦除、读和写的控制指令。此模块根据接收到的指令信息,选择要存储配置文件的首地址[8]。然后从此地址开始下发擦除指令,等待擦除完毕后,上传擦除完毕信息给上位机,上位机再下发配置文件数据,此模块接收到数据后,开始启动写数据指令给Flash 读写模块。当要加载配置文件给FPGA 时,此模块发送读数据指令给Flash 读写模块,读取Flash 中的配置文件加载到FPGA 中。

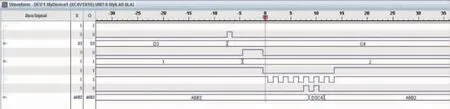

Flash 读写模块主要是完成对Flash 具体的擦除、读和写操作的指令和数据的过程,按照Flash 要求的时序和指令信息操作Flash,Flash 的读写时序要求如图4 和图5 所示,可以完成对Flash 的正常读写操作。

图4完成了对Flash 的基本写操作过程,从图中可知,P_flag_c 为写入数据的标志,P_data_c 为要写入的数据,它们把准备写入的数据准备好。App_req_c 为操作Flash 的标志信号,当此信号为高时,App_cmd_c的值为2,表示要启动写Flash。在启动写Flash 之前,先给App_cmd_c 的值为1,表示先擦除Flash,擦除完毕后,再写入Flash。通过片选信号CE_FLASH、写使能信号WE_FLASH、写数据有效标志app_wvalid_c 信号和写数据app_wdata_c 信号,可以把之前准备好的数据写入到Flash 中。从图4 可以看出,写入的数据为A6B2 和D3C4。

图4 Flash 的写操作过程

图5完成了对Flash 的基本读操作过程,从图5可知,App_req_c 为操作Flash 的标志信号,当此信号为高时,App_cmd_c 的值为3,表示要启动读Flash。通过片选信号CE_FLASH、读使能信号OE_FLASH、读数据有效标志app_rvalid_c 信号和读数据app_rdata_c信号,可以得到读出的数据,从图5 可以看到之前写入的数据被正确读出。

图5 Flash 的读操作过程

FPGA 加载控制模块主要接收控制板通过标准的I2C 协议给CPLD 下发的配置指令信息,CPLD 首先解析出I2C 协议中的地址信息,如果是此设备的地址,则继续获取I2C 中的数据部分,此数据包含了FPGA 加载配置的页码信息,CPLD 通过页码信息,读取Flash相应地址段中FPGA 的配置文件数据,把数据传输给FPGA 配置加载模块,对FPGA 进行加载配置。

FPGA 配置加载模块接收到配置指令后,按照FPGA 的配置流程,输出配置时钟和数据,把要加载的配置文件通过从SelectMAP 模式加载到FPGA 中,完成对FPGA 的配置加载。

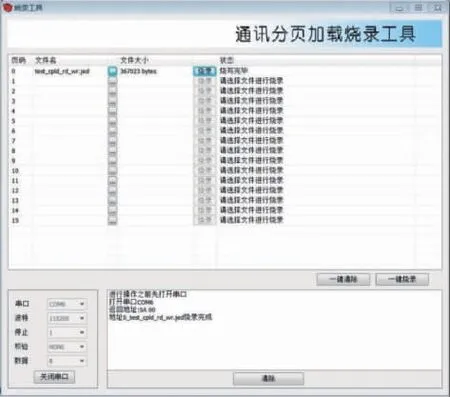

上位机软件通过串口与CPLD 连接,主要功能是通过串口收发指令和数据。设置好串口参数后打开串口,把FPGA 的配置文件添加到对应的页码中,点击烧录按键,CPLD 通过传输过来的指令,开始擦除对应页码的Flash 区域,擦除完毕后,同时反馈相应的信息给上位机。上位机开始把FPGA 配置文件数据发送出去,CPLD 接收到数据后,把数据缓存后存放在Flash相应的区域中[9]。当配置数据写入完成后,反馈给上位机状态信息,显示在界面上,如果配置失败,则重新配置。上位机烧录成功界面如图6 所示。

图6 上位机烧录成功界面

对于FPGA 的配置来说,控制板的主要作用是上电后通过I2C 给CPLD 下发配置指令信息,CPLD 解析出指令后,把对应Flash 中的配置文件数据传输到FPGA 的专用配置管脚上[10]。在系统正常运行时,通过控制板下发不同的I2C 指令,FPGA 就会被加载不同的配置文件,这样就实现了对FPGA 的重配置。

4 结论

本文实现了基于CPLD 对FPGA 的多重配置方法,该方法以CPLD 为核心,可以方便快捷地更新FPGA 的配置文件,调试和系统升级方便。在系统运行过程中,可以任意切换FPGA 的配置文件进行加载。该方法通用性强,可以用在不同的工程应用领域,特别是在软件无线电平台上有较好的应用前景。