3D 堆叠封装热阻矩阵研究

2022-05-30张振越蒋玉齐朱思雄杨中磊

黄 卫,蒋 涵,张振越,蒋玉齐,朱思雄,杨中磊

(1.中国电子科技集团公司第五十八研究所,江苏无锡 214072;2.中微高科电子有限公司,江苏无锡 214035)

1 引言

随着集成电路制造技术的飞速发展、市场需求的高速增长以及芯片在多领域的广泛应用,芯片功能多样化、尺寸小型化和高性能已成为集成电路主要的发展方向[1]。系统级封装将具有一定功能的系统或子系统封装在芯片内部,并通过芯片端口电信号的输入与输出实现相应的功能。芯片端口数量在一定程度上决定了芯片的性能,相较于金线键合(Wire Bonding,WB)封装技术,倒装(Flip chip,FC)封装技术的应用在一定程度上增加了单颗芯片封装体I/O 接口数量[2]。高频次电信号的输入与输出导致芯片热量聚集,在一定温度范围内,电子元器件的温度每上升2 ℃,可靠性降低10%。导致设备损坏、无法正常工作的因素中,电子元件温度导致器件可靠性降低占有很大的比重,因此越来越受到重视。

相较于单芯片封装技术,多芯片组件可在一个封装体内封装多个芯片,有效提高了芯片的封装密度[3]。针对单芯片封装体,可以通过热阻值来衡量器件的散热能力,封装器件的热阻有相应的JEDEC 测试、仿真标准以及理论计算,封装器件热阻具有一套成熟的计算体系,芯片结温计算准确度具有一定的保障。多芯片封装由于内部有多个热源,若采用单芯片封装体热阻计算方法,会导致一个封装体出现多个热阻值,无法准确计算封装体的散热能力,且封装体内部芯片之间的热耦合与热阻扩散将被忽略,造成计算温度与实际温度偏差较大,降低仿真结果的准确性[4]。

多芯片封装体封装器件的类型有多种。针对3D封装器件的结温计算,芯片工作状态下产生的热量主要以热传导的方式传递,小部分的热量以热辐射、热对流向外散发,从而实现封装体器件的热量平衡。本文根据封装体器件的散热特性建立3D 堆叠封装器件的热阻矩阵,再对热阻矩阵进行验算,分析封装器件模型的热阻矩阵准确性。

2 单芯片结构模型

2.1 热阻测试

针对单芯片CBGA 封装类型结构,使用热阻测试仪器测试热阻。热阻测试加热电流为1.0 A,测试电流为1 mA,芯片加热功率为3.551 W,封装器件底部贴于导热性能较好的铜块热沉上。将电路引脚反接,电路温敏系数(K)测试拟合曲线如图1 所示,K为-2.0262 mV/℃。

图1 K 拟合曲线

双界面法测试热阻需要两次测量,并将结构函数曲线分离点作为器件的结-壳热阻值Rjc。图2 为热阻测试所得到结构函数拟合曲线,结构函数曲线分离点均在0.50~1.51 区间范围,表明热阻测试数值在该区间范围内。图3 为根据图2 结构函数拟合曲线所得到的结壳热阻,阻值为1.02 ℃/W。

图2 热阻测试结构函数拟合曲线

图3 结构函数拟合曲线的结壳热阻值

2.2 热阻仿真

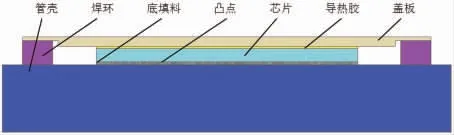

对上述热阻测试芯片进行热阻仿真,图4 为单芯片结构模型,表1 为芯片内部结构的材料属性,芯片与上部的盖板涂覆有导热胶,可将芯片产生的热量导向盖板。封装体的热量传递路径有3 条:绝大部分热量以热传导的方式向盖板散热;小部分热量通过凸点与底填料向管壳导热,经焊环将热量导入盖板散热;此外还有极小部分的热量以热辐射的方式直接传递到盖板上。

表1 封装体器件内部结构材料热属性

图4 单芯片结构模型

不考虑封装体内部芯片的辐射热影响,单芯片热阻根据其结构模型以及热传导路径,构成的热阻网络模型如图5 所示。

图5 单芯片热阻传递路径

芯片结温Tj、环境温度Ta、芯片热功率P以及封装体热阻R总之间的关系满足式(1):

热阻理论计算公式如式(2)所示:

式中,L为结构热传递厚度,K为结构材料的导热系数,S为热传递横截面面积。

当热量由芯片经过导热胶将热量传递到盖板上,其封装器件总热阻阻值R为:

当热量经过凸点、底填料、管壳以及焊环传递到盖板上,由于底填料与凸点属于热阻并联结构,因此封装器件总热阻值R为:

封装体芯片与盖板之间涂覆有导热胶,因此使用式(1)、(2)进行封装器件的热阻计算,为1.062 ℃/W。

芯片倒装类封装体,凸点在实现管壳与芯片之间电信号传递的同时也会产生热量,其热量的堆积将造成芯片温度升高,并随着单位时间信号交换频次的递增,温度逐渐上升。因此,在仿真中将芯片与凸点的接触底面作为热源面,并按照热阻测试芯片的发热功率为3.551 W 设置。此外,封装器件的顶部作为25 ℃的恒温面,热阻仿真结果如图6 所示。

图6 热阻仿真结果

仿真结果中芯片的结温为28.3 ℃,低温恒温为25 ℃,芯片发热功率为3.551 W,根据式(1)计算出封装体芯片到盖板的热阻阻值为0.93 ℃/W。对比理论计算、测试、仿真得到的热阻值,其误差均在10%之内,表明该仿真设置边界条件能够保证封装体器件热阻仿真分析的准确性。

表2 测试、理论计算及仿真热阻值对比

3 多芯片堆叠模型

3.1 芯片堆叠结构

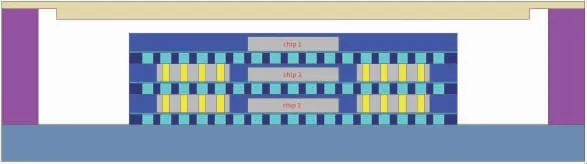

3D 芯片封装可在结构上将芯片堆叠,从而有效减小了封装体轴向横截面面积。3D 芯片堆叠结构如图7所示,芯片堆叠通过硅通孔(TSV)、再布线层(RDL),实现芯片之间的信号数据传递连通。

图7 3D 芯片堆叠结构示意图

单芯片组件热量的传递中,芯片作为唯一的热源器件,产生的热量由上向下传递,并通过底部器件散热,达到整个单芯片封装体内部的能量平衡[5]。与单芯片封装体不同,多芯片封装体内部含有多个发热体,热量的传递方式有热传导、热辐射和对流换热,在空间上是一种三维传递方式[6]。与多芯片组件(MCM)封装技术不同,3D 芯片封装技术实现芯片堆叠结构无论采用何种方式的多芯片封装,热量在封装体内部传递会造成其他芯片温度升高,即在一个封装体内部2 个或2个以上芯片同时发热时,除芯片本身产生的热量外,发热芯片之间还存在热扩散与耦合,从而导致温度高于其单独的理论计算温度[7]。

3.2 3 层芯片堆叠模型

对于多芯片组件,无论是芯片平铺或者堆叠,最有效的降低芯片结温的方式是将热源沿着最短的热量传递路径传递到散热部位,极大地降低了热源相互之间的热耦合效应[8]。对于集中热源MCM 封装模型,影响多芯片热阻的因素有热源功率、热源尺寸、对流换热系数、导热系数、热源相互之间的距离等。为估测多芯片封装体内部各芯片结温大小,在MCM 技术封装的热阻矩阵基础上,对三层芯片堆叠结构热阻矩阵进行分析,构建芯片堆叠热阻矩阵。

芯片堆叠结构模型如图8 所示,芯片置于RDL上,并采用塑封料将芯片包裹,RDL 底部与焊球接触,第一层与第二层芯片设计有TSV 结构,用于实现上、下部位区域上焊球之间信号的传递。

图8 三维芯片堆叠结构

3.3 堆叠芯片热阻矩阵

相较于单芯片热阻计算,多芯片热阻矩阵能够考虑多芯片封装内部多个热源之间的热耦合与热扩散,对于多芯片封装技术来说,由于内部封装器件热源功率的不同,芯片结温也具有明显的差异性[9]。因此,预测芯片的结温对提高多芯片封装组件稳定性具有非常重要的意义。随着工程传热学仿真技术的迅速发展,使用模拟技术分析多芯片组件的热耦合效应能够有效预测芯片结温与温度分布,极大地提高了多芯片封装技术的热学可靠性[10]。

3 层芯片堆叠结构内部材料的热属性参数如表3所示,其中简化了RDL 结构热属性,有利于降低仿真计算量。

表3 堆叠芯片结构材料热性能

为保证仿真结果的准确性,仿真条件加载时参照第2 节,芯片底部作为热源加载面,芯片的加载功率均设置为1 W。热量从芯片向下传递,并通过管壳底面向外散热,维持整个封装器件内部的热平衡。在仿真时将陶瓷管壳底部作为恒温面,并设置温度为25 ℃。图9、图10 分别为芯片1 发热、芯片1 和芯片2 共同发热2 种工况的热仿真云图。

图9 芯片1 发热器件温度分布

图10 芯片1、芯片2 发热器件温度分布

由于该封装是一种芯片堆叠结构,芯片1 产生的热量经过芯片2、3 向底部管壳传递,芯片2 产生的热量经过芯片3 向底部管壳传递。两芯片同时发热时,其热量传递路径共享,导致其在能量传递过程中产生热交叉耦合效应。对比芯片1 单独发热与芯片1、芯片2 同时发热两种工况仿真结果,对于芯片1 来说,由于芯片2 发热使得两个芯片存在热量耦合,导致其温度上升近24.23 ℃。仿真分析结果表明,用单芯片的热阻理论模型计算多芯片封装器件的内部芯片结温,忽略了芯片之间的热耦合效应,会产生非常大的偏差。

封装器件内部分别有芯片1、芯片2 和芯片3 三种芯片作为热源,其共同发热时必定会产生热耦合,导致芯片的结温高于芯片单独发热产生的温度。为准确计算多芯片封装体内部芯片的结温,引入热阻矩阵概念[11],建立热阻矩阵模型,利用热量传递线性叠加原理计算多芯片封装体内的不同芯片结温大小。热阻矩阵模型的表达式为:

式中,Tn为芯片n的结温;Pn为芯片n的功率大小;Ta为环境温度。

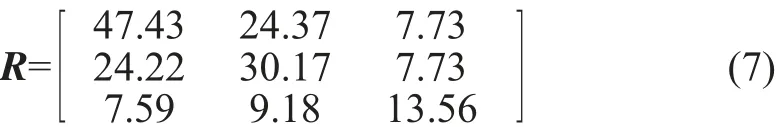

定义热阻矩阵R 为:

式(6)中,Rnn表示芯片n依照单芯片热阻模型计算得到的芯片热阻,即表明芯片n本身热阻;Rij表明芯片j对芯片i造成的温度影响。根据前面对仿真边界及热加载条件进行的设置,并按照上述热阻矩阵计算模型,对芯片分别发热所对应工况下封装体内部芯片的结温进行记录。

依据表4,对3D 封装芯片进行热阻计算,其热阻矩阵如式(7)所示:

表4 不同芯片发热工况下封装体内芯片结温

从式(7)中数据可以得出,对于单芯片发热,不同芯片发热由于其热传递路径不同,如R11、R22和R33,其热量均向底部恒温面散热,其热传递路径变短,故其芯片热阻值逐渐减小;对于耦合热阻,虽然芯片的尺寸、功率均相同,但由于其堆叠结构导致其耦合热阻具有一定的差异性,如R23、R32,这表明堆叠芯片结构中芯片i对芯片j的耦合热阻与芯片j对芯片i的耦合热阻由于空间位置的不同具有一定的差异性。

4 芯片堆叠热阻矩阵验证

当封装体内芯片都处于工作状态时,假设芯片1功耗为0.5 W,芯片2 功耗为0.8 W,芯片3 功耗为0.3 W,其对应的温度分别为70.38 ℃、64.07 ℃、40.42 ℃,有限元热仿真结果如图11 所示。

图11 封装器件热仿真云图

由表5 可以看出,3D 堆叠结构通过热阻矩阵计算得出的内部各芯片结温与仿真芯片结温的误差在1%以内,多芯片封装组件内部芯片在不同的功率下,其热阻矩阵计算得出的结温可以保证芯片结温结果的准确性,验证了该热阻矩阵计算方法对3D 芯片堆叠封装器件具有高度的适用性。

表5 芯片结温计算值与仿真值对比

5 结论

本文以单芯片封装器件模型为基础,通过计算和测试结果验证仿真边界条件的加载,确定仿真加载条件。对3D 芯片堆叠封装组件芯片底部采用相同的热源加载面,对比单芯片发热与双芯片发热,分析多芯片之间热耦合效应导致的温升,并在此基础上建立模型确定3 层堆叠芯片热阻矩阵。通过改变芯片的功率,对封装体芯片结温仿真与热阻理论计算进行误差分析,验证了3D 封装热阻矩阵的准确性。