基于FPGA的RISC微处理器设计

2022-05-26陈剑锋学江煜郭湘津

陈剑锋 学江煜 郭湘津

摘 要:针对传统CISC指令集复杂、硬件开发难度大、运行效率低、体系架构复杂等关键技术问题,设计了一种基于FPGA的32位RISC微处理器。通过分析微处理器的基本架构和流水线数据处理方法,基于VIVADO软件对所设计的RISC微处理器的软核进行了功能仿真验证,采用XC7A75T芯片为控制核心,完成了RISC处理器系统硬件搭建。仿真结果表明,所设计的RISC-CPU运行稳定,效率高,层次合理,能实现各种指令的预期功能,指令执行速度快,达到了预期设计目标。

关键词:FPGA;RISC-CPU;MIPS指令集;流水线;嵌入式

中图分类号:TP302.2 文献标志码:A 文章编号:1671-0797(2022)10-0022-05

DOI:10.19514/j.cnki.cn32-1628/tm.2022.10.007

0 引言

近年来,精简指令集计算机RISC(Reduced Instruction

Set Computer,RISC)技术不断成熟,其应用范围也越来越广泛,如手持电子设备、家用电器、工业控制、机器人等领域。以往的复杂指令集计算机CISC(Complex Instruction Set Computer,CISC)其复杂指令的使用率低,运算速度慢,硬件架构庞大,开发周期长,导致微处理器的总体性能下降,无法满足处理速度快的高性能要求。RISC采用简单的指令集系统,嵌入式处理,架构简洁,集成度高,不仅优化了微处理器的内部结构,而且缩小了体积,提高了性能,便于片上系统开发,灵活方便。因此,RISC微处理器的研究具有理论和实际意义。

目前,针对RISC微处理器的系统设计方案研究成为众多学者关注的热点。

郝振和等人[1]提出了一种基于AHB总线的RISC-V微处理器,采用嵌入式系统设计,在功耗和性能上与Cortex-M0处理器相当。

雷少波等人[2]采用4级流水线的数据处理结构设计了一款16位RISC嵌入式微处理器,解决了硬件结构在指令执行过程中延迟的问题。

刘览等人[3]提出了一种8级流水线的32位微处理器,解决了微处理器分支冒险问题,并在FPGA硬件平台和Quartus Ⅱ软件平台上进行验证。

黄旺华等人[4]基于FPGA流水线设计了一种RISC微处理器,针对数据相关性的写后读问题,采用“旁路”技术来解决,提高了处理速度,其最高时钟频率达到74.59 MHz。

赵坤等人[5]基于FPGA实现一个完整的SoC-FPGA平台,采用精简3级流水线数据处理结构,带有静态分支预测功能,该SoC的工作频率为50 MHz。

基于现场可编程门阵列(Field-Programmable Gate Array,FPGA)的32位RISC微处理器的设计,其目的在于简化硬件电路结构,提高计算机数据处理速度和系统运行效率,将中央处理器(Central Processing Unit,CPU)擅长复杂流程控制和FPGA并行数据处理的特点相结合,使得微处理器架构简洁,指令集系统简单,缩短硬件开发周期,降低硬件开发难度,提高CPU整体性能。

1 RISC-CPU体系结构

1.1 RISC-CPU的基本架构

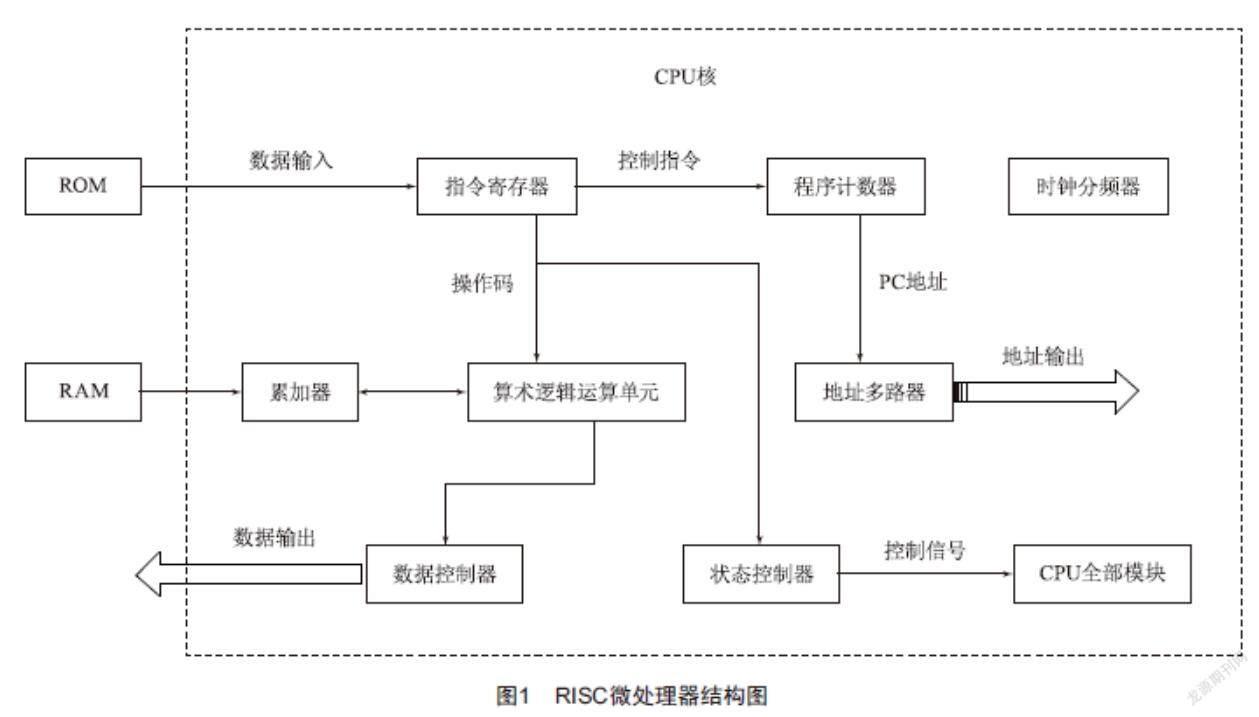

本文采用冯·诺依曼结构来实现RISC微处理器设计[6]。如图1所示,所设计的RISC微处理器主要由指令寄存器、程序计数器、地址多路器、状态控制器、累加器、算术逻辑运算单元、数据控制器、时钟分频器八大基本部件组成。其中,时钟分频器可为CPU各个部件提供时钟源信号,保证系统的正常运行。累加器用于存储RAM传输来的数据信息和当前的运行结果。程序计数器在当前的指令结束后,立即提供下一条指令的地址,保证指令有序执行。

地址多路器中的每个指令周期共有8个时钟,前面4个时钟从ROM中读取指令,后面4个时钟则从RAM中读取指令。算术逻辑运算单元主要用于处理操作码信息,进行基本逻辑运算。

1.2 MIPS指令集

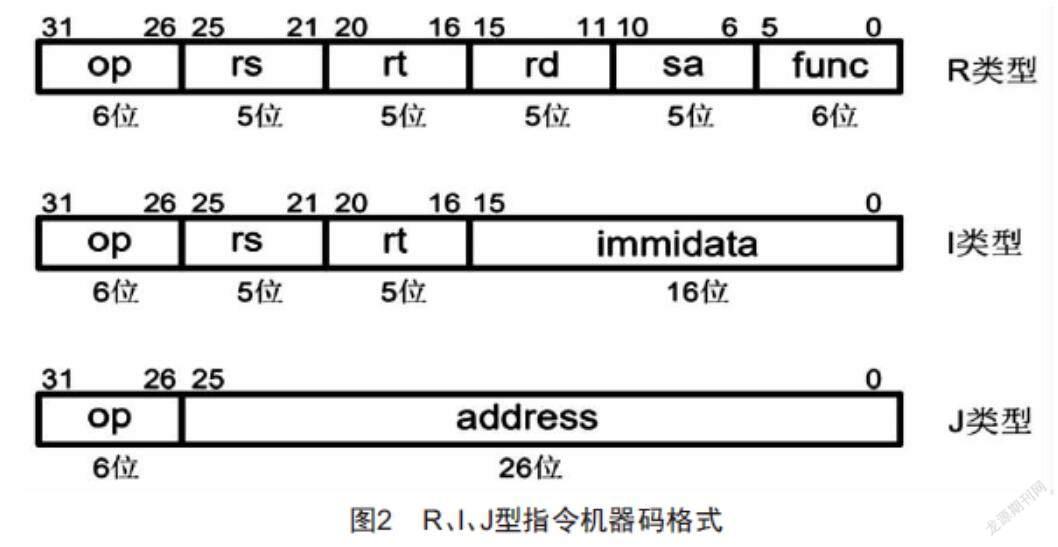

MIPS[7](Million Instructions Per Second)是一种高效的指令架构,其最大特点在于简化了CISC的庞大指令集,在指令数目和格式上进行了优化,极大地提高了微处理器的数据处理效率。MIPS指令集的指令数量比较少,格式固定且整齐,缩短了指令的执行时间,更易于在硬件上实现数据的流水线处理。如图2所示,MIPS32有三种指令机器码格式,分别为R型(寄存器类型)、I型(立即数类型)和J型(跳转类型)。MIPS架构设计非常简洁、合理,内核中可以加入自定义的指令,数据处理量大的任务由编译器完成,从而保证了处理的高效性。

1.3 流水线技术

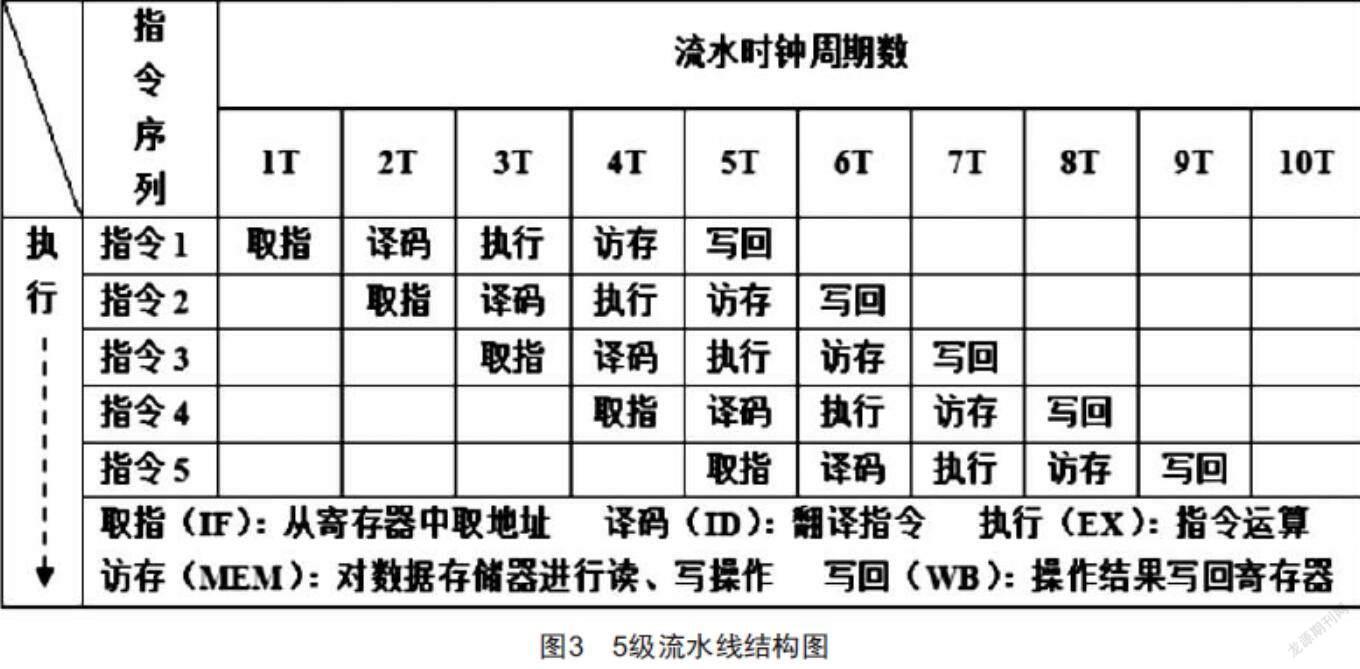

本文设计的RISC微处理器采用5级流水线的技术方案,能实现多条指令并行处理,提高了指令的执行速度。5级流水线结构图如图3所示,所谓“5级流水线”是指在执行指令过程中需要经过5个流水段,每个流水段完成不同的任务,分别为取指、译码、执行、访存和写回。假设,执行5条指令,采用单时钟周期执行单条指令,则需要15T;若采用流水线技术,仅需9T就能完成。因此,相同时间内,流水线技术提高了微处理器指令的执行速度,可作为优化微处理器性能的关键技术。

2 RISC-CPU系统的硬件实现

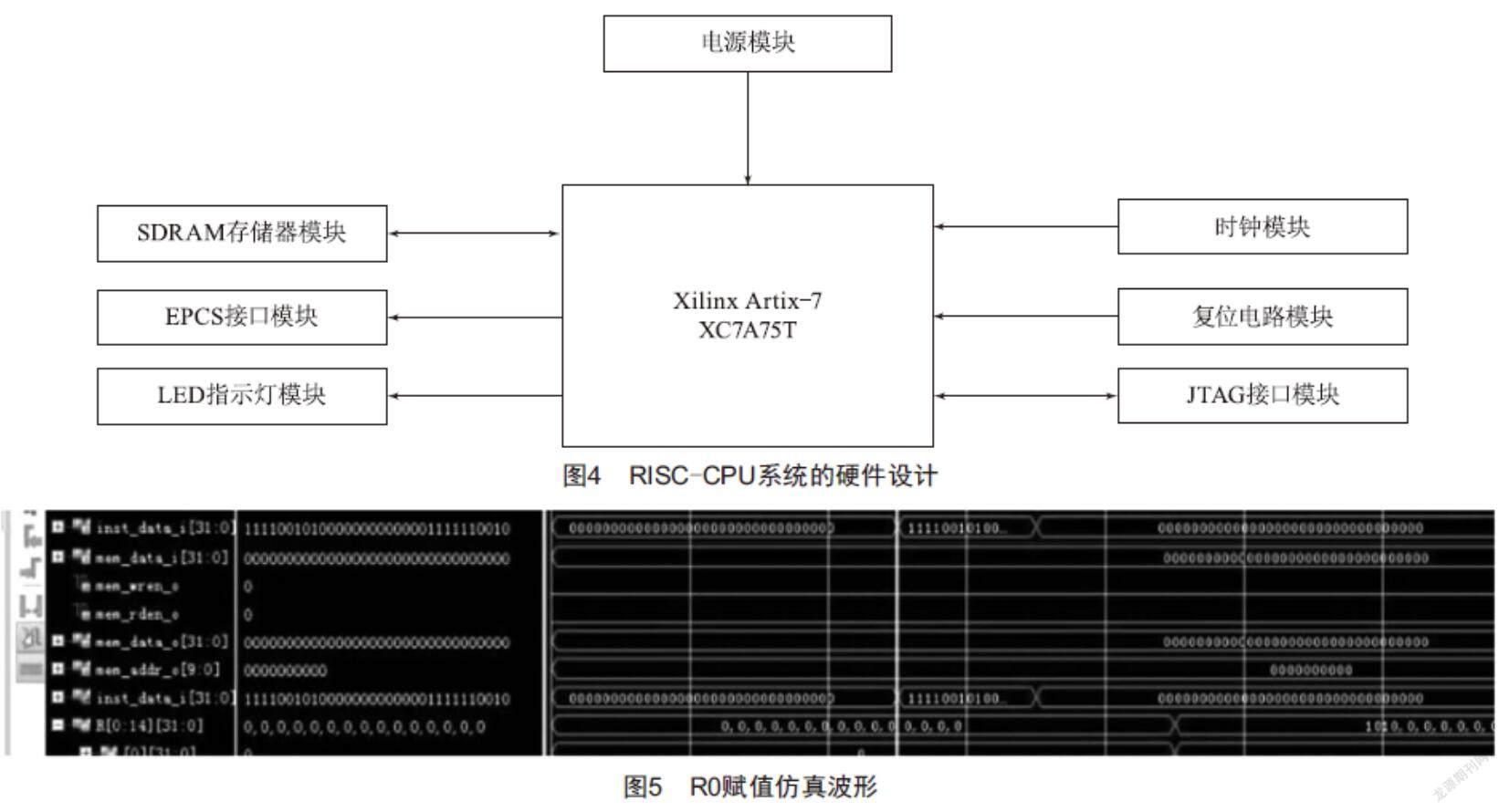

本设计中的FPGA芯片采用的是Xilinx公司开发的Artix-7芯片,型号为XC7A75T,該芯片逻辑单元丰富、数字运算处理能力强、集成度高。如图4所示,RISC-CPU的硬件系统以FPGA为控制核心,系统工作时,FPGA芯片负责协调、管理系统各个模块的工作任务,保证系统有序运行。SDRAM存储器模块是FPGA芯片的数据存储中心,其具有容量大、功耗低、读/写速度快的特点,在嵌入式系统的开发中应用广泛;系统的运行状态由LED指示灯模块显示;断电保护采用EPCS接口模块;JTAG接口模块用于FPGA的程序下载、仿真和调试。

3 RISC-CPU系统的仿真测试

采用VIVADO 2014.3对所设计的RISC-CPU系统进行仿真测试,由两部分组成,其中cpu_top.v模块为所设计的RISC-CPU,memoRy.v模块为存储模塊。

(1)R类型指令:图5和图6展示了为寄存器R0赋值立即数1 010和为寄存器R1赋值立即数1的过程。可以看出RISC-CPU读取到对应指令,经过一个时钟周期后,对应寄存器的值变为用户指定值。

图7和图8为寄存器之间数值的计算过程,图7为将R0和R1寄存器的值累加送给R2,图8为将R2寄存器的值和自身累加再送给R2(即R2的值翻倍)。从图7中可以发现读取到加法命令后,R2的值变为R0当前值(1 010)加上R1当前值(1)的结果,即1 011。从图8中可以发现读取到加法指令后,R2的值从1 011翻倍为2 022。

(2)I类型指令:图9和图10展示了寄存器和存储器之间交换数据的过程,图9展示了将R0寄存器的值(1 011)送到存储器地址4中,图10展示了将存储器地址4中的值读出送给R1,再将R0和R1的值累加送给R2的过程。

(3)J类型指令:图11和图12展示了利用J类型指令实现当R0=1时,给R2赋值2 021,否则赋值2 022的功能。图11中,R0为1,利用J类型指令跳过了第四条指令的执行,最终运行结果R2=2 021。图12中,R0为2,因此第四条指令照常运行,最终运行结果R2=2 022。

编译结果显示所设计的RISC-CPU层次合理,可以实现R类型、I类型和J类型指令的功能,CPU能正常运行,指令执行速度快。

4 结语

本文设计了一套基于FPGA的RISC微处理器控制系统,采用MIPS32指令集和5级流水线技术简化了硬件设计,整个系统运行速度快、性能高、可移植性强、稳定性好。并且在VIVADO软件上对设计的功能和关键模块进行仿真、调试、验证,以保证系统设计的合理性和正确性。

测试结果表明,设计的RISC微处理器功能正常,主频性能优良,能实现数据存储、指令执行、算术和逻辑运算、与存储器/外设交换数据等功能,满足设计要求。

[参考文献]

[1] 郝振和,焦继业,李雨倩.基于AHB总线的RISC-V微处理器设计与实现[J].计算机工程与应用,2020,56(20):52-58.

[2] 雷少波,黄民.16位嵌入式RISC微处理器设计[J].微型机与应用,2013,32(7):13-15.

[3] 刘览,郑步生,施慧彬.基于FPGA的32位RISC微处理器设计[J].数据采集与处理,2011,26(3):367-373.

[4] 黄旺华,李振坤,刘怡俊,等.基于FPGA流水线RISC微处理器的设计[J].微计算机信息,2008(14):187-189.

[5] 赵坤.基于RISC-V架构的SoC设计与实现[D].海口:海南大学,2021.

[6] 杨培森.第五代计算机的结构及其相关技术[J].系统工程与电子技术,1985(11):1-7.

[7] 严浦洲.基于Verilog HDL的多周期CPU设计与实现[J].数码世界,2020(12):31-32.

收稿日期:2022-02-23

作者简介:陈剑锋(1995—),男,福建泉州人,助教,研究方向:电路设计、信号处理、机械工程。