基于RISC-V 架构的中断实验设计

2022-03-22冯建文

冯建文

(杭州电子科技大学计算机学院,杭州 310018)

0 引 言

RISC-V架构以其开源特性和优越的性能,在全球范围内得到迅猛发展,也为国产处理器自主可控带来发展机遇[1-4]。相应地,国内外越来越多的高校基于RISC-V架构开展教学[5-6]。

中断和异常处理是现代CPU的必备功能,在实现I/O交互、软硬件故障处理、操作系统功能调用及并发机制等方面,有着不可替代的作用[7-8]。中断原理抽象,涉及指令集体系架构的底层,是计算机组成原理课程的难点之一。在课程前期实验中,学生已经完成了25 ~37 条RV32I 指令子集的多周期CPU 设计,但中断实验比较繁琐、复杂,尤其对于地方高校学生,实验难度较大。本文秉承“精简开放,重在方法”的设计理念,基于32 位多周期RISC-V架构,提出了一种精简的中断实验方案,引导学生使用FPGA工具,设计实现一个能处理单重可屏蔽外部中断的模型机,使学生理解中断原理、学会设计中断CPU。

1 RISC-V中断控制器设计

1.1 中断相关的CSR寄存器

RISC-V具有用户、监控和机器3 种工作模式,规范中要求必须实现拥有最高特权级的机器模式(M-mode)。RISC-V 设有4 096 个控制与状态寄存器CSR,其中6 个与机器模式下外部中断相关,图1 给出了它们的结构、部分字段含义,忽略了用户模式、监控模式以及其他中断类型[9]。

图1 RISC-V机器模式下外部中断相关的CSR寄存器

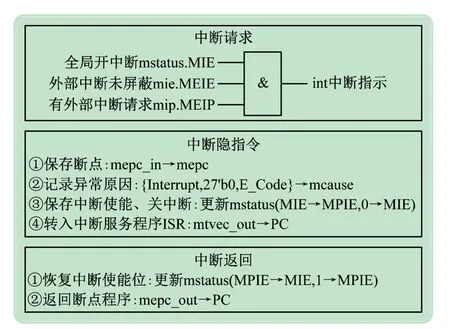

本实验处理的是机器模式外部中断,故Interrupt=1,编号为11;采用直接寻址方式转入中断服务程序ISR,故mtvec.MODE =0。

1.2 中断控制器

RISC-V标准通过平台级中断控制器PLIC完成对外部中断的判优及处理[10]。本实验只处理1 个外部中断源,设计的简单PLIC如图2 所示。

图2 CSR及中断控制器模块

(1)CSR 寄存器及读写控制。用于实现CSR 读写指令。实现了图1 的6 个CSR寄存器,csr_out始终读出地址为csr_A的CSR寄存器内容,记为CSR[csr_A];显然需要进行非完全地址译码。当csr_Write =1时,在csr_clk上跳沿执行对CSR[csr_A]的写操作,写入的数据是CSR[csr_A]和rs1_data 的运算结果csr_in。运算由独立的运算器完成,功能由csr_op 指定:=01,输出rs1_data;=10,进行或运算;=11,进行rs1_data & CSR[csr_A]运算。csr_op取自CSR指令funct3[1:0]。

(2)中断控制逻辑。用于中断请求、响应与返回。INTR是CPU外部中断请求输入引脚,上跳沿来临时,置位mip.MEIP。如图3 所示,此时如果开中断且未屏蔽,则输出int =1,送至控制单元CU处理。

图3 RISC-V中断过程的具体操作

本条指令执行完后,如果CU检测到int =1,则发送中断响应信号int_ack,执行图3 中的中断隐指令操作。针对本实验的外部中断:保存的断点mepc_in 是PC;且Interrupt =1,E_Code =11;转入ISR的方法是直接将mtvec内容置入PC。

CPU通过执行中断服务程序ISR来处理中断,ISR的最后一条指令一定是中断返回指令,RISC-V机器模式下就是mret指令。执行mret指令时,需要发送中断返回信号int_ret以返回断点,具体操作见图3。

外部中断处理后,通常是由软件(譬如读中断状态寄存器)来复位外部中断请求。图2 中,硬件上使用clr_MEIP信号清除mip.MEIP。那么由谁、何时发送clr_MEIP 信号呢?实验用存储器地址2000 0000H映射了一个自定义寄存器mipc[11],当软件写该地址时,clr_MEIP置1,从而复位MEIP。

6 个CSR寄存器要对其敏感的控制信号做出响应,下面给出mip寄存器的Verilog代码示例。

assign clr_MEIP =(F ==32’h2000_0000)&& Mem_Write;

always @(negedge rst_n or posedge csr_clk or posedge INTR or

posedge clr_MEIP) / /mip寄存器

begin

if(!rst_n) mip <=32'h0;

else if(INTR) mip[11]<=1′b1;/ /MEIP =1

else if(clr_MEIP) mip[11]<=1′b0;/ /MEIP =0

else if(csr_Write &&(csr_A ==12′h344)) / /写mip

mip <=csr_in; / /csr_in =CSR[csr_A]csr_op rs1_data

end

2 模型机设计实现

2.1 目标指令集

目标指令集包含RV32I 基础指令和中断相关指令。前期的CPU 实验,学生已经实现了至少25 条RV32I指令子集,允许学生在此基础上修改添加,也可以选取表1 所示的8 条典型RV32I指令[12],或者以目标导向的方式来选择最小化指令集——以能执行“中断功能测试程序”为设计目标。

表1 RV32I目标指令子集

表2 给出了新增的2 条中断指令和3 条CSR 指令[9],均为I型格式。CSR 指令同时完成一对原子操作:rs1 与CSR运算后写入CSR、CSR内容写入rd。

表2 中断指令与CSR寄存器访问指令

2.2 模型机的系统结构和数据通路

基于目标指令集,设计出多周期RISC-V 中断模型机的系统结构,如图4 所示。

存储器采用哈佛结构,指令执行包含经典的五阶段[13-14]:取指令IF、译码-读寄存器ID、执行EX、访存MEM和写回WB。每个阶段都包含了相应的功能部件以及保存操作结果的暂存器/寄存器,例如IR、A/B/F暂存器、MDR寄存器。

初级译码器ID1 解析指令字段、产生32 位立即数imm32。译码及控制单元CU则进行二次译码,产生全机的控制信号,包括中断控制信号。

分析指令在图4 上的数据通路,可以画出指令执行流程图,如图5 所示,虚线框表示与中断相关。每条指令的指令周期结束后,都会转移到公共的中断查询周期,询问“int =1?”,如果为1,则转入中断响应周期,执行中断隐指令。

图4 多周期RISC-V中断模型机系统结构

图5 指令执行流程

2.3 CU部件设计

控制单元CU是CPU控制中心,有序发送当前指令所需的控制信号,它的设计是CPU 设计的关键步骤。CU可采用硬布线或有限状态机FSM 来实现,由学生自主选择。FSM实现CU的设计步骤如下[15]:

(1)将图5 中相同的方框合并,构造出状态转移图,如图6 所示,依据指令操作码执行状态转移。

图6 指令执行的状态转移图

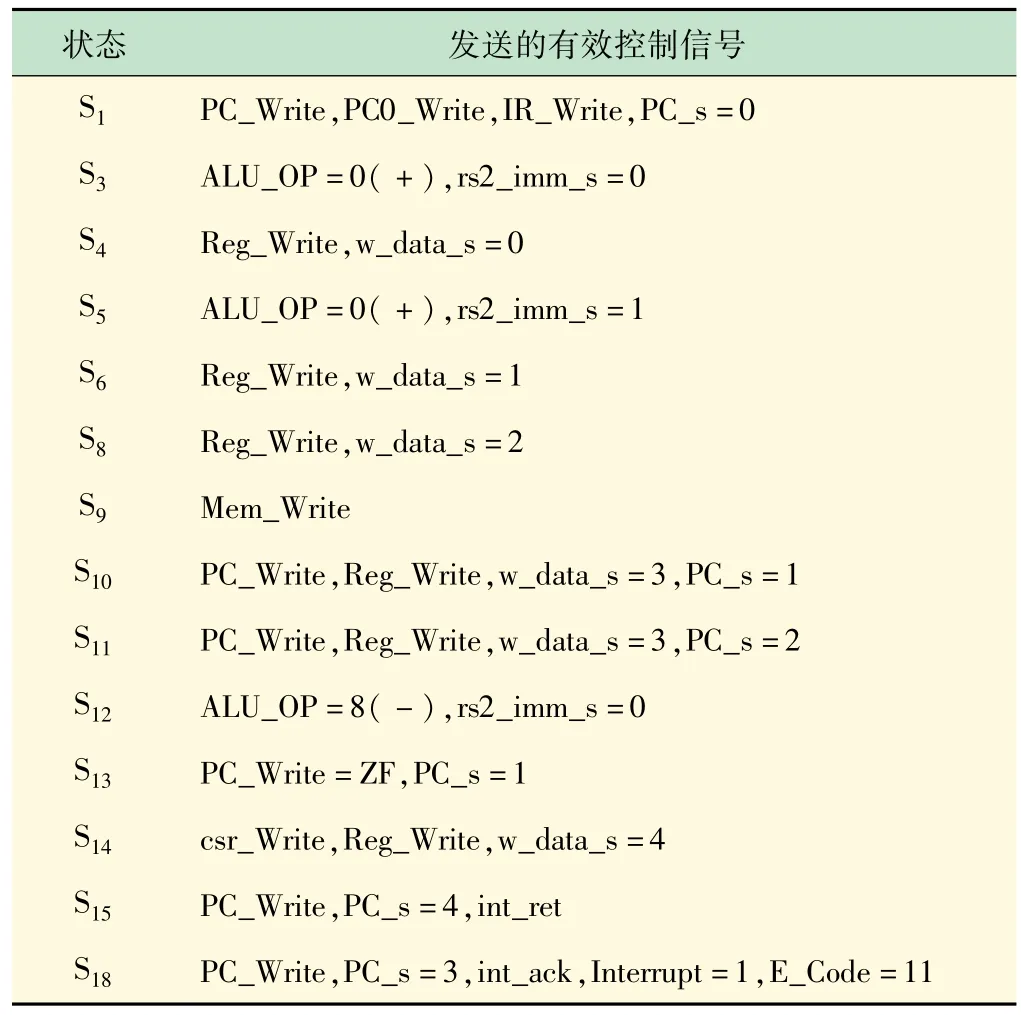

(2)写出每个状态下发送的控制信号,如表3 所示。中断相关的状态是S14~S18;表格中未出现的状态不发送有效控制信号,仅由clk 控制操作。例如S16和S17状态,仅根据int信号确定下一状态。

表3 各状态下指令发送的控制信号

(3)采用FPGA两段式或三段式有限状态机描述状态转移图,并发送控制信号。

设计完成CU 后,将它和其他部件连接起来就构成了RISC-V的模型计算机。

3 测试与验证

3.1 中断测试程序

为测试外部中断,将CPU 的INTR 接到一个按键上,每按下一次,就产生一次中断。假设CPU 对外部中断的处理是将x6 寄存器内容减1,为0 时结束主程序,测试程序如下:

main: #主程序,地址00H

addi x5,x0,0x20 #取ISR_DEC入口地址0x20→x5

csrrw x0,mtvec,x5 #装中断向量(x5)到mtvec

addi x6,x0,3 #中断次数3→x6,3次结束主程序

L: wfi #等待外部中断

beq x6,x0,exit # x6 =0结束主程序,否则顺序执行

j L #x6≠0,则跳转L,继续等待中断

exit:wfi #相当于空指令/占位符

wfi #相当于空指令/占位符

ISR_DEC: #中断服务子程序,地址20H

lui x7,0x20000 #x7 =0x2000_0000

sw x0,0(x7) #写0x2000_0000产生clr_MEIP

addi x6,x6,-1 #中断处理操作,x6-1

mret #中断返回

3.2 实验验证

将测试程序翻译成机器语言程序,装入指令存储器IM,即可设计验证方案,重点验证wfi 指令、mret 指令和中断隐指令,能否正确转移。图7(a)给出了wfi指令(编码10500073H)发生外部中断时的仿真波形图,状态机当前状态ST 从S16(0x10)转移到S17(0x11),再转入S18(0x12)进行中断响应,图7(a)黄线显示PC 被修改为ISR_DEC 的入口地址20H。图7(b)是相应的板级验证,左边5 位LED灯是ST状态。当ST =10000b(S16)时,按clk 键状态保持不变,但是按一次INTR键后再按clk键,状态会变成10001b(S17),进而变成10010b(S18),正确响应了中断。3 次中断后,主程序停在exit 处。验证结果表明中断实验的CPU运行正确。

图7 实验验证

3.3 思考与探索

基本要求之外,实验设置了丰富的思考与探索题,要求学生至少回答或实践两个。例如:能否在执行mret指令时清除mip.MEIP?能否合并状态S16和S17?能否取消S17状态,以使所有指令周期缩短1 个clk?CSR指令的运算操作能否用主ALU 实现?如何修改设计,以支持中断嵌套?如果要实现支持8 个硬件中断源的PLIC呢?如果外部中断请求的操作是从开关读入一个数据存入主存,如何修改设计方案?

思考与探索环节促进学生养成勤于分析思考、善于推导求证、敢于探索实践的习惯,学生逐渐由被动到主动,很大程度上激发了学生硬件学习实践的兴趣。

4 结 语

中断是CPU处理突发事件、实现操作系统核心功能的重要手段。基于FPGA 实验平台,本文设计了一个功能精简、原理深入的中断实验,通过实现32 位RISC-V多周期中断CPU,达成了“理解中断原理、学会简单的中断CPU设计实现”的教学目标。在指令集选择、指令流程设计、CU 实现、测试程序及实验验证等各环节,均设置多元开放的实验要求,让学生自主选择、组织与架构,实现自己的中断CPU。实验设计注重学思结合、知行统一,锻炼了学生的分析研究与系统设计的能力,在教学实践中,取得了良好的教学效果。