基于ARM处理器的空间可靠性软件架构设计与实现

2022-03-19宋桃桃杜长刚薛治纲李园利

宋桃桃,杜长刚,邱 翔,薛治纲,李园利

(中国空间技术研究院西安分院,西安710000)

0 引言

随着小卫星技术的发展与成熟,小卫星在航天应用上正在向全方位扩展,使用CPU处理器实现复杂逻辑与控制功能越来越必要[1]。但是传统的宇航级处理器价格昂贵且体积大,不适用于体积小、质量轻、成本低的小卫星系统。恶劣的空间环境对处理器的选择也提出了严格的要求。体积小、功耗低、价格低、性能高、可靠性高的处理器是小卫星星载控制设备的理想选择。TMS570LS3X是一款针对安全领域应用的高性能微处理器。体积小、价格低、低功耗及高性能等特点[2]使其在小型化、产品化的小卫星星载设备上具有一定应用前景。选取具有低轨飞行经历的TI公司高性能微控制器TMS570LS3X,但是由于其等级为工业级芯片,在空间环境中可靠性无法保障,且现有文献中并未提出对该类处理器的有效加固措施。因此提出一种通过采用软件设计提升处理器可靠性的方法,并在硬件平台上进行了验证。

1 TMS570LS3X应用分析

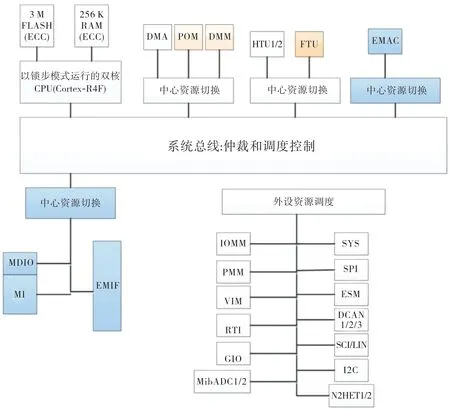

TMS570LS3X是针对安全领域应用的高性能汽车级微处理器,上电自检、以锁步模式运行的双核处理器及内嵌ECC(error correction code)功能都为其使用中的安全性提供了保障。高达180 MHz的工作时钟可满足较复杂逻辑控制功能的性能要求, 3 MB片内程序闪存和256 KB片内RAM及高达128 MB的SDRAM空间和3个16 MB的EMIF外部存储空间可满足星上处理软件存储及运行要求。TMS570LS3X器件集成了ARMCortex-R4F浮点CPU,可提供高效的1.66 DMIPS/MHz。当以180 MHz时钟运行时可提供高达298 DMIPS的运算能力。处理器功能框图如图1所示[2-3]。

图1 功能框图Fig.1 Functional block diagram

处理器上电后PC指针指向0x00000000片内FLASH地址空间,因此可执行文件须放在此地址段[4]。但是该FLASH没有抗辐射指标,在复杂的空间环境下可能造成FLASH中程序文件的损坏,导致软件功能无法正常运行,继而影响系统任务执行[5-6]。星载软件可靠性至关重要,因此通过软件架构设计确保空间飞行状态下,片内FLASH中可执行文件的正确加载及运行,是文章要研究及解决的问题。

2 软件架构设计

2.1 存储器地址空间映射

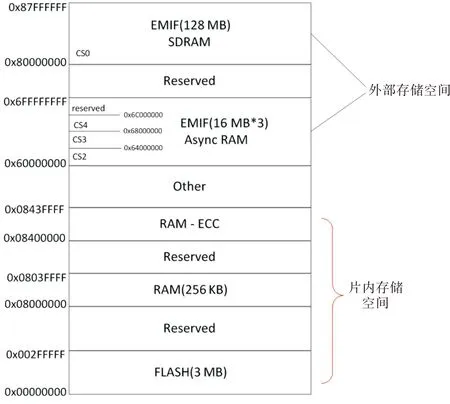

Cortex-R4F CPU 使用32 bit地址总线可寻址4 GB的存储空间,该空间被划分为多个不同区域。主要存储空间分配如图2所示,片内有3 MB FLASH程序存储空间和256 KB RAM数据存储空间,均支持纠1检2的ECC校验,每64 bit数据对应8 bit的校验数据。外部存储器接口EMIF支持4个片选信号,可以外挂3个16 MB大小的异步存储器和1个128 MB的SDRAM,支持8位或16位宽的数据总线[3]。

图2 主要存储空间地址映射Fig.2 The main memory map

2.2 可靠性架构设计

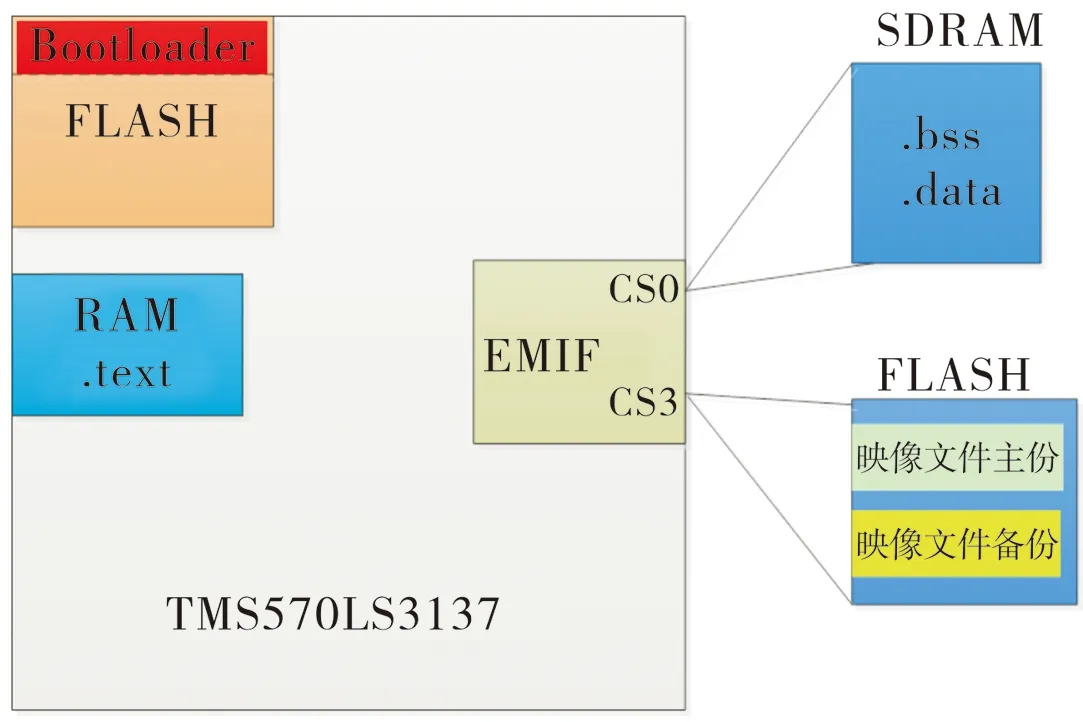

通常,基于TMS570LS3X开发的程序将映像文件.text段存储并运行于片内FLASH,而数据段运行于片内RAM[7-8]。但考虑到单粒子及其他空间辐射的影响,存储在片内FLASH中的映像文件有可能会被损坏,映像文件越大被损坏的可能性就越高[9-10],所以考虑在外部存储空间上挂接可靠性高的高等级FLASH芯片,且将应用程序映像文件以主备份冗余形式存储于片外FLASH中,片内FLASH仅存储精简的Bootloader程序,实现硬件基本初始化、可执行程序加载及PC指针跳转,降低片内FLASH中文件损坏的风险,提高软件的可靠性。高等级FLASH发生位错误的概率很低,因此仅对应用程序映像文件采用主备份方式。软件设计如图3所示。

图3 软件架构设计Fig.3 Software structure design

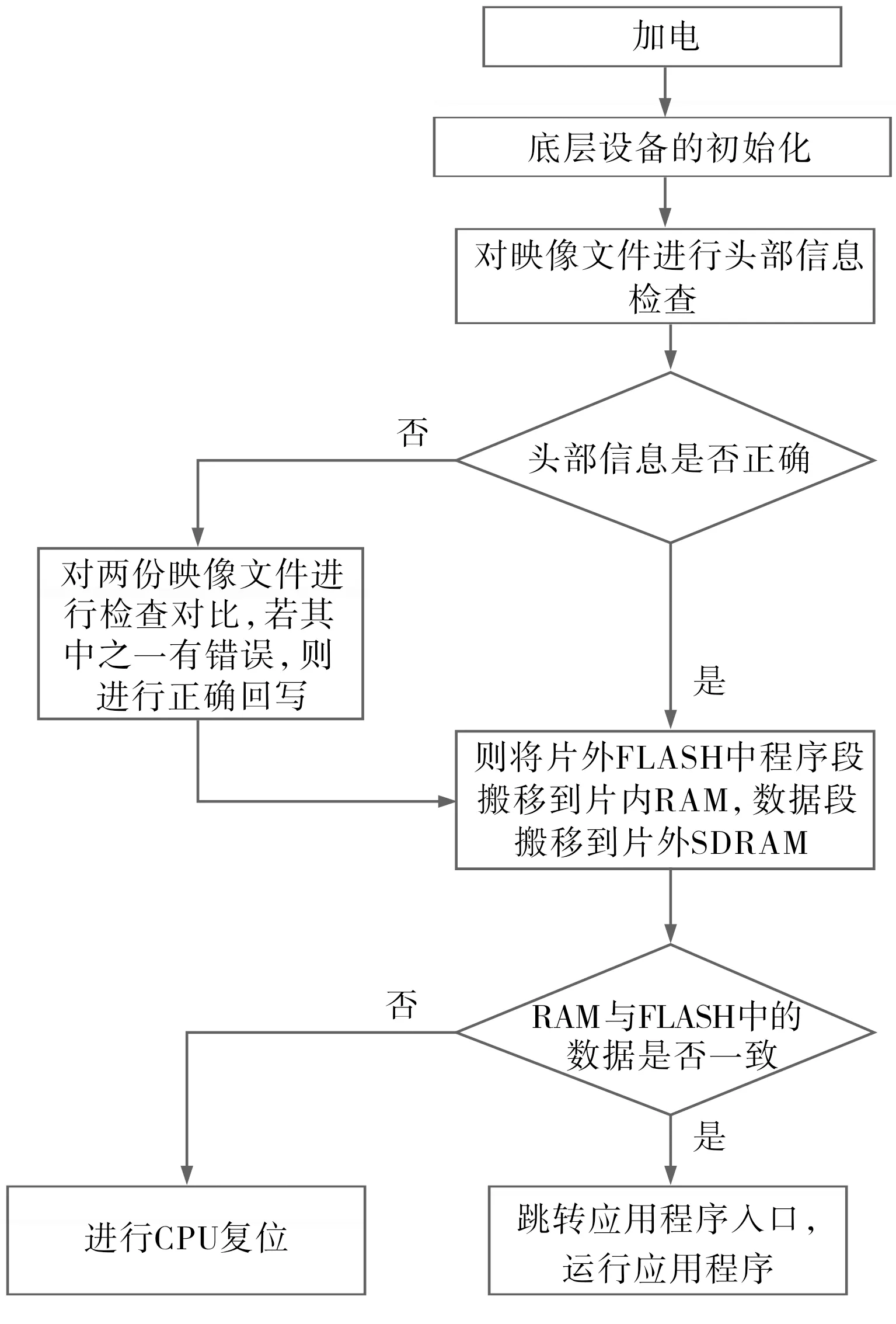

Bootloader首先实现基本的硬件初始化,包括中断向量表、内部寄存器、堆栈空间、时钟、管脚映射及外部存储器SDRAM和FLASH初始化等[4,11];然后从片外FLASH读取并加载映像文件,当主份数据读出时若CRC校验发生错误,则利用备份数据完成加载,并对主份数据进行正确数据的回写。Bootloader将映像文件的.text搬移到片内RAM,数据段搬移到片外SDRAM,以提高代码的执行速度和可靠性。映像文件在烧写到片外FLASH前需进行一定处理,增加文件头校验及区段长度等信息。Bootloader实现框图如图4所示。

图4 Bootloader实现框图Fig.4 Bootloader implementation block diagram

另一方面通过寄存器设置,将片内FLASH及片内RAM的ECC功能置为“使能”状态,当软件在轨发生单比特错误时ECC可自动纠正数据,保证总线上数据的正确性,亦可在一定程度上降低单粒子翻转造成软件异常的风险,所以在底层硬件初始化时应打开ECC校验。

3 实现及验证

3.1 Bootloader实现

本小节对Bootloader中关键的程序模块进行说明。

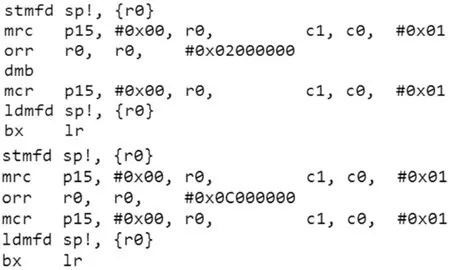

3.1.1 ECC功能初始化

在_c_init00函数中加入以下语句将片内FLASH和RAM的ECC校验功能设置为“使能”状态[12]。

3.1.2时钟配置

TMS570LS3X处理器有7个可供选择的时钟源,文中选用PLL1作为系统时钟源,先清零CSDIS寄存器的相应比特位使能PLL1,然后设置寄存器PLLCTL1、PLLCTL2实现倍频功能,倍频后系统工作钟最高可达180 MHz。PLL1输出时钟与OSCIN时钟的计算关系如式(1)所示:

(1)

为了检查PLL1输出是否与程序中设置的一致,可通过ECLK管脚测量系统的实际工作时钟。在时钟初始化代码中,将寄存器SYSPC1的ECPCLKFUN位置1,选通ECLK的时钟输出功能;其次清零ECPCNTL寄存器的ECPSSEL位选择ECLK的时钟源为VCLK(0为VCLK,1为OSCIN),最后通过配置ECPDIV位确定ECLK管脚上的时钟频率(ECLK管脚输出频率最大不能超过20 M),ECLK时钟频率与VCLK时钟的关系如式(2)所示[2]。

(2)

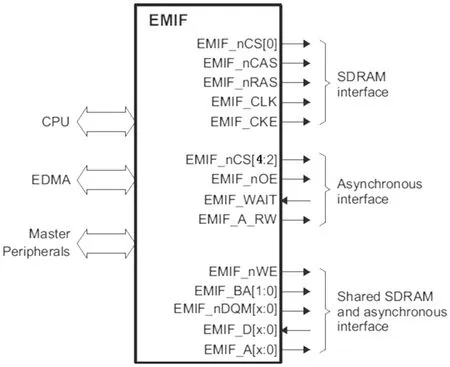

3.1.3 EMIF接口初始化

EMIF存储控制器接口数据线为16位位宽,兼容JESD21-C SDR SDRAM。通过该接口CPU可连接多种外部存储器,如同步SDRAM,异步设备NOR FLASH、SRAM等。EMIF接口共有4个外部片选信号:CS0支持16位宽的SDRAM,CS2~CS4支持16位NOR FLASH 、SRAM等异步存储器。原理框图如图5所示。

图5 EMIF接口原理框图Fig.5 EMIF functional block diagram

EMIF接口的初始化包括接口时钟、复用管脚、接口时序及数据总线位宽。VCLK3为EMIF接口提供时钟,通过CLK2CNTRL的VCLK3R位配置VCLK3的时钟频率。对复用的I/O管脚进行寄存器配置,使其功能为EMIF地址线或数据线。结合所选外部存储器芯片手册配置CEnCFG(n= 2,3,4)寄存器,使读写时序及数据位宽与外部存储器一致。

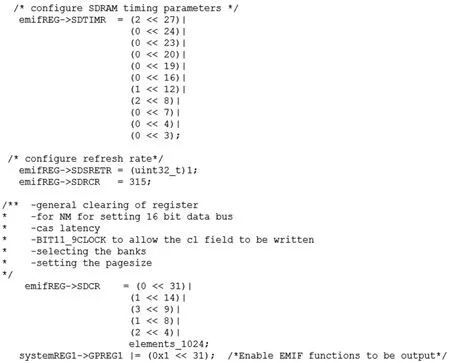

下文给出所选用SDRAM的初始化配置,包括刷新模式、bank数量、页大小、CAS等待时间、刷新速率、时序等,此处VCLK3初始化为40 MHz。

3.1.4 映像文件加载

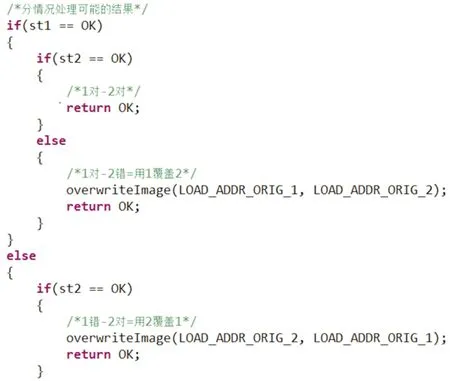

读取主份映像文件头部CRC字段,与当前计算的CRC值进行比较;对备份映像文件进行同样操作。如果两份文件中有一个出现错误则用正确文件进行回写,否则直接将主份映像文件的代码段和数据段加载到指定的空间。

3.2 集成开发环境配置

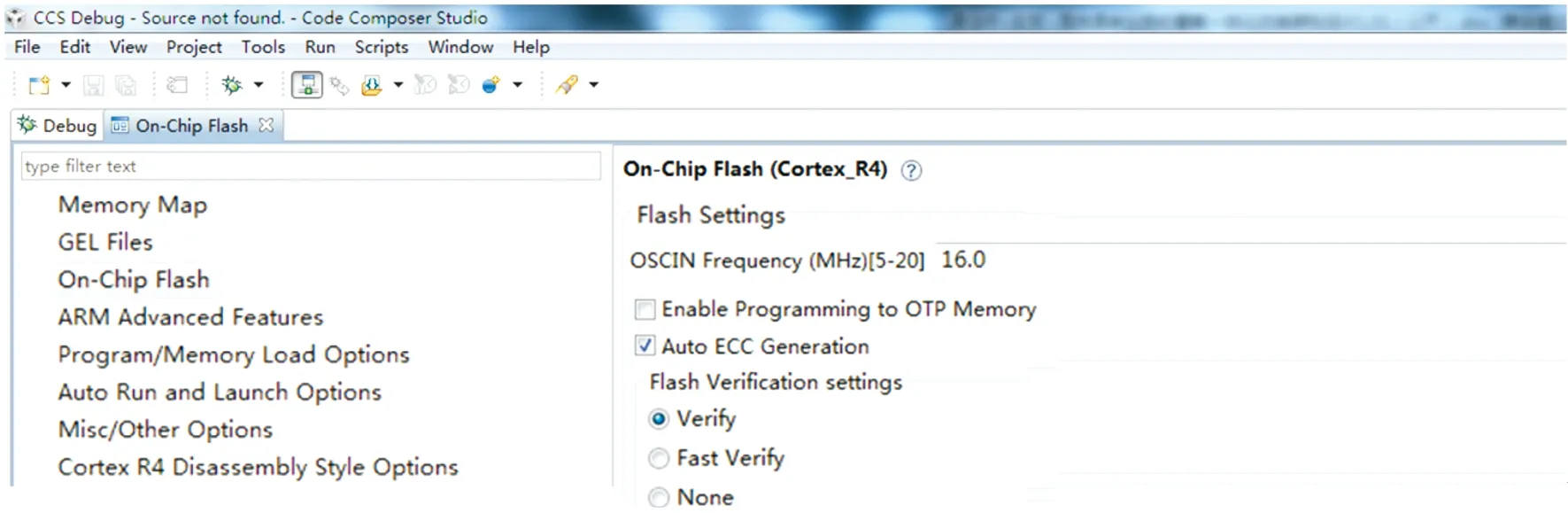

本文使用CCS5.5集成开发环境。在Bootloader中使能片内FLASH ECC功能后,需要同时配置调试环境以实现Bootloader的正确运行,如图6所示。

图6 CCS5.5调试界面下使能 FLASH ECCFig.6 Enable FLASH ECC over CCS5.5 debug condition

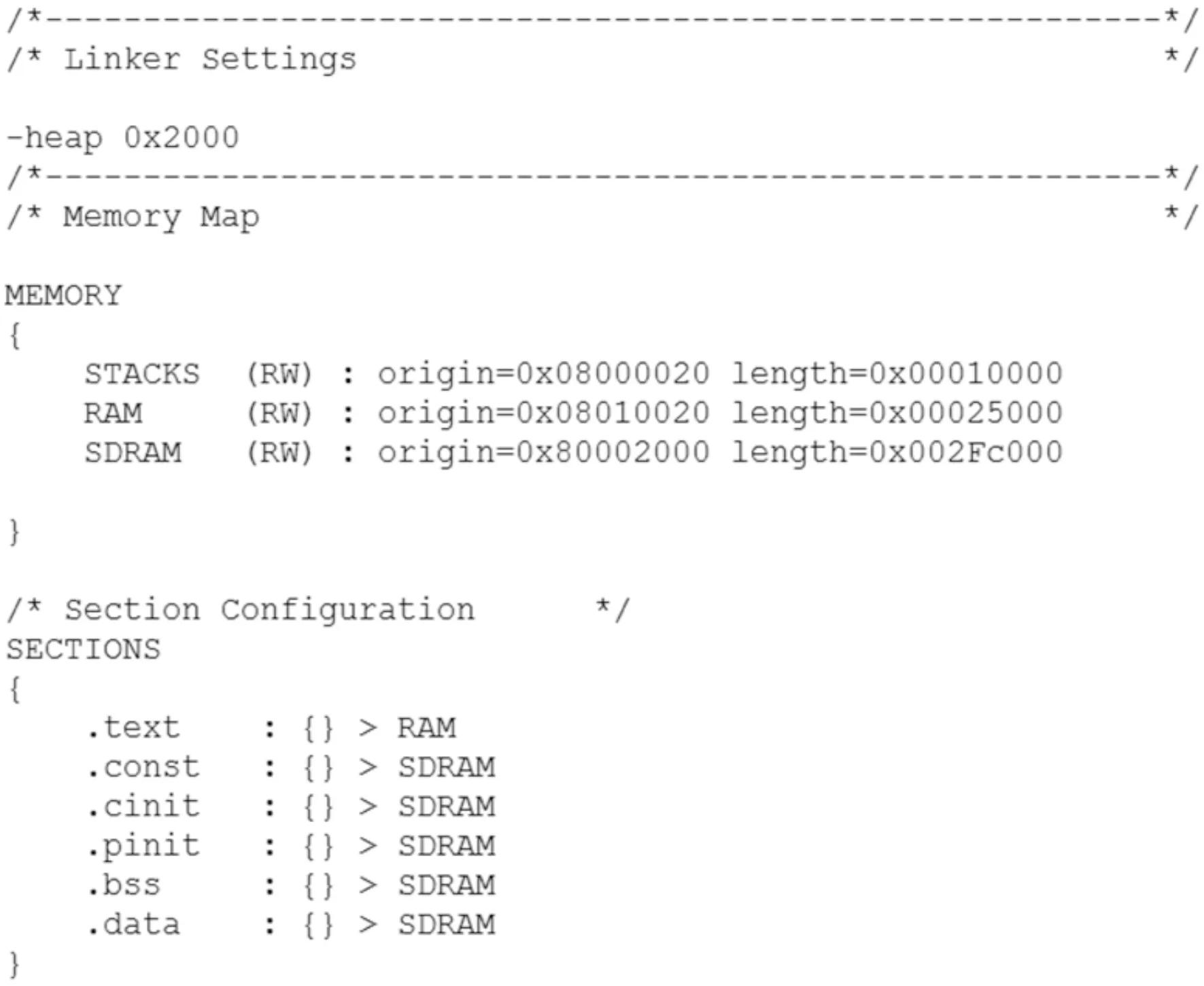

对应用程序使用CCS5.5集成开发环境,通过修改cmd文件,将应用程序的数据段链接到片内RAM,而数据段放到片外SDRAM。具体cmd文件的设置如下所示:

3.3 硬件平台验证

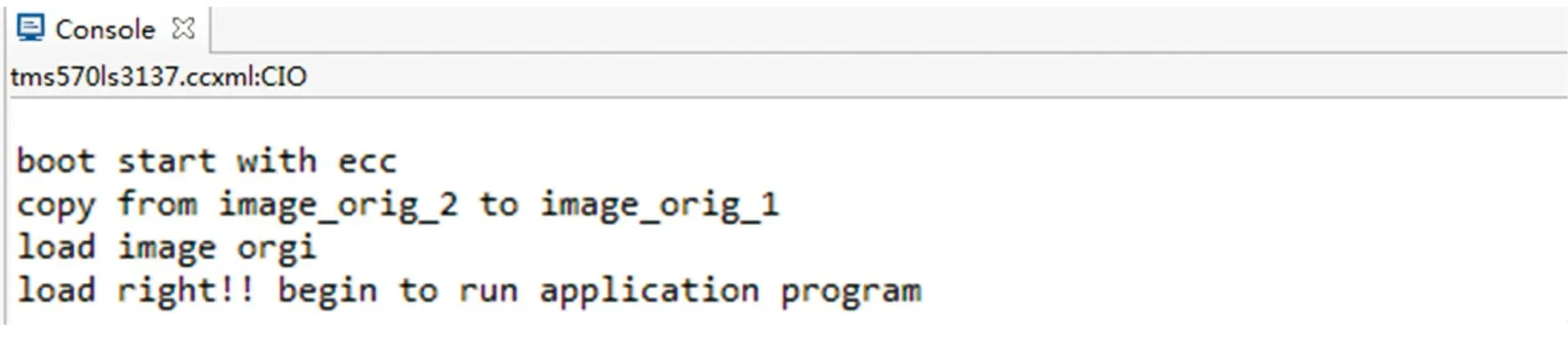

在硬件平台上通过CCS5.5集成开发环境将Bootloader烧写到片内FLASH,然后将处理过的应用程序映像文件烧写到片外FLASH存储空间。分3种情况对Bootloader功能进行验证。

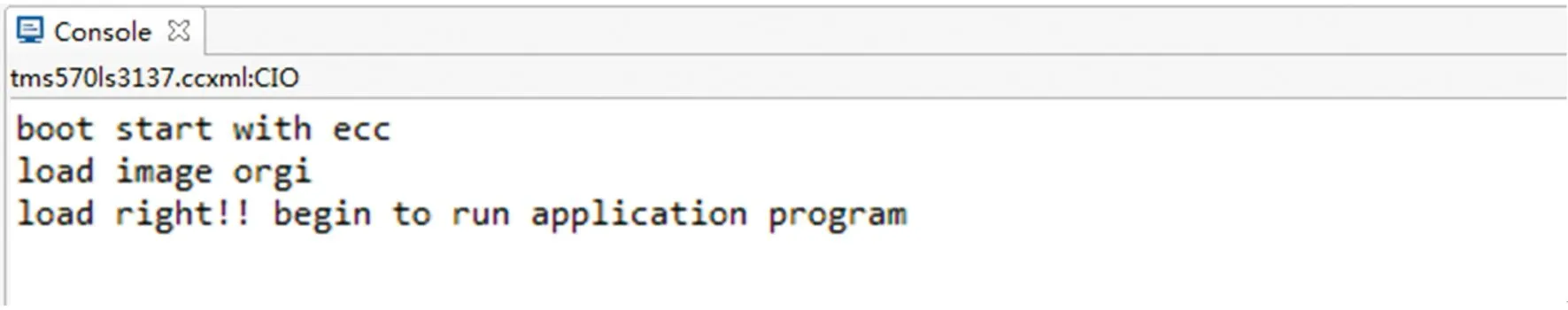

3.3.1 两份映像文件均正确

片外FLASH两份映像文件均烧写正确内容时,Bootloader会直接将主份映像文件搬移到RAM及SDRAM。测试结果如下:

3.3.2 主份映像文件正确,备份映像文件错误

将备份映像文件人为烧错1 bit,模拟在轨故障[11]。Bootloader加载前会用主份文件修复备份文件,然后进行程序搬移及加载。测试中分别选择检验头出错、text段出错或data段,且每项出错均进行5次以上测试验证,测试结果一致均可以正常加载:

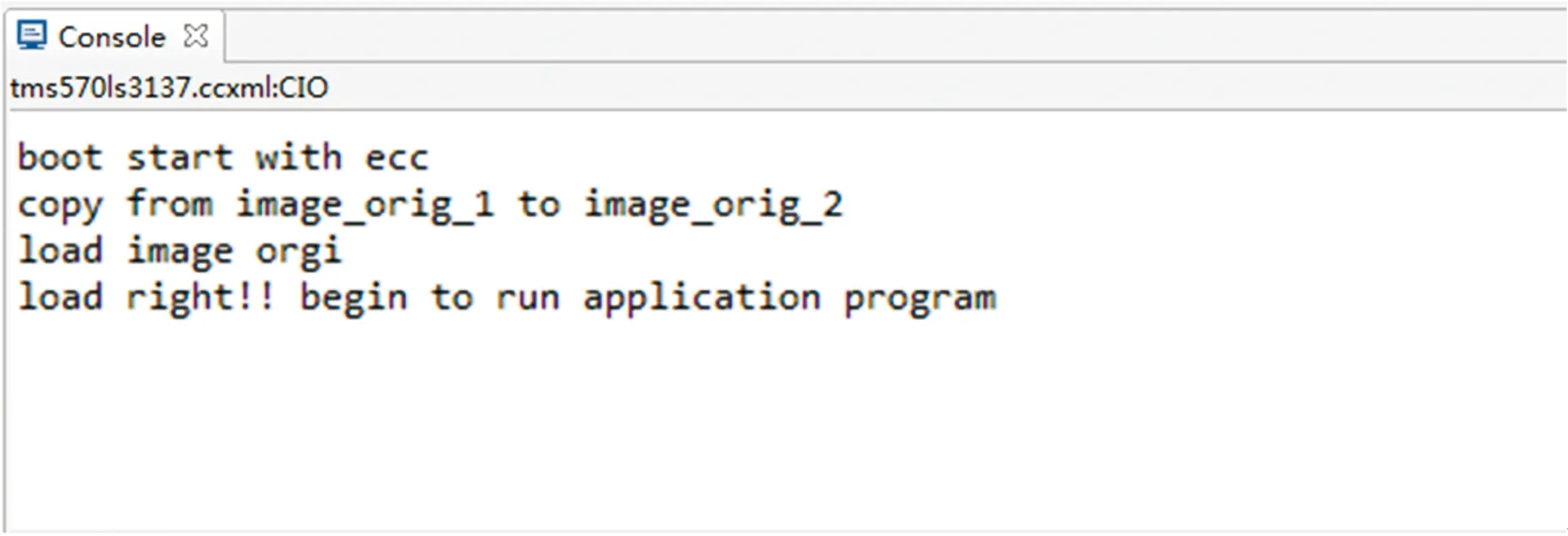

3.3.3 主份映像文件错误,备份映像文件正确

将主份映像文件人为烧错2 bit,模拟在轨故障。Bootloader加载前会用备份文件修复主份文件,然后进行程序搬移。2 bit出错位置选取原则为:1)文件首部校验区2 bit连续错误;2)文件text段2 bit连续错误;3)文件data段2 bit连续错误;4)文件任意位置非连续2 bit错误。按以上4条原则分别设置出错bit文件,每项用例进行5次以上测试。测试结果均可以纠正错误并正常加载,如下所示:

4 结论

小卫星低成本、短周期和高性能的特点使得体积小、成本低、集成度高、性能高、功耗低的工业级元器件得到了越来越多的青睐。但此类元器件质量等级低,抗空间环境性能差,直接代替高等级元器件应用于航天器工程中存在一定的风险。在对TMS570LS3X处理器功能及架构分析的基础上,针对其在空间环境应用中存在的风险点进行了分析研究,提出了使用软硬结合提高处理器可靠性的方法。通过对软件架构的设计分析和工程实现后,在设计的硬件平台上进行了充分测试验证,测试结果表明该方法可有效提升处理器抗单粒子能力,大大降低系统故障概率,为高性能工业级元器件在宇航应用中的可靠性加固提供了参考和借鉴。