一种数据链通信偶发故障剖析

2022-01-06杨廷静

杨廷静

(中国电子科技集团公司第十研究所,四川 成都 610036)

0 引言

数据链是连接整个战区内数字化战场上指挥中枢、作战节点和武器平台的信息处理、交换和分发系统,当数据链出现通信故障时,将导致整个数据通信网不畅通甚至中断。由于数据链通信故障涉及设备多、链路相关性大,因此排故复杂度较高。

本文针对某综合处理设备数据链通信时出现偶发异常,通信功能不稳定的故障,逐层分析以剖析根本原因,并提出了解决措施。

1 工作原理

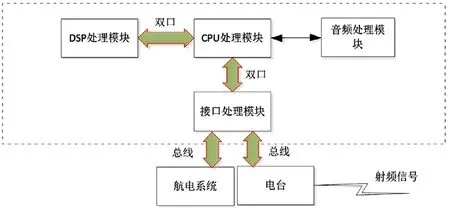

某数据链通信原理框图如图1所示,其数据消息接收处理流程为:电台将接收到数据链消息转发给接口模块,经接口模块协议转换、CPU模块处理后传给DSP,并由其对接收到的数据进行数据校验以完成信息处理。若校验成功,则认为该消息合法,然后将信息解析结果经CPU实现控制并返回系统;若校验失败,则丢弃该消息。

图1 通信原理框图

在系统使用过程中,偶尔会出现读取消息失败,显示接收数据CRC校验错误的故障现象。通过在软件中插庄代码,对发往DSP的双口数据进行CRC校验,确认该故障发生在CPU模块访问DSP模块双口存储器的时候,此访问过程的硬件组成与原理如图2所示。

由图2可知,DSP模块双口存储器的地址线为单向输入信号,由CPU模块处理器产生,经驱动器后输出到DSP模块。而数据线为双向输入输出信号:在CPU模块写DSP双口时,由CPU模块处理器驱动后输出到DSP;在CPU模块读DSP双口时,由DSP双口驱动后输出到CPU模块。

图2 CPU模块访问DSP双口存储器的原理图

2 故障剖析与解决措施

2.1 DSP双口写入数据错误

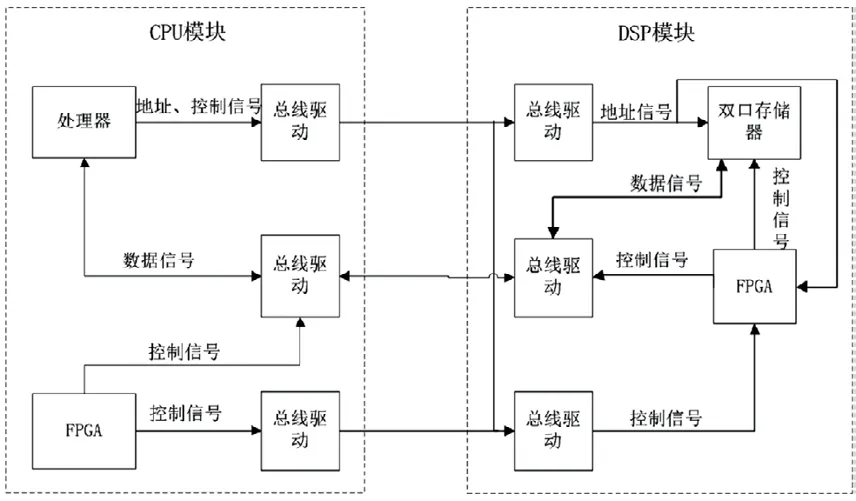

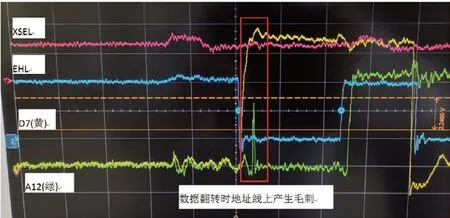

当发生故障时,用示波器测量CPU模块访问DSP双口的相关片选、读写信号,发现CPU模块写DSP双口地址时,DSP内部地址线A12上有高电平毛刺产生,波形如图3所示。图中,从上到下信号依次为LBE总线片选信号/CS、写信号WR、DSP内部地址线A12。

图3 故障时DSP内部地址线A12信号测量

当DSP双口存储器拟写入地址为0x17FF时,A12应为低电平,但系统在实际运行中由于地址线A12上产生了高电平毛刺,此时所形成的地址则变为了0x1FFF。采用CPU对0x1FFF地址进行数据读取,读取结果与CPU拟写入地址0x17FF的数据相同,由此可判定DSP双口存储器地址总线上产生的高电平毛刺导致了数据的写入错误。为了查明毛刺的来源,继续采用示波器对相关信号进行测量,发现当毛刺产生时,LBE总线上有多条数据线将发生跳变,测量波形如图4所示。图4中,从上到下信号依次为LBE总线XSEL信号、CPU模块上数据线驱动器的使能信号EHL、LBE数据总线D7和DSP地址线A12。

图4 毛刺产生时LBE总线数据信号测量

经反复测量发现,DSP双口存储器地址总线上毛刺产生时刻均为LBE总线数据信号跳变时刻,并且发现若LBE总线上的数据线同时发生翻转的信号较少(小于8个)时,DSP双口存储器地址总线将不会产生毛刺。由此可判断,在DSP双口存储器的写周期,其地址总线上产生的毛刺与LBE总线上的多条数据线同时发生翻转时所产生的同步开关噪声有关。

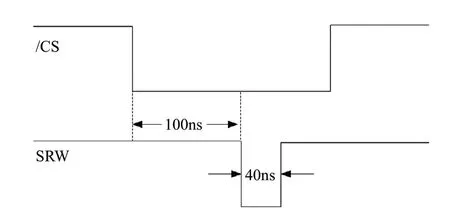

为了避免在写周期中,数据翻转时在地址总线上所产生的毛刺引起的写入错误,于是对DSP模块中FPGA输出的写信号时序进行了优化,对其输出时间进行延后并减小其有效输出时间,优化后的写信号波形如图5所示。图5中,从上到下信号依次为LBE总线片选信号/CS、DSP双口存储器写信号SRW。

图5 修改后DSP双口写信号时序

此时,DSP双口存储器写信号在片选有效之后约100 ns变为有效,而毛刺出现在片选信号有效之后约20 ns,因此其不会对写周期产生影响。同时,写信号有效时间为约40 ns,大于双口存储器芯片写入脉冲的最小宽度15 ns,保证了数据的可靠据写入。

2.2 DSP双口读取数据错误

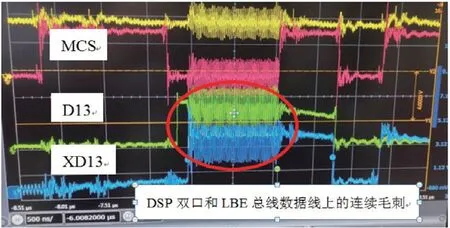

当DSP模块中FPGA的写时序逻辑完成优化后,采用CPU模块对DSP中的双口存储器进行访问验证,则会出现偶发性的数据读取错误。此时,采用示波器测量LBE总线数据信号、DSP双口存储器数据信号均有连续毛刺产生,其波形如图6所示。图中,从上到下信号依次为DSP双口存储器片选信号MCS、数据线D13和LBE总线数据XD13信号。

图6 故障时DSP双口数据线和LBE总线数据线测量

在读周期中,LBE总线数据信号由DSP双口存储器数据信号驱动,通常不会有连续毛刺产生。由测量结果判断,LBE总线数据线上的毛刺信号应由DSP双口存储器数据线上的毛刺所引起,从而导致了数据的读出错误。进而对LBE总线数据驱动器的使能信号测试,发现DSP双口存储器数据线上的毛刺产生在LBE总线数据驱动器使能信号有效时,由此可判断DSP双口存储器数据线上的毛刺由多个LBE总线数据信号的同时跳变引起。经反复测量发现,若同时发生翻转的总线数据信号较少(小于8个)时,DSP双口存储器数据线上将不再产生毛刺。当DSP双口存储器数据线上产生毛刺时,其地址总线信号也将产生连续毛刺,且两者在时间上是同步的。由此推断,读周期中DSP双口存储数据线上的连续毛刺与其地址线上的连续毛刺有关,而地址线上的连续毛刺与多个LBE总线数据同时发生翻转时产生的同步开关噪声有关。

由于读周期中的LBE数据总线由

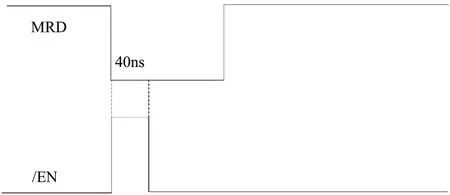

DSP模块驱动,其数据信号在DSP双口存储器读出数据有效时发生跳变,而DSP双口存储器芯片从读信号有效到数据输出之间的间隔不大于10 ns,因此DSP双口存储器芯片数据信号和LBE总线数据信号发生翻转的时刻在读信号有效后10 ns左右,若将此段时间的LBE总线地址驱动器使能信号/EN设为无效,可有效避免LBE总线数据信号翻转对DSP双口存储器地址信号的影响。于是,在DSP模块FPGA的时序中,将LBE总线地址驱动器使能信号/EN在双口存储器读信号MRD有效时保持1个时钟周期(如40ns)的无效状态后变为有效值,如图7所示,以保证数据的有效输出。

图7 修改后LBE总线地址驱动器使能信号

综合以上分析,当CPU模块访问DSP双口存储器时,若多个LBE总线数据同时发生翻转时,其产生的同步开关噪声会引起DSP双口存储地址信号产生毛刺,该毛刺在读写周期中均会造成数据访问错误。其根本原因在于,多个LBE总线数据信号同时发生翻转时产生的同步开关噪声使其地址线上产生有效幅值较小的毛刺,但该毛刺经连接器、母板和PCB走线传输至DSP模块地址驱动器后,毛刺幅值被放大。此时,毛刺的最大幅值达到了1 V,超出了驱动器低电平门槛电压(0.8 V),被识别为高电平,最终导致地址错误。通过对DSP模块中FPGA总线驱动器使能与双口存储器写信号在时序上的优化,然后对系统进行了反复测试,均不再发生数据的读写错误,有效解决了上述的偶发性故障问题。

3 结束语

CPU模块访问DSP双口存储器时,多数据总线同时跳变产生的同步开关噪声使得DSP双口存储器地址线上产生了高电平毛刺,进而导致数据改写和读出错误故障。通过优化DSP双口存储器写信号及DSP模块中LBE总线地址驱动器使能信号的时序逻辑,有效地解决故障。数据链通信系统具有规模大、综合化和复杂度高的特征,当发生故障时可能导致系统整体失效,因其涉及元素多,故障诊断和修复时间相对较长,本次故障分析和排查过程对类似数据链通信系统故障的快速诊断与修复具有较大参考价值。