星地高速数传系统低复杂度可重构LDPC编码器设计

2022-01-04安军社王冰冰

康 婧 安军社 王冰冰②

①(中国科学院国家空间科学中心 北京 100190)

②(中国科学院大学 北京 100049)

1 引言

空间探测任务中,近地轨道(Low Earth Orbit,LEO)卫星因具有发射成本低、通信时延小和覆盖范围广等优势而被广泛应用。随着空间探测任务需求愈加复杂、卫星有效载荷传感器精度不断提高,星地链路传输数据量大大增加[1],如何在星上硬件资源、带宽和功率受限的情况下实现高速数据传输已成为我国目前航天器发展需要解决的核心难题。良好的信道纠错编码对于提高数传的抗干扰性、传输可靠性和传输功率受限情况下的数据传输容量十分重要,与高阶数字调制技术相结合还可以解决带宽受限问题[2],因此探索一种合适的信道编码方案对当前空间通信的发展具有重要意义。

低密度奇偶校验(Low Density Parity Check,LDPC)码由Gallager[3]于1962年在其博士论文中提出,是一种纠错性能逼近Shannon极限的信道编码技术,具有译码复杂度低、误码平层低等优势,已广泛应用于多种通信标准,如DVB-S2, CCSDS,IEEE 802.11n等。针对航天通信应用,国际空间数据系统咨询委员会(Consultative Committee for Space Data Systems, CCSDS)制定了《131.0-B-2遥测同步及信道编码》标准[4],规定了近地卫星通信应用和深空通信应用的两套LDPC码字,其中近地卫星通信部分采用了码率为7/8的准循环(8176,7154) LDPC码。

CCSDS标准规定的(8176, 7154)LDPC码是一种准循环LDPC(Quasi-Cyclic, QC-LDPC)码,可利用循环移位寄存器实现线性复杂度的编码[5,6]。文献[7]实现了满足航天应用需求的串行编码电路,其实现复杂度低,但所需编码时钟周期数和信息比特位数成正比,码长较长时编码数据吞吐率不能满足高速数传需求。文献[8]提出了一种高效低功耗低并行度的编码方案,文献[9-12]实现了并行度更高的编码器。并行编码电路可以满足高编码数据吞吐率要求,但其硬件资源消耗大,功耗高。文献[13-15]提出了可重构设计思想,以改善系统性能。本文面向LEO卫星星地高速数传系统,针对CCSDS近地卫星通信标准提出了一种低复杂度可重构LDPC编码器设计方案,并进行了硬件实现验证。

2 LDPC编码算法

2.1 CCSDS标准LDPC编码算法

LDPC 码的编码算法可以分为两类:基于生成矩阵的编码算法和基于校验矩阵的编码算法[16]。基于生成矩阵的编码算法直接将生成矩阵与信息比特进行矩阵运算,这种编码算法简单且易于实现,但编码复杂度高,正比于码长的平方。而CCSDS近地卫星通信标准采用的是码率为7/8的(8176,7154)LDPC码,该码是一种QC-LDPC码,可以利用移位寄存器实现线性复杂度的编码,其生成矩阵G是大小为7154× 8176的矩阵

基于生成矩阵的编码算法为

2.2 并行编码算法

为缩短编码周期,提高编码数据吞吐率,在CCSDS标准LDPC编码算法基础上,通过对输入信息比特进行插0处理和拆分循环矩阵,可以实现并行编码算法。具体步骤如下:

(1)以循环矩阵Bi,j的阶数511为一段,将输入信息比特u分割为14个长度为511 bit的子向量

3 低复杂度可重构LDPC编码器

3.1 整体结构

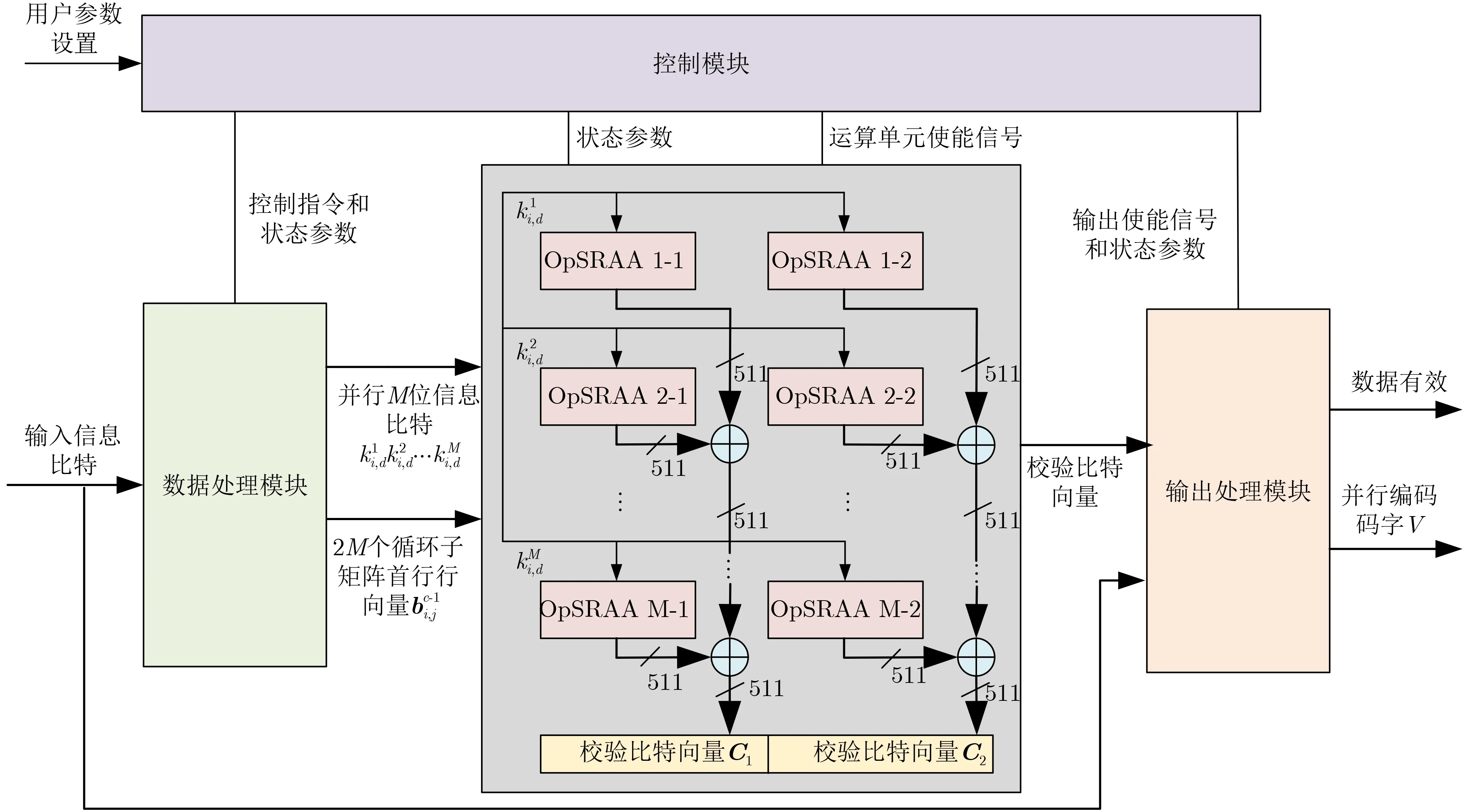

在对资源、编码数据吞吐率要求苛刻的星地数传系统中,应根据实际应用需求选择合适的编码并行度M,并行度过高,会占用大量硬件资源,并行度太低,则不能满足编码数据吞吐率要求,大多数文献中的编码器仅支持单一的编码并行度,灵活性较差。另一方面,当今飞行器和地面系统通常只能处理32 bit倍数结构的数据,(8176, 7154)码并不满足这个条件,为在实际空间通信系统中获得应用,需将(8176, 7154)码缩短和调整为(8160, 7136)码并在编码时进行添加32 bit帧头、加扰等操作[4]。针对上述需求,设计了如图1所示的低复杂度可重构LDPC编码器。包括控制模块、数据处理模块、并行编码模块和输出处理模块。

图1 低复杂度可重构LDPC编码器

3.2 低复杂度设计

图2 低复杂度可重构LDPC编码器工作流程

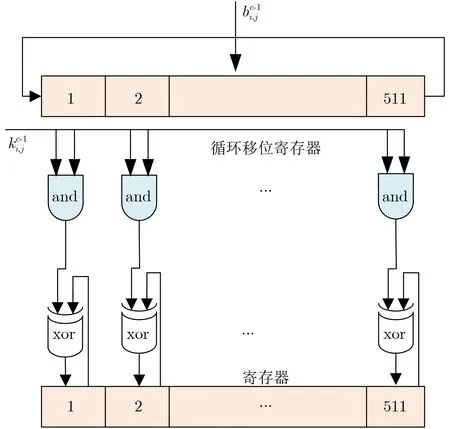

图3 SRAA单元

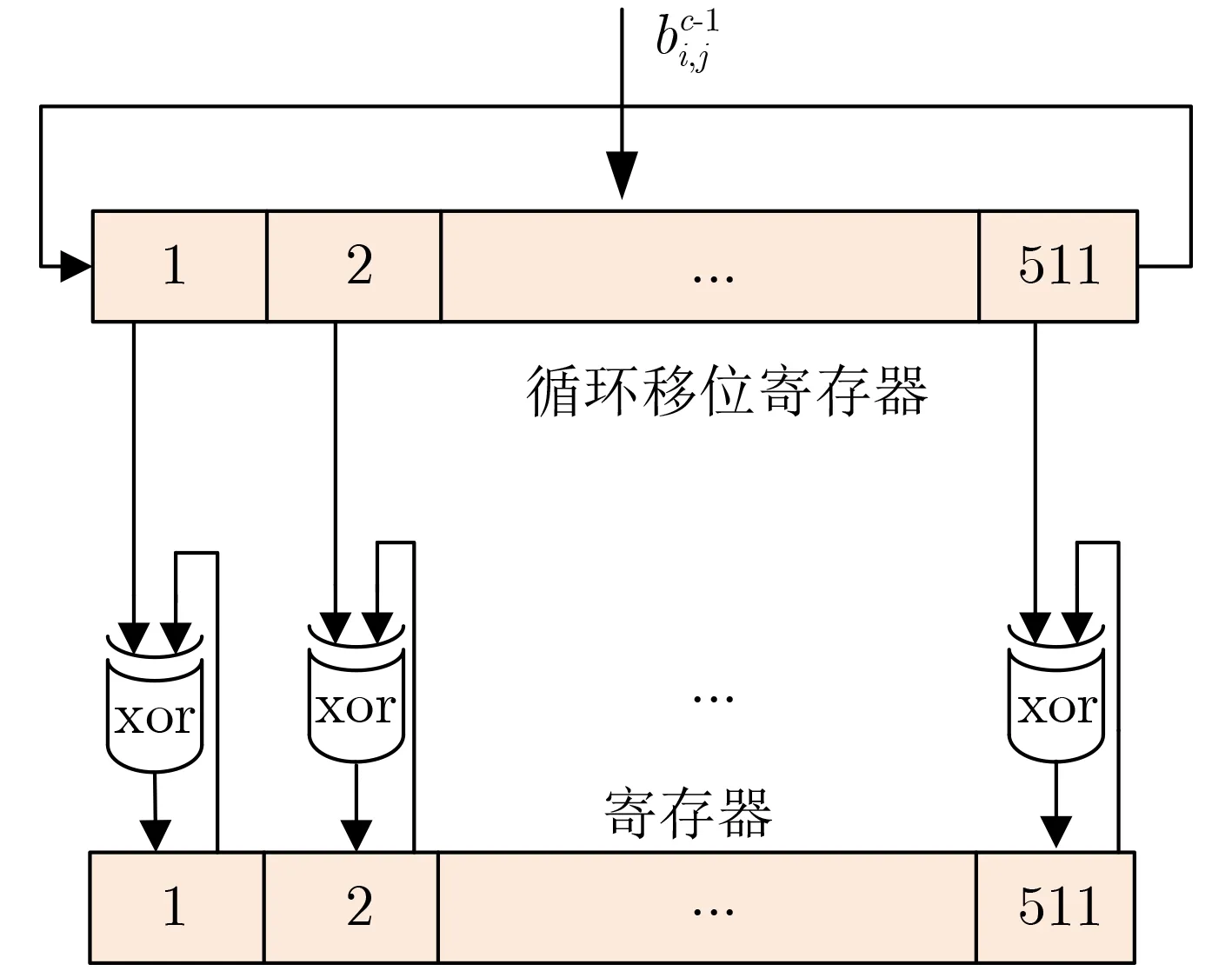

由于信息比特在二元域取值,当输入信息比特为0时,经过与门运算的结果为0,与寄存器中的值进行异或时,不会改变寄存器中的值,因此可将SRAA进行优化,只在输入信息比特为1时,将循环移位寄存器中的值和寄存器中的值进行异或并存储于寄存器中。图4为优化的移位寄存器累加单元(Optimized Shift Register Adder Accumulator,OpSRAA),该单元包括:一个位宽511 bit用于存储异或运算结果的寄存器,一个位宽511 bit用于产生和存储循环子矩阵行向量(d,:)的循环移位寄存器以及511个用于累加运算的二输入异或门。

图4 OpSRAA单元

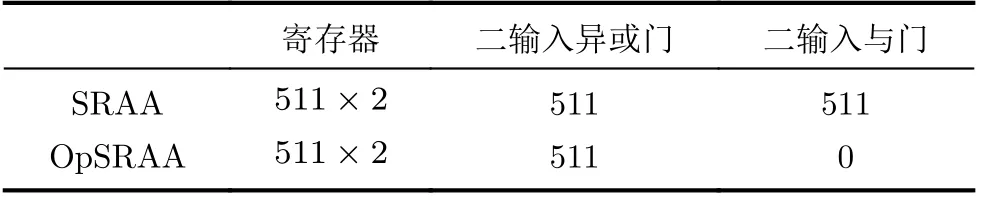

SRAA单元和OpSRAA单元所需硬件资源对比如表1所示。

表1 SRAA和OpSRAA资源对比

由以上分析知,利用2M个OpSRAA单元,经过14×N个时钟周期即可计算得到C,可节省2×511×M个二输入与门,降低了硬件实现复杂度。而且本文设计的OpSRAA对于具有准循环结构的编码具有普适性,实际应用时,只需要根据生成矩阵循环矩阵阶数改变寄存器的宽度和二输入异或门的个数。

3.3 并行度可重构设计

可重构硬件设计思想是复用硬件电路中的主要资源,在增加少量控制硬件的情况下增加系统的功能或改善系统的性能[15]。本文将可重构设计思想应用于 LDPC 编码器来改善系统性能。

综上分析,在控制模块的控制下,采用可重构思想设计的编码器可以有效保证编码器动态自适应调整以适用于不同近地卫星通信系统对编码指标、性能的不同要求,使得所设计的编码器具有灵活性与通用性,而且可以取得编码数据吞吐率和资源消耗之间的良好折中。

4 实现结果与分析

4.1 编码器硬件实现分析

对本文提出的低复杂度可重构LDPC编码器,在Xilinx XC4VLX80-12ff1148型号FPGA上进行了实现,开发环境为ISE14.7,与其它文献编码器对比结果如表2所示。

文献[8]通过插0处理和改变矩阵结构实现了2路并行编码。文献[11]利用矩阵转换的概念,即只要循环矩阵的阶数可以分解为两个互质的数,那么可按照一定规则将其转换为维度更小的块循环矩阵,由于511=7×73,因此文献[11]将511×511的循环矩阵转换为73×73的块循环矩阵实现了7路并行编码。文献[12]中800 Mbps数传吞吐率需求以及Spacewire接口和组帧模块的设计要求编码在886个时钟周期完成,因此设计了98路高并行度编码。上述文献只支持单一编码并行度,而本文提出的编码器通过插0处理和拆分循环矩阵支持2, 4和8 共3种编码并行度,具有可重构性,其中控制模块有效保证了编码器的动态自适应调整,提高了编码器的灵活性与通用性。

从表2可以看出,由于采用OpSRAA单元完成基本编码运算,本文提出的编码器寄存器资源、查找表资源与文献[8]采用SRAA单元的编码器相比分别节约了13.7%和14.8%,具有低实现复杂度。文献[11]根据转换的块循环矩阵结构和向量乘法运算规则,利用2个并行移位寄存器累加单元(Parallel Shift Register Adder Accumulator, PSRAA)实现编码,且由于编码并行度7是CCSDS标准循环矩阵阶数511的约数,可以将信息比特序列直接分割,节省了插0处理需要的硬件逻辑,而本文为兼容多种编码并行度,采用了最大化备份编码策略,因此总体寄存器资源和查找表资源消耗比文献[11]多。但文献[11]设计的PSRAA需消耗2×73个7比特寄存器、7×511个 2 输入与门、7×511个2输入异或门和146个矩阵向量乘法运算单元,具有针对性,而本文设计的OpSRAA单元只需要2个511 bit寄存器和511个二输入异或门,相较于PSRAA具有低复杂度,且对于具有准循环结构的编码具有普适性,实际应用时,只需要根据循环矩阵阶数改变寄存器的宽度和异或门的个数。文献[12]的编码器是针对OFDM链路而设计,除包括核心编码模块还包括输入输出组帧模块、数据缓存等模块,因此硬件资源占用较多。

表2 不同文献编码器对比

4.2 编码器性能分析

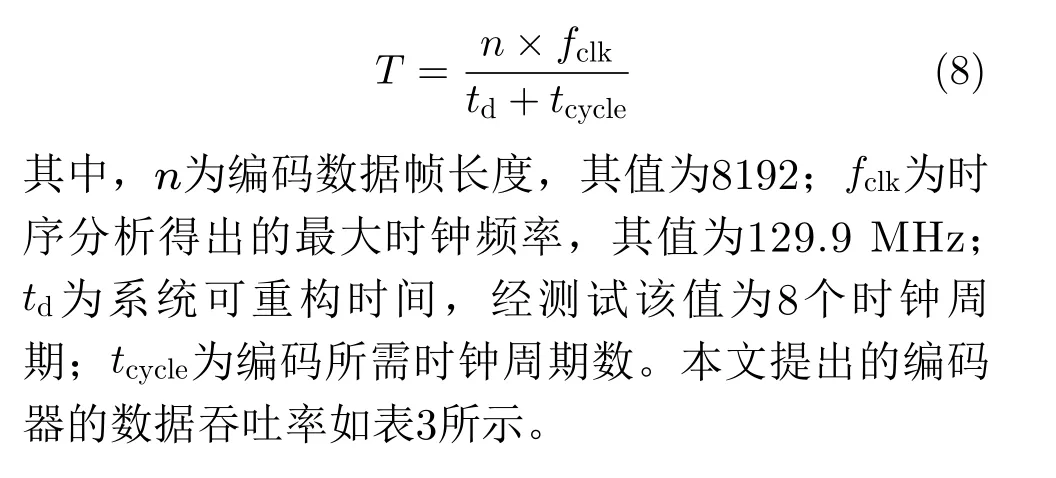

编码数据吞吐率是衡量编码器性能的一个重要指标。对于航天应用编码器,考虑其可靠性和功耗约束,将系统时钟约束为125 MHz,借助Timing Analyzer工具,对本文编码器进行时序分析,并按式(8)计算编码数据吞吐率

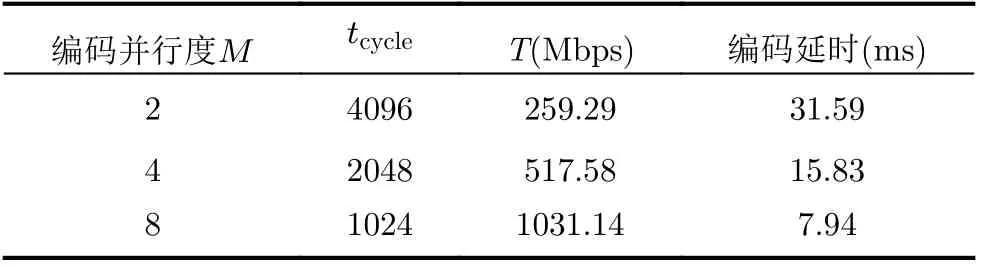

表3 本文编码器吞吐率

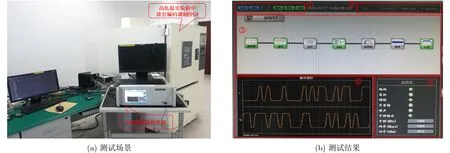

为进一步验证本文编码器的可行性及有效性,搭建如图5(a)所示硬件平台对该编码器进行实际测试并利用高速数据接收终端对其进行状态参数监控。测试时,设置编码调制FPGA系统时钟为125 MHz,LDPC编码器并行度为8,数字调制方式为QPSK,测试结果如图5(b)所示。

图5(b)中“①”指示硬件健康状态,显示当前编码调制通道的网络连接、外设驱动、FPGA温度、硬件电压等状态,绿色表示正常的硬件状态,蓝色表示正常的网络连接。“②”指示编码调制通道固件及基本性能,包括编码调制通道、FPGA固件版本以及支持的中频和调制符号速率范围。“③”指示编码调制流程图,绿色表示该模块正常工作,灰色表示该模块被旁路,从图中可看到数据源经LDPC编码和QPSK调制后输出。“④”显示I, Q调制基带波形的时域图,便于用户观察调制数据。“⑤”为编码调制状态参数显示,包括编码开关、卷积开关、调制开关、中频、噪声、码率、功率等信息,从图中可看到实测编码数据吞吐率为1 Gbps。

图5 测试场景与测试结果

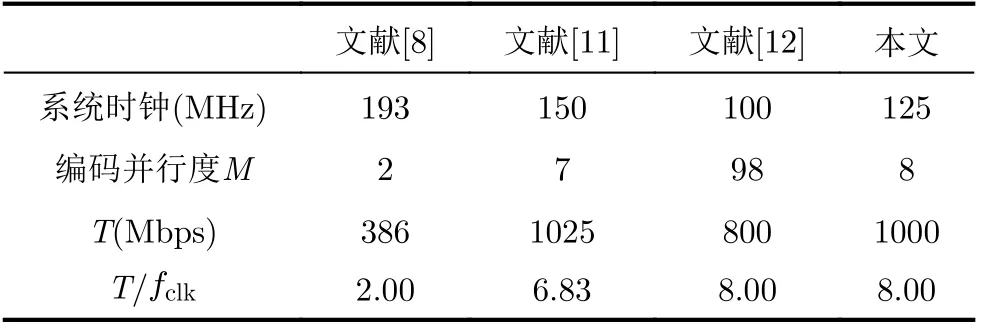

系统时钟直接影响编码数据吞吐率的大小,而系统时钟会受硬件平台影响,因此本文对系统时钟进行归一化处理,比较归一化编码数据吞吐率。本文与其它编码器归一化编码数据吞吐率比较如表4所示。

由表4可以看出,与文献[11]设计的7路并行编码器相比,本文归一化编码数据吞吐率提高了17.1%,文献[12]采用98路并行编码达到了和本文相同的归一化编码数据吞吐率。由此可见,本文设计的编码器更高效。

表4 不同文献归一化编码器吞吐率对比

综上分析,本文提出的低复杂度可重构LDPC编码器,降低了硬件资源规模,提高了编码数据吞吐率,实现了硬件资源和编码数据吞吐率之间的动态平衡,而且能够兼容3种编码并行度,提高了编码器的灵活性,可以满足不同卫星通信系统的要求。

5 结束语

本文面向LEO卫星星地高速数传系统对高通量、低复杂度、高可靠性信道编码的应用需求,提出了一种低复杂度可重构LDPC编码器。通过对输入信息比特插0处理、拆分循环矩阵并动态重构编码电路,实现了并行度可重构编码,提高了编码器的灵活性与编码数据吞吐率;采用OpSRAA 结构显著降低了编码器硬件资源。FPGA实现结果表明,本文设计的编码器,在系统时钟为125 MHz时,采用8路并行编码最高编码数据吞吐率可达1 Gbps,归一化编码数据吞吐率与并行度相近的编码器相比提高了17.1%,且寄存器资源和查找表资源与相同平台已有方案相比分别降低了13.7%和14.8%。综上,本文设计的编码器在对资源、功耗、编码数据吞吐率要求苛刻的LEO卫星星地高速数传系统中具有较高应用价值。