1 280×1 024 DI型多功能红外焦平面阵列读出电路设计

2021-11-12裘天慧夏晓娟刘琦关钰

裘天慧 夏晓娟 刘琦 关钰

摘 要:为适应第三代红外探测器的需求, 提出一种大阵列低功耗的1 280×1 024红外读出电路设计方案。 在分析各模块实现的基础上, 重点设计了超大阵列像素单元的低功耗读出实现和阵列工作时序, 提高了输出缓冲器对外部系统的驱动能力, 并实现了边积分边读出以及多路输出功能。 在温度80 K、 时钟频率5 MHz的工作条件下, 对像素阵列窗口进行了四路、 八路读出仿真以及线性度仿真, 输出帧频可以达到60 Hz, 输出摆幅为1.6~4.8 V, 最大功耗小于450 mW, 线性度为97.76%。

关键词: 红外焦平面; 读出电路; DI结构; 互补并联结构; 红外探测器

中图分类号: TJ765.3+33; TN215文献标识码: A 文章编号: 1673-5048(2021)05-0114-05

0 引 言

红外成像技术是将物体的红外辐射转化为图像的一种高新技术。 自19世纪红外辐射概念提出, 不同形式的红外成像技术经过不断的发展和改进, 已经在军事军备、 工业生产、 医疗卫生等众多领域得到了广泛的应用[1]。

红外焦平面阵列(Infrared Focal Plane Arrays, IRFPA)是一种先进的红外探测系统, 被广泛应用于红外成像领域, 具有检测并处理红外辐射的功能, 其中读出电路(Readout Integrated Circuit, ROIC)是组成红外焦平面阵列至关重要的部分[2-4]。 读出电路负责为探测器阵列提供稳定可靠的电压偏置, 将输入电流积分转化为电压信号, 并经过放大和缓冲转化为合适的输出电压供后续模块使用。 除此之外, 读出电路还会搭载数字控制模块, 实现多种开窗以及时序控制功能, 因此, 读出电路的性能决定了红外焦平面阵列的成像质量。

随着微电子技术和集成电路加工工艺的进步, 为进一步提高红外焦平面探测器的探测距离和识别能力, 研究者对第三代探测器提出了大于1K×1K的阵列规模要求[5]。 而随着阵列的扩大, 十几万个像素的同时积分造成功率增大以及帧频的下降, 很多问题亟待解决[6]。 针对这些问题, 本文提出了一种1 280×1 024规模的红外焦平面读出电路, 重点设计了像素单元内的电流放大电路, 不仅满足了应用环境对于红外读出电路分辨率的要求, 还降低了每个单元像素在积分读出过程中消耗的功率。 此外, 还调节了阵列工作时序, 可边积分边读出, 最多可实现八路同时输出, 提高了读出电路的读出速度。

1 读出电路架构

本文使用台积电0.35 μm标准CMOS工艺设计了1 280×1 024-25 μm 单色红外读出电路, 架构如图1所示, 分为模拟通路部分与数字时序控制电路部分。

模拟通路部分包含像素单元阵列、 列采样缓冲电路以及输出缓冲电路模块。 输入来自探测器的注入电流, 输出连接至后续ADC系统。 三个模块形成的模拟信号链路负责将探测器产生的光电流积分采樣、 放大保持、 转化为相应的电压信号, 最终通过多路输出传输到后级系统中, 每个模块的性能将直接影响读出电路的信号质量。

像素单元阵列首先接收探测器的光电流信号, 并通过积分转化为电压信号, 直接影响光电流的转换效率和功率以及最终的线性度。 为了提升大阵列读出电路的帧频, 像素单元可以分别控制积分电容与采样电容的积分与放电, 通过数字模块实现边积分边读出的功能。 列采样缓冲电路对来自像素单元阵列的电压信号进行增益放大、 噪声抑制以及电平移位等进一步处理。 电路中每列共享一条列采样缓冲电路, 某一行选通之后, 该行像素单元的信号会同时采样至对应的列采样电容, 然后控制列选信号将电压依次读出。 总输出缓冲电路将列采样缓冲电路处理后的信号经由最多8个输出端口传输至外部系统, 能够驱动较大的负载。 多路输出时, 同时工作的输出缓冲器越多, 读出电路的帧频越大, 功耗也会相应增加。

偏置电路不直接处理模拟信号, 用于产生稳定的偏置电流和偏置电压, 为探测器阵列和各级缓冲电路提供合适的偏置条件。

数字时序控制电路包含串行控制寄存器组、 行控制电路以及列控制电路。 输入来自串行数字信号DATA控制字, 默认模式下对像素阵列进行满阵列读出, 也可以通过调整控制字控制模拟通路的开关信号, 实现任意大小和位置开窗、 多路输出、 功率调节、 电流调节等功能。

2 关键模块设计原理

2.1 像素单元

像素单元阵列是红外读出电路的关键部分, 极大地影响读出电路模拟信号的传输效果。 目前主要有3种像素单元注入结构: 缓冲注入结构(BDI)、 电容反馈跨阻放大器(CTIA)及直接注入结构(DI)[7-8], 如图2所示。

在选择像素单元结构时, 需要考虑注入效率、 电荷处理量、 面积以及功耗等不同方面, 并且需要保证探测器两端偏压平衡, 确保探测器产生的电流能精确反映红外辐射的大小。 探测器注入端VCOM由片外电源保持恒定, 因此输入端电压 Vx 也需要维持稳定值。

图2中, BDI与CTIA结构均利用运算放大器的虚短特性, 由另一侧输入端的偏置电压 V b来保证 Vx 的稳定, 结果较为精确。 但是放大器结构会极大地增加像素单元的面积和功耗, 而DI结构构造简单, 只需要控制采样与

复位的晶体管即可实现电流积分的功能, 适用于对单位像素单元的面积与功耗要求较高的大阵列读出电路。 DI结构中由 Vb控制的注入管工作在亚阈值区, 相对于另外两种结构产生的电流较小, 进一步降低功耗。 此时, 电压 Vx 遵循MOS管亚阈值区的电流-电压关系:

ID= I0 exp Vcs- V TH ηV T-exp V DS V T (1)

式中: I D为漏端电流; I0 为一个与MOS管相关的相对常量; VGS为栅源电压; VTH为阈值电压; η (>1)为一个非理想因子; V DS为漏源电压; VT= kT/q , k 为玻尔兹曼常数, T为温度, q为电子电荷量。 由于亚阈值区探测器的电流-电压呈指数关系, 当探测器注入的电流较为恒定时, 注入管偏置电压变化极小, 因此确定 V b之后, Vx 能够保持稳定。

DI结构的注入效率:

ηDI= gm RD 1+gm R D(2)

由式(2)可知, 在高背景条件下, 由于输出电阻较大, DI结构能够提供较高的注入效率。 综合各方面考虑, 本文采用结构简单、 面积小、 功耗较低, 同时注入效率高的DI结构作为像素单元结构。

2.2 列级放大器电路

列级放大电路负责将像素单元阵列采样积分后的电压信号按照一定的顺序读取后, 进行放大与移位处理, 再传输至后级的输出缓冲器进行输出, 由处理电压大小的电荷放大电路、 电平移位电路以及驱动后级模块的输出缓冲电路组成。 在大阵列红外焦平面读出电路中, 由于连接了大量的像素输入单元以及后续电路, 列输入总线以及列输出总线都有很大的寄生电容。 电荷放大电路前后分别连接电平移位电路与列输出缓冲电路, 能够有效隔绝放大器与输入输出总线, 减少寄生电容对信号建立时间的影响, 提升放大器速度并减少电路功耗。

为进一步提高大阵列读出电路的能量利用效率与帧率, 列输出缓冲部分采用时序调整及总线分割的方法, 降低负载电容与电容功耗, 提高信号传输速度。

2.2.1 列输出缓冲电路工作时序

列输出缓冲电路位于结构末端, 需要驱动整个总线, 若要在读出期间时刻保持1 280个输出缓冲器单元处于工作状态, 会消耗极大的功耗。 因此, 芯片中设计了相应的时序, 采用动态选择的工作方式, 仅在选择到当前列时开启相应的列输出缓冲电路, 可以大大降低整个放大电路的功耗。

列输出缓冲器的电路如图3所示。 M1~M6构成主体放大器, 其中由M5和M6管构成双尾电流源结构, COL_C1和COL_C2为偏置电压, 控制电流源大小。 不同工作状态下的尾电流情况如图4所示, I DS5和 I DS6分别表示流过M5和M6晶体管的电流。 M5管一直保持工作状态, 提供较小的基本工作电流, 电流值约为7.7 μA; M6管由列选择信号 LESL(i)进行控制。 当列选信号有效时, 右侧电路打开使M6 导通, 经过M6的尾电流可以达到900 μA。 两个尾电流管提供的大偏置电流使缓冲器具有较大的驱动能力, 能够驱动电容负载较大的列输出总线, 但是也面临放大器功耗过高的问题。

列输出缓冲器的工作时序如图5所示, 其中CLK为时钟信号, LSEL(i)为第i列的列选信号。 列选信号有效时间为一个时钟周期, 前半个时钟周期开启M6进入大电流模式, 从而在列输出总线上建立信号, 并且在列选信号有效的后半个时钟周期输出。 由此可以保证每半个时钟周期仅有2个列输出缓冲器的选择信号选通, 大幅降低了电路的功耗。

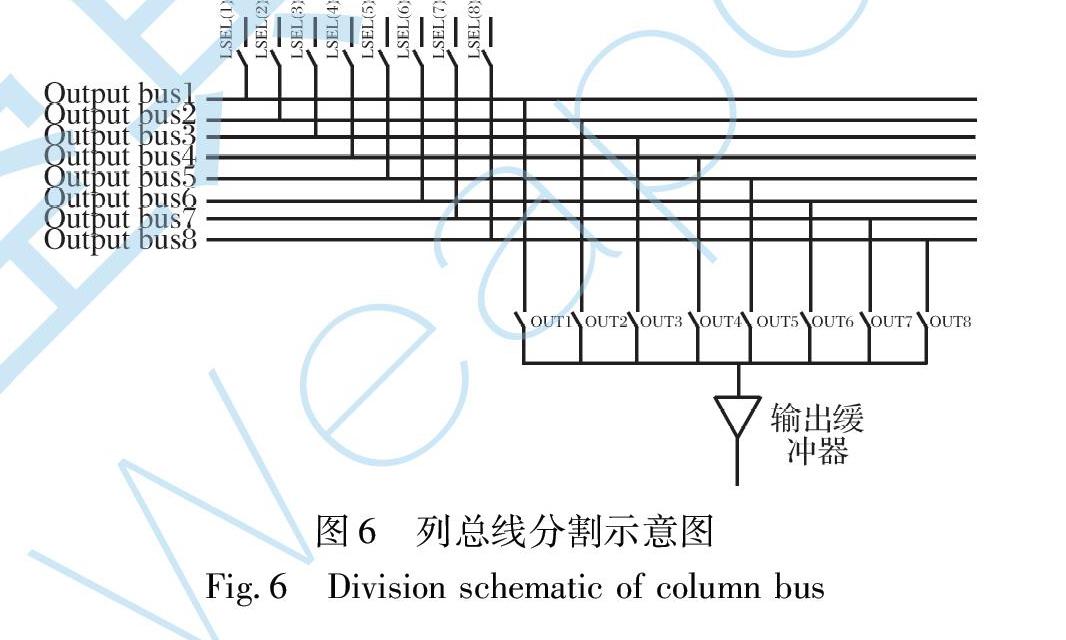

2.2.2 列输出总线分割设计

为解决大阵列读出电路中列输出总线寄生电容过大的问题, 通过总线分割对输出电路进行分组, 可以减少缓冲器的负载, 从而有效降低输出时的功耗。 列输出总线上的总寄生电容 C bp可以表示为

C bp=1 280( C dp+ C dn)+1 280 WLC metal+23 W B LB Cox (3)

式中: C dp和 C dn分别为传输门中PMOS和NMOS的漏电容、 列选通开关的寄生电容; 第二项为金属互联线的寄生电容, C metal为金属互联线的单位面积电容; 最后一项表示输出端MOS管的栅电容。 由此可得输出总线的信号建立时间为

T setup= Cbp V swing I SS+ τ ln1ε(4)

式中: 等号右边第一项为大信号建立时间, Vswing为最大电压摆幅, ISS为由尾电流源提供的偏置电流; 第二项为小信号建立时间, τ 为时间常数, ε为增益误差精度。 由式(3)~(4)可以看出, 大阵列会造成开关和传输线寄生电容的增加, 因此, 可以通过总线分割减少缓冲器负载, 从而缩短信号建立时间, 保证输出电压的稳定性。

总线分割的示意图如图6所示, 将列级放大电路的输出端依次连接至分割后的总线, 每组总线仅带载160个CMOS传输门开关和160条金属互联线, 可以大幅减少式(3)中的前两项寄生电容, 有效解决了电路负载电容过大的问题。

2.3 输出缓冲电路

输出缓冲电路将前端模拟通路处理后的电压信号直接输出至芯片外部, 因此, 需要保证输出电压的稳定性, 并使电压输出范围与后续系统匹配。 为了使输出缓冲电路具有更大的输出摆幅和驅动带载能力, 模块中采用了放大器互补并联的结构, 替代原有的传统缓冲器结构。

输出缓冲器的电路结构如图7所示, 该结构含有以NMOS和PMOS为输入对管的传统运算放大器, 将其并联得到互补并联的运算放大器结构, 此结构的输出电压范围为

V 0D9≤ V OUT≤ V DD- V 0D2(5)

式中: V OD i 为MOS管 Mi 的过驱动电压; V DD为电源电压。 传统运算放大器结构由于要满足尾电流源MOS管的偏置电压要求, 输出摆幅受到较大限制, 通过采用这种互补结构则可以使输出电压具有接近轨到轨的摆幅。

为了增强输出驱动能力, 放大器两侧MOS管运用了非对称设计, 输出侧MOS管的宽长比要大于输入侧MOS管的宽长比, 从而使输出侧MOS管获得更大的偏置电流, 具有更强的输出负载能力。 晶体管宽长比关系如式(6)所示, αi 为MOS管 Mi 的宽长比。

α1α2=α7α6=K1, α3α4=α9α8=K2 (K1, K2>1)

(6)

3 电路仿真结果

在温度80 K、 时钟频率5 MHz的工作条件下, 采用边积分边读出模式, 对16×32大小的像素阵列窗口进行了四路、 八路读出以及线性度仿真。

3.1 多路输出仿真

在边积分边读出模式下对像素阵列进行仿真, 得到的主要时序控制信号与四路、 八路输出信号的仿真结果如图8~9所示。

图中, CLK为时钟信号, OUTA~OUTH为8个输出端口, 输出端口每半个CLK读出一列。 由图中波形可以看出, 四路输出条件下, 在标志一帧读出开始的帧同步信号有效之后, 经过3次行同步信号的缓冲, OUTA~OUTD开始同时输出对应列电压, 每一行的读出宽度为4个CLK, 一共读出32列。 在八路输出条件下, 同样在行同步信号到来后输出该行对应列的电压信号, 每一行的读出宽度为2个CLK, 一共读出32列。 经过验证, 两种模式下都可以正常实现多路输出功能。

3.2 线性度仿真

线性度仿真选择像素阵列的测试行, 将0~3.1 nA的电流按照0.1 nA的间隔注入该行的32列像素单元, 并记录对应的输出电压。 不同注入电流与其对应输出电压值如表1所示。 根据计算可知非线性度为2.24%, 线性度为97.76%。

列级与总输出缓冲模块中, 电压信号通过栅漏短接的输出晶体管传输至后端, 因此随着探测器注入电流的增加, 缓冲模块的输出电压以及 V DS相应增大, 工作在饱和区的晶体管的输出阻抗 rO也会随之增大[9]。 不同电压下输出阻抗的变化会导致放大器增益的变化, 引入了一定的非线性特性。

4 结 论

为适应第三代红外焦平面读出电路的要求, 本文吸收和继承了刘琦等人设计的640×512红外焦平面阵列读出电路的技术特点, 设计了1 280×1 024规模的大阵列读出电路。 在像素单元中使用了DI结构, 并通过控制列输出部分的时序以及总线分割, 降低电路工作时的功耗。 电路具备边积分边读出以及先积分后读出两种工作时序, 支持像素阵列任意位置的开窗。 经过验证, 可以实现四路/八路同时输出, 并具备较大的输出范围和较高的线性度。 读出电路的主要性能参数如表2所示。

在实现大阵列读出电路的同时, 还需要保证电路能够适应多波段读出的探测器, 应用于更复杂的红外探测环境。 因此, 下一步研究将致力于解决大阵列像素单元下同时处理两个波段红外辐射的问题, 实现双色读出的功能。

参考文献:

[1] 刘琦, 夏晓娟, 徐申, 等. 640×512-25 μm多功能红外读出电路设计[J]. 航空兵器, 2019, 26(2): 90-95.

Liu Qi, Xia Xiaojuan, Xu Shen, et al. Design of 640×512-25 μm Multi-Function Infrared Readout Circuit[J]. Aero Weaponry, 2019, 26(2): 90-95. (in Chinese)

[2] Scribner D A, Kruer M R, Killiany J M. Infrared Focal Plane Array Technology[C]∥Proceedings of the IEEE, 1991, 79(1): 66-85.

[3] Hsieh C-C, Wu C-Y, Jih F-W, et al. Focal-Plane-Arrays and CMOS Readout Techniques of Infrared Imaging Systems[J]. IEEE Transactions on Circuits and Systems for Video Technology, 1997, 7(4): 594-605.

[4] Belmonte P N A, Monteiro D W L. A Readout Integrated Circuit for Sensitive Infrared Photo Detection Operating in Intense Backgrounds [J]. Sensors and Actuators A: Physical, 2020, 304: 1-11.

[5] 白丕績, 姚立斌. 第三代红外焦平面探测器读出电路[J]. 红外技术, 2015, 37(2): 89-96

Bai Piji, Yao Libin. Read Out Integrated Circuit for Third-Generation Infrared Focal Plane Detector[J]. Infrared Technology, 2015, 37(2): 89-96. (in Chinese)

[6] 陈伯良. 红外焦平面成像器件发展现状[J]. 红外与激光工程, 2005, 34(1): 1-7.

Chen Boliang. Development State of IRFPA Imaging Device[J]. Infrared and Laser Engineering, 2005, 34(1): 1-7. (in Chinese)

[7] 李辛毅. 紅外焦平面阵列读出信号处理电路设计关键技术研究[D]. 天津: 天津大学, 2010.

Li Xinyi. Study on Key Techniques for Infrared Focal Plane Array Readout Signals Process Circuits Design[D]. Tianjin: Tianjin University, 2010. (in Chinese)

[8] Song P Y, Ye Z H, Hu W D, et al. Injection Efficiency of DI and CTIA Readout Integrated Circuit[C]∥International Conference on Numerical Simulation of Optoelectronic Devices (NUSOD), 2015: 81-82.

[9] 毕查德·拉扎维.模拟CMOS集成电路设计[M].陈贵灿, 程军, 张瑞智, 译.西安: 西安交通大学出版社, 2003: 481-483.

Razavi B. Design of Analog CMOS Integrated Circuits[M]. Translated by Chen Guican, Cheng Jun, Zhang Ruizhi. Xian: Xian Jiaotong University Press, 2003: 481-483. (in Chinese)

Design of 1 280×1 024 DI Multi-Functional IRFPA Readout Circuit

Qiu Tianhui1, Xia Xiaojuan2, Liu Qi1*, Guan Yu3

(1. Southeast University, Nanjing 210096, China;

2. Nanjing University of Posts and Telecommunications, Nanjing 210023, China;

3. Infrared Detector Technology Key Laboratory of Aeronautical Science and Technology, Luoyang 471009, China)

Abstract: To meet the needs of the third generation infrared detector, a design of 1 280×1 024 pixel infrared readout circuit with large array and low power consumption is proposed. Based on the analysis of each module, low-power readout and working sequence of super array pixel unit are mainly designed, which improves the driving ability of the output buffer to the external system, and the integration while reading and multi-channel output functions are realized. Under the working conditions of temperature of 80 K and clock frequency of 5 MHz, 4-way and 8-way readout and linearity simulations of pixel array window are performed. The output frame rate could reach 60 Hz, the output voltage swing is 1.6~4.8 V, the maximum power consumption is less than 450 mW, and the linearity is 97.76%.

Key words: IRFPA; readout circuit; DI structure; complementary parallel structure; infrared detector