基于特高频传感器的局部放电信号并行采集系统设计∗

2021-10-27代少升刘仁光刘

代少升刘仁光刘 凯

(1.重庆邮电大学通信与信息工程学院,重庆400065;2.重庆市信号与信息处理重点实验室,重庆400065)

局部放电检测技术是气体开关绝缘设备(Gas Insulated Switchgear,GIS)故障检测的关键技术,是高压电站安全稳定运行的前提[1-4]。GIS内部绝缘缺陷类型主要有:金属尖端、自由金属颗粒、悬浮电极等,针对于不同的缺陷类型,其放电的波形的时域特征参数(均值、最大最小值、峰值、方差、偏斜度、陡度等)具有明显的区别[5],放电脉冲的时域特征参数也是区分不同放电类型的主要依据。目前,主流局部放电信号检测方法有:超声波传感器检测法、特高频传感器检测法、脉冲电流法。

文章在特高频传感器的基础上,致力于研究如何利用分时交替并行采样技术实现系统采样率的提升。分时交替并行采样技术,即TIADC(time-interleaved analog-to-digital,TIADC)技术,以4片最大采样速率为250 MHz的AD9481模数转换芯片实现了最大采样率为1 GHz。该方法具有成本低和配置灵活的优点,用户可以自行配置250 MHz~1 GHz的采样率。此外,围绕分时交替并行采样技术引入的系统偏置失配误差、增益失配误差以及时延失配误差,提出了基于LMS迭代的自适应偏置与增益失配校准算法以及基于Farrow结构的分数延时滤波器的时延失配校准算法。

1 系统体系结构

系统以Xilinx Kintex-7 XC7K160T-2FFG676I FPGA芯片为主控核心,完成系统的采样、缓存以及误差校正。系统包含AD采样前置电路、高速数据缓存、以及误差校正等模块,系统结构如图1所示。

图1 系统结构图

1.1 AD采样前置电路

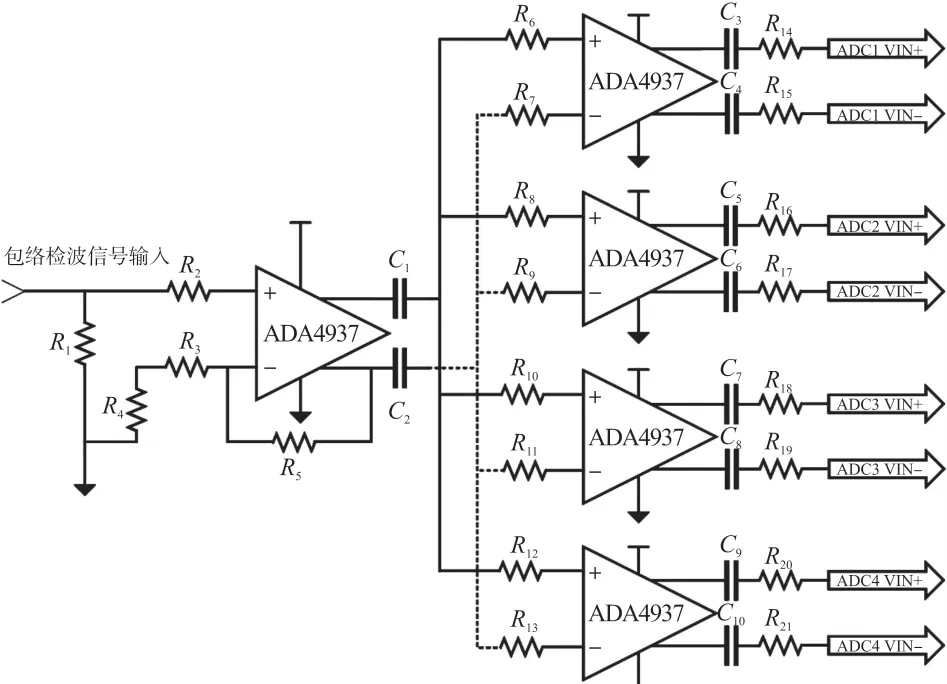

TIADC技术需要送入四片ADC芯片的信号是完全相同的模拟信号。设计中AD9481采用差分的方式接收数据,先将单端的包络检波后的信号转换成差分输出,再驱动成四路完全相同差分信号,输入给高速的AD采集芯片AD9481。AD采样前置电路如图2所示。

图2 AD采样前置电路原理图

AD采样前置电路核心由5片ADA4937运算放大器组成,ADA4937-3 dB带宽为1.9 GHz,其可实现单端到差分或者差分到差分的操作,具有可调的共模输出电压,可以通过一个电阻调节增益。

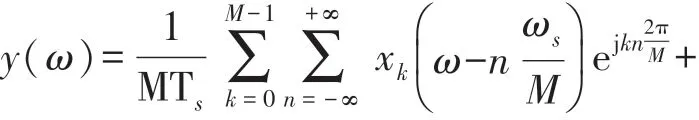

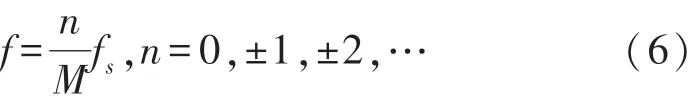

1.2 时间交替并行采样原理

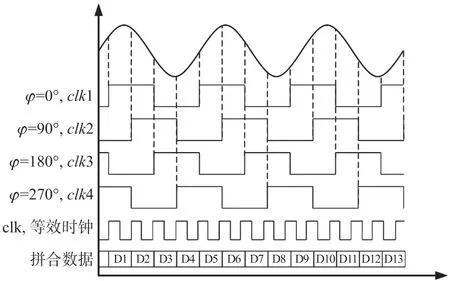

TIADC技术利用多片低速的ADC时间交替并行采集,再对各通道数据进行拼合,从而实现高速数据采集。M路子ADC采集通道,可达到的最高采样频率为fs,fs/M为单通道的采样频率,图3为4路并行通道采样的时序图,各ADC通道相位相差90°。

图3 4片ADC分时交替采样时序图

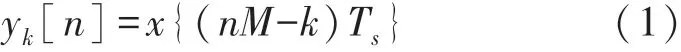

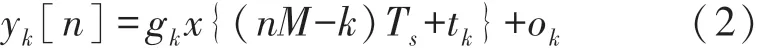

理想情况下,由各子通道进行拼合得到的数据,与采样率为fs的单片ADC采样结果一致。然而实际应用中,各ADC芯片性能并不完全一致、各ADC基准电平也有差异以及PCB布局布线使得相位有延迟,这些都将引起通道之间的失配误差[6]。由参考电压不一致引起偏置失配误差;各通道增益不一致引起增益失配误差;各通道时钟相位延迟不一致引起时延失配误差。无失配误差时,单通道ADC的理想输出为:

实际情况下考虑失配误差的存在,实际的输出为:

上述两式中gk,ok,tk,Ts分别表示第k个子通道增益失配误差、偏置失配误差、时延失配误差及多通道并行采样周期。由于这些失配误差的存在,导致实际的输出数据中存在杂散谱,降低了采样精度。因此必须采取有效措施进行校准补偿。

2 数据缓存及误差校准

2.1 数据缓存

系统以Xilinx 7系列芯片XC7K160T-2FFG676I作为主控芯片。Kintex 7系列芯片,具有基于6输入查找表的高性能FPGA逻辑;具有高性能的I/O逻辑资源,支持DDR3的速率高达1 866 Mbyte/s;内置千 兆 收 发 器,最 大 速 率 从600 Mbyte/s到6.6 Gbyte/s,提供特殊的低功耗模式,针对芯片到芯片进行了接口优化;锁相环(PLL)和混合模式时钟管理器(MMCM)可产生高精度和低抖动的时钟。

考虑到每一路ADC的采样率为250 MHz,对从接收到的单路ADC采样数据,首先经过Xilinx公司FPGA中的高性能输入串行/解串器(ISERDES)进行1∶4降速处理,将每一路250 MHz的数据转化为单路62.5 MHz的数据流,由四个异步FIFO进行跨时钟域处理。如图4所示,在进行数据拼合时,将4个异步FIFO中的数据读出来,按照采样的先后顺序进行拼合。第一路的250 MHz采样时钟作为系统时钟,利用对FIFO读使能信号的控制,实现四路ADC采样数据的拼合并存储到DDR3内存中。

图4 四路AD数据拼合时序图

2.2 偏置失配误差校准

偏置失配误差是由于ADC采样保持电路失配、各通道采样参考电压不一致以及运放失调引起。偏置失配误差特点是不随输入信号的频率变化,在时域上表现为叠加直流噪声,仅会使ADC的动态量程造成损失,在频域上偏置失配误差出现在0频附近,偏置失配误差不是频率的函数,不随输入信号的频率变化,因此可以被视为固定值[7]。偏置失配误差模型如图5所示。

图5 偏置失配误差模型

ok为第k个子ADC通道的偏置失配误差,一般视为固定值ok,由图5可知:

式中:yk[n]为第k个ADC通道的时域输出,δ(tnMTs+kTs)表示第k个通道在nMTs-kTs时刻采样。

M个通道的合路输出为:

对上式作傅里叶变换得:

式中:第一项为ADC的理想输出,第二项是由偏置失配误差造成的杂散谱。由频谱表达式可以看出杂散分量的频率分布为:

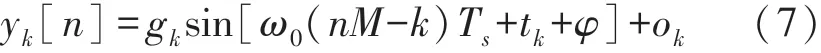

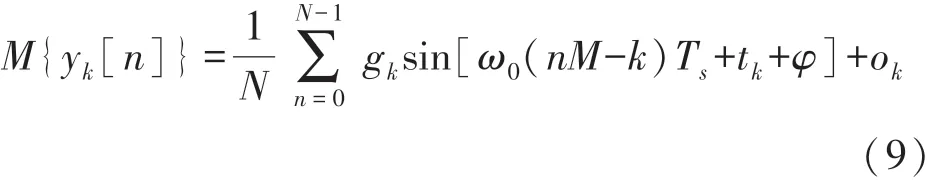

令系统输入模拟信号为x=sin(ω0t+φ),ω0为输入信号角频率,φ为信号的初相,考虑三种主要的失配误差同时存在时,第k路子ADC的输出为:

根据正弦信号的特性可知,当采样点数恰好为整数倍信号周期时,对上式求平均可得:

式(8)表明对采样信号求统计平均可以获得通道的偏置失配误差。一般条件下,对采样信号求平均可得:

由式(9)可知当采样点数足够多时,对采样信号求均值可以得到偏置误差的估计值为ok。因此对偏置误差的估计,以标准正弦信号求采样均值获得4个采样通道的偏置误差并以第一通道为基准,可以求得第k通道的偏置误差为:

2.3 增益失配误差校准

假设系统输入的模拟信号为x=sin(ω0t+φ),考虑增益误差存在的情况,第k路子ADC时域表达式如下:

传统的针对增益失配误差的校准采用的是基于FFT变换来获取各通道的增益误差[8-9],此方法计算复杂且计算量大,不便于硬件实现。对于增益失配误差,首先对输入信号求绝对值,再进行滑动平均求得平均值,由此可得参考通道和待校准通道的平均绝对值输出为:

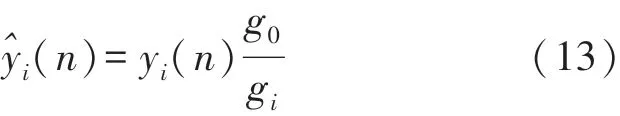

式中:gi,g0分别为待校准通道和参考通道的增益值,将|Vi|和|V0|作差,消除偏置失配误差影响。然后经最小均方滤波器(LMS)得到通道的增益失配系数,校准后的通道输出为:

2.4 时延失配误差校准

每个通道的实际采样时刻与理想采样时刻存在时间偏差,导致时延失配误差的产生。时延误差通常由采样时钟走线延迟、输入信号的线路延迟等造成。时延失配误差对直流信号不影响,因为直流信号在任意时刻的采样值一致,对于交流信号频率越高时延失配误差越大,输入信号的斜率越大所造成的时延误差越大[10-12]。

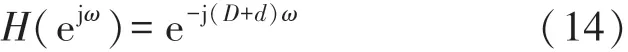

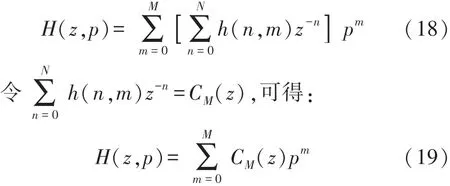

针对时延误差采用基于Farrow结构的分数延时滤波器进行校正,分数延时滤波器的系统函数如下[13-14]:

式中:D为分数延时滤波器的整数部分,d为分数延时滤波器的小数部分。对应的幅频响应为:

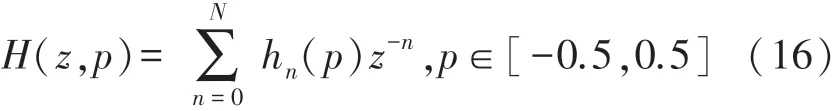

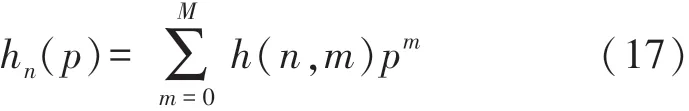

式中:p为延时部分,ω为归一化后的角频率,二者分别满足ω∈[0,απ],p∈[-0.5,0.5],其中α为[0,1]之间的小数。为了最大限度的逼近理想的分数延时滤波器,Farrow结构的分数延时滤波器的频响函数为[15-16]:

式中:hn(p)为滤波器系数是关于p的函数,以M阶p的多项式近视为:

将式(17)代入式(16)得:

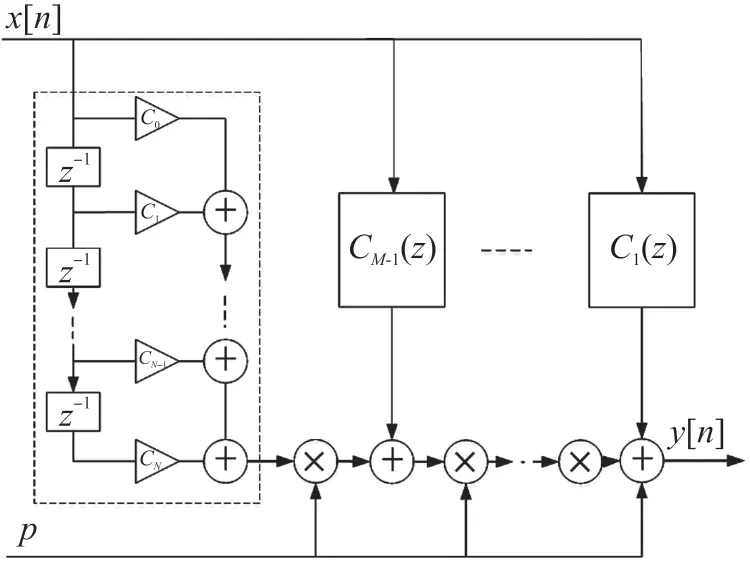

基于Farrow机构的分数延时滤波器的结构如图6所示。

图6 Farrow结构滤波器框图

3 实验结果

3.1 增益和偏置失配误差校准验证

图7 为TIADC系统增益失配和偏置失配联合校准Simulink仿真模型,时钟模块采用了脉冲PulseGenerator产生四路相位差为90°、频率为250 MHz的采样时钟,ADC采用Simulink模型库中提供的精度为8位的理想ADC,量化前引入了偏置和增益失配误差,采样量化后经LMS自适应偏置和增益失配校准模块,最后经Multiport Switch模块合路输出。Simulink仿真模型校准算法完全利用HDL Coder库搭建,方便后续转换为Verilog代码进行功能仿真进一步验证算法的有效性。

图7 增益失配和偏置失配联合校准模型

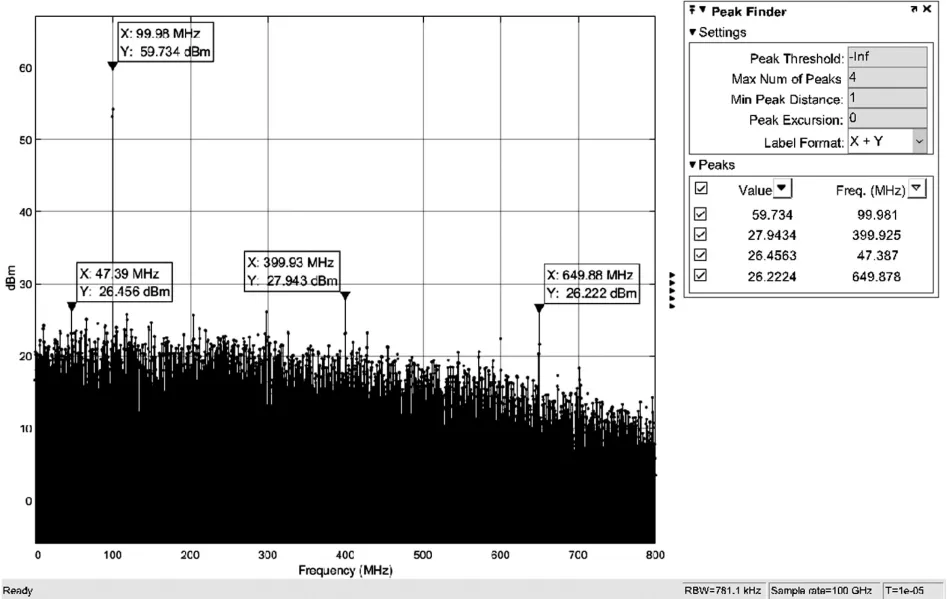

仿真参数设置如下:信号频率为100 MHz的正弦波、各通道的偏置误差为offset=[0.1,-0.05,0.07,0.2]、增益误差为gain=[1,1.1,0.7,1.02]。使用Simulink自带的频谱分析仪对校准前后的信号分别进行FFT运算得到信号的频谱分别如图8和图9所示。可以明显看出校准后由偏置失配误差和增益失配误差引起的杂散谱消失,TIADC性能得到明显提升。

图8 增益和偏置误差校准前频谱图

图9 增益和偏置误差校准后频谱图

3.2 时延失配误差校准验证

时延失配误差的校准在增益和偏置校准的基础上加入了Farrow结构的全并行分数延迟补偿模块完成时延失配误差的补偿。采样时钟的时延失配利用Simulink库中的可变延时模块添加到各通道采样保持模块的采样时钟沿,各通道的时延误差为time=[0.1,0.1,0.07,0.2],误差单位为ns,图10和图11分别为校准前后的频谱图。

图10 时延误差校准前频谱图

图11 时延误差校准后频谱图

3.3 三种失配联合校准

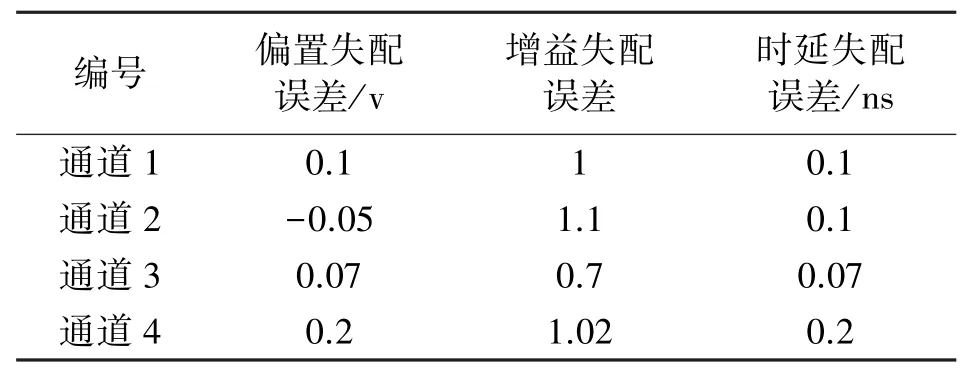

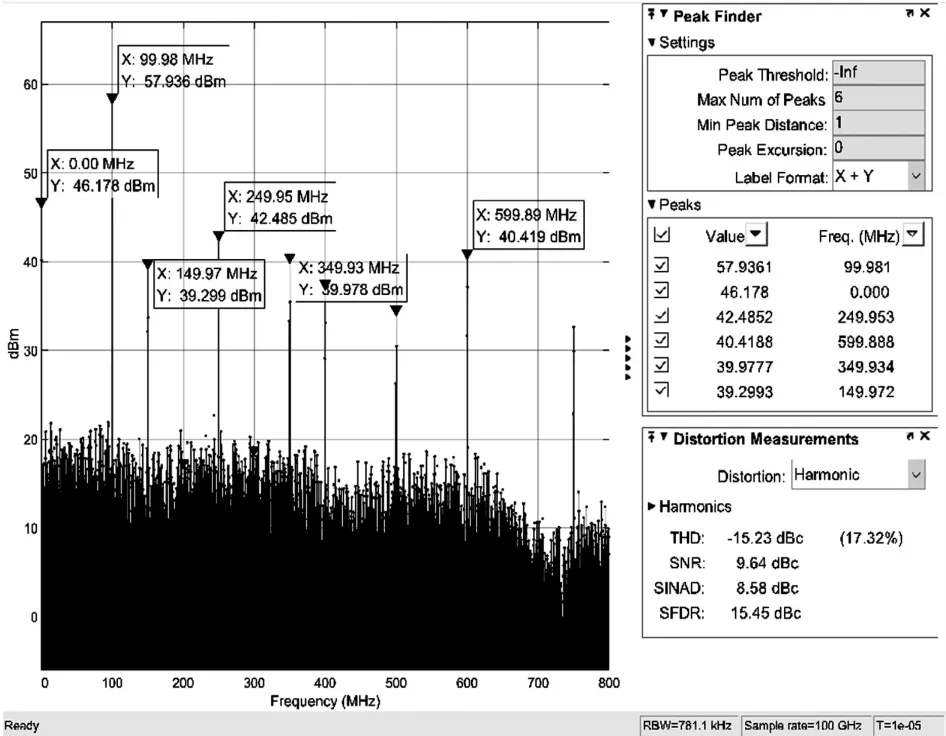

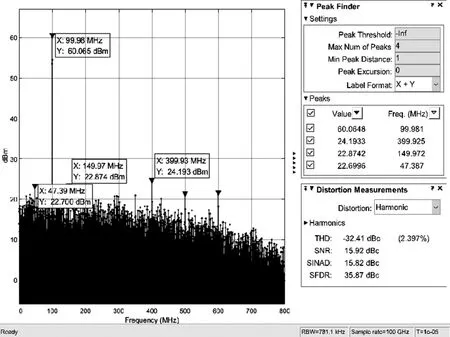

整合上述失配误差校准算法到系统中,给定失配误差如表1所示。

表1 三种失配误差值

图12 和图13分别表示在100 MHz单频信号输入信号条件下,校准前后和校准后的频谱图。表2表示TIADC校准前后动态参数对比。

图12 校准前频谱图

图13 校准后频谱图

表2 校准前后动态参数对比

通过三种失配误差联合校准前后图谱及校准前后动态参数对比可知,由失配误差引起的杂散谱得到了有效的抑制,无杂散动态范围提升到了35.87 dB。

3.4 硬件实现

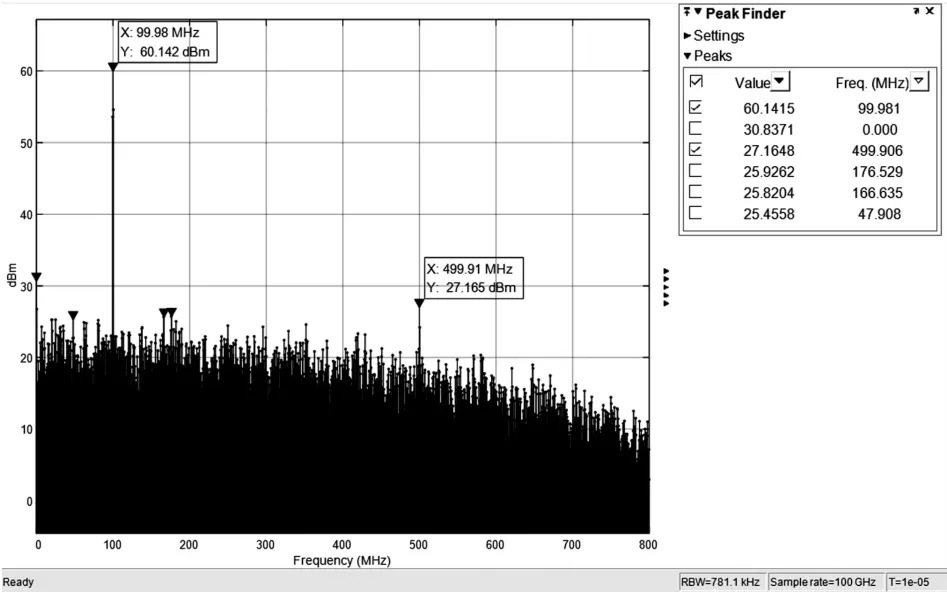

本节,利用Simulink自带的HDL Coder工具箱将误差校准算法转化为硬件描述语言,Simulink会自动生成Verilog代码,并将其加载到Xilinx XC7K160T-2FFG676I芯片。使用实验室标准信号源产生100MHz的正弦信号,通过Xilinx自带的逻辑分析仪抓取采集到数据波形并导出数据在MATLAB中分析得校准之后的频谱如图14所示,实际采集的尖端放电信号的时域波形如图15所示。

图14 FPGA采集100MHz正弦信号频谱

图15 尖端放电时域波形图

3.5 不同缺陷类型局放信号采集

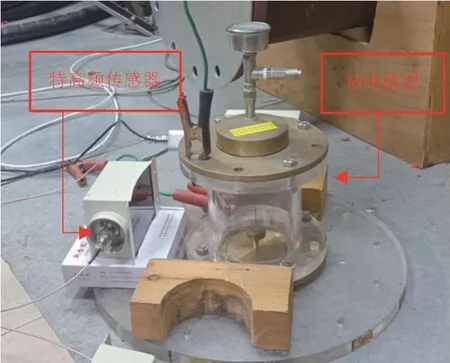

不同缺陷类型的局部放电信号产生平台如图16所示。实验中,通过图16中的放电模型产生金属尖端放电、悬浮放电、自由金属颗粒放电三种放电类型。通过FPGA采集到的采样率提升前后的波形对比如图17~图19所示。

图16 局部放电产生平台

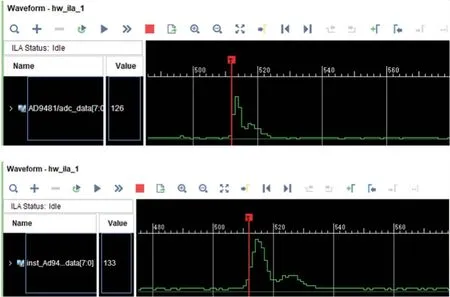

图17 尖端放电采样率提升前后波形图

图18 悬浮放电采样率提升前后波形图

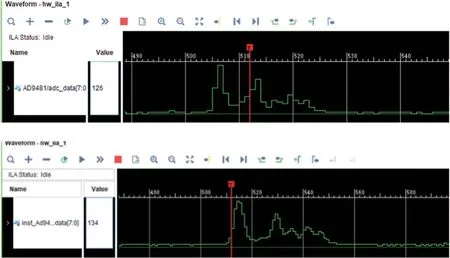

图19 自由金属颗粒放电采样率提升前后波形图

由上述三种不同放电类型的采样率提升前后的波形图对比可知,采样率的提升更好的保留了原始局放的脉冲波形特征。并且对比三种不同缺陷局部放电信号的波形图可以看出,由该系统采集到的局部放电波形能够反映不同的缺陷类型。

4 结论

本文为实现最大程度的保留特高频传感器接收的局部放电信号时域波形特征,设计了一种基于TIADC技术特高频局部放电信号并行采集系统。针对TIADC技术引入的失配误差,提出了基于LMS的自适应增益和偏置误差校准算法,对于时延失配设计并实现了基于Farrow结构的分数延时滤波器进行校准。最后实验结果表明,设计的并行采集能够实现最高1 GHz的采样率,并且针对TIADC引入的通道失配误差也得到了有效校准,有效抑制了杂散谱,在100 MHz带宽范围内无杂散动态范围提升到了35 dB。