基于FPGA的MIPS单周期处理器的实现

2021-09-27严海洲

严海洲

摘要:在MIPS CPU设计原理的基础上,通过Verilog硬件描述语言编程、使用Xilinx FPGA开发板的调试和仿真工具Vivado,实现基于FPGA的MIPS单周期处理器。最终下载到Nexys4-DDR平台上,通过ChipScope工具抓取运行过程中产生的波形进行验证。

关键词:MIPS;硬件描述语言 ; Vivado ;单周期处理器

中图分类号:TP311 文献标识码:A

文章编号:1009-3044(2021)19-0005-04

本文旨在使读者理解和掌握基于FPGA的MIPS单周期处理器的设计和实现。我们要在了解MIPS CPU设计原理的基础上,掌握Verilog硬件描述语言编程、Xilinx FPGA开发板(Nexys4-DDR)的调试和仿真工具(Vivado 2014.4)。过程大致分为用Vivado设计套件创建工程、编写 Verilog 代码、仿真测试和下载验证等四部分。

1 用Vivado设计套件创建工程

1.1 关于Vivado设计套件

Vivado设计套件是FPGA厂商赛灵思Xilinx公司2012年发布的集成设计环境,以提升生产力、缩短产品上市时间、实现可编程系统集成等目标。Vivado设计套件可实现FPGA部分的设计和开发,管脚和时序的约束,编译和仿真,实现RTL 到比特流的设计流程。包括高度集成的设计环境和新一代从系统级到IC级的工具,全新的系统级设计的中心思想是基于知识产权(IP)核的设计,Vivado工具把各类可编程技术结合在一起,能够扩展多达1亿个等效ASIC门的设计。这些均建立在共享的可扩展数据模型和通用调试环境基础上,可以让用户更快地实现设计收敛。

1.2 新工程的创建和设置

打开 Vivado设计套件(本文使用的是Vivado 2014.4)新建工程,输入工程名和存储路径如图1所示。然后选择FPGA型号、综合和仿真工具、推荐描述语言(Verilog)等配置如图2所示。

1.3 添加Verilog 模块

如图3所示,右键点击 Hierarchy 窗口,选择 Add Copy of Source ,添加已有的Verilog模块,例如 Register file,Sign Extend,Data Memory,Instruction Memory,ALU 模块。并重新定义Top 层模块和 Control。

2 编写 Verilog 代码

2.1 关于Verilog HDL

Verilog HDL(常简称为Verilog)是一种硬件描述语言,以文本形式来描述数字系统硬件的结构和行为的语言,用它可以表示逻辑电路图、逻辑表达式,还可以表示数字逻辑系统所完成的逻辑功能。Verilog HDL和VHDL是目前业界最常用的两种硬件描述语言,这两种HDL均为IEEE标准。

2.2 MIPS 单周期处理器原理概要

单周期CPU是指一条指令在一个时钟周期内执行完毕,然后开始执行下一条指令。时钟周期一般也称振荡周期。 单周期处理器的设计,关键是确定数据路径以及确定哪些操作需要时钟,哪些不需要时钟。例如对于 Data Memory 读和写就需要区别对待。将计算好的数据写到 Data Memory 需要一个时钟周期来完成。而读 Memory 的操作,意味着将读到的数据写入到 Register file,如果读 Memory 和写 Register 都需要一个时钟周期,那就无法实现单周期的处理器。所以 Data Memory写操作采用时序逻辑,而读操作采用组合逻辑,本文采用的就是这种方式。当然,还有其他方式来解决多周期修改成单周期,例如采用快慢两个时钟的方法等。

2.3 编辑 control 模块和Top 层模块

根据上述设计思路,编辑 control 模块如图4;编辑Top层模块如图5,将各个模块互联起来。

2.4 系统时钟的设置

设计的系统时钟暂定为 32MHz,外部时钟是 100MHz,需要添加一个时钟生成器进行分频处理,得到32MHz。利用Core Generator来生成时钟,右键选中 Hierarchy 窗口,选择 New Source,左侧框中选择 IP,右侧输入文件名,如图6所示。选择 IP Core 类型,这里使用 Clocking Wizard,如图7所示。然后配置 DCM 时钟参数,在 Top 模块中调用 Clk_gen 模块。

3 仿真测试

整个处理器设计基本完成,接下来编辑 testbench 文件,进行行为级的仿真。

3.1 系统的初始化

1)初始化 data memory、instruction memory 和 register 三大存儲模块,这里仅以初始化 instruction memory 为例说明,其他类推即可。该 memory 用于存储二进制代码,如图8显示。Verilog中调用了系统任务$readmemh,将Instruction文件中的数据读入到InstMem数组中。

2)编写Top层的testbench文件如图9。右键选中Hierachy窗口,选择new source,如图10所示,定义 file name为Top_tb,在左侧栏中选择 Verilog Test Fixture,点击 Next,选择Top模块,自动生成 Top_tb 测试文件。添加时钟激励,初始化其他输入信号。

3.2 仿真与观察

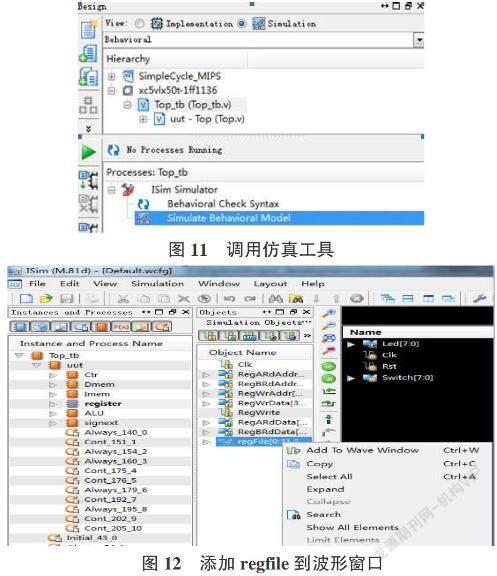

1)调用Vivado自带的仿真工具进行仿真如图11,双击 Simulate Behavioral Model。添加 register 模块中的 regfile 寄存器数组到波形窗口,观察各个寄存器的变化情况,如图12所示。