基于Vivado HLS的硬件设计效能评估

2021-09-27戴源,白雨鑫,张伟,陈鑫

戴源,白雨鑫,张伟,陈鑫

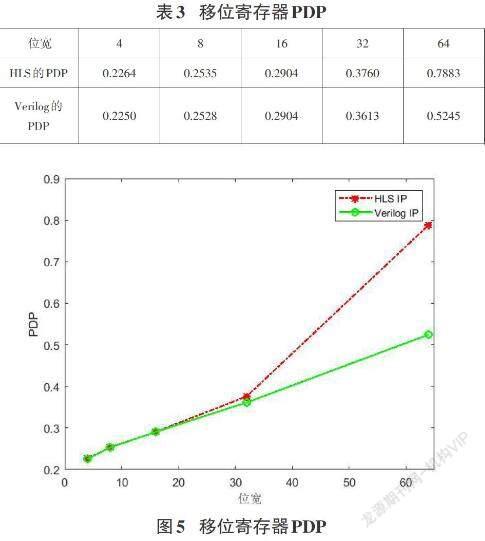

摘要:本文为了研究面向FPGA芯片的高层次综合工具Vivado HLS在硬件设计中的性能,分别利用C++语言与Verilog语言设计移位寄存器,通过比较两种设计方法在不同输出位宽下,其时序、功耗、PDP以及资源使用量上的差别来评估HLS工具在硬件电路设计上的效率与功能性。实验结果表明,虽然HLS工具综合得到的Verilog代码表现不如手工直接编写的Verilog代码,但其以高级语言作为输入的特性还是能满足让设计师在不需要掌握硬件描述语言的情况下利用FPGA实现算法加速的目的。

关键词:FPGA;高层次综合;高級语言;Vivado HLS;Verilog;PDP

中图分类号:TP311 文献标识码:A

文章编号:1009-3044(2021)19-0001-04

Effectiveness Evaluation of Hardware Design Based on Vivado HLS

DAI Yuan,BAI Yu-xin,ZHANG Wei,CHEN Xin*

(College of Electronic and Information Engineering, Nanjing University of Aeronautics and Astronautics, Nanjing 210016, China)

Abstract: In order to study the performance of vivado HLS, a high-level synthesis tool for FPGA chips, the shift registers are designed by using C ++ language and Verilog language respectively. The efficiency and functionality of HLS tool in hardware circuit design are evaluated by comparing the differences of timing, power consumption, PDP and resource usage between the two design methods under different output bit widths. The experimental results show that although the performance of Verilog code synthesized by HLS tools is not as good as that of the Verilog code written directly by hand, its high-level language as input can still meet the purpose of using FPGA to speed up the algorithm without mastering the hardware description language.

Key words: FPGA; High Level Synthesis; High Level language; Vivado HLS; Verilog; PDP

集成电路伴随摩尔定律发展至今,其复杂性已经逐渐超过人类可以手工管理的范畴。如:一颗拥有百万门级的SoC,其代码量约为20万行,完成一次规范审查和逻辑综合的时间分别为6.5和8小时[1]。因此,完全使用RTL级的逻辑抽象设计当代芯片是不现实的,复杂的代码不光开发耗时长,还大大增加了编码错误的概率,且调试和验证也非常困难[2]。

高层次综合(High Level Synthesis, HLS)技术就是一种将高级语言转换成硬件描述语言的技术,这项技术能够帮助工程师克服直接在寄存器传输层(RTL)进行开发的困难[3]。设计师们在高层次综合流程下需要注重的是系统的运行模式,HLS工具会负责生成RTL级代码。但不幸的是,HLS工具作为一种编译器,其可靠性难以得到保证,例如,Yang等人就在一些成熟、使用广泛的编译器中发现了数百个以前未知的错误[4]。况且即便是高级语言,其算法中也会存在诸如数据依赖等问题,因此想要利用HLS工具实现高性能的硬件设计,还需要从高级语言代码的编写和HLS工具优化等角度进行大量的工作[5]。

Vivado HLS是FPGA芯片公司Xilinx在2012年发布的集成开发环境中的一款高层次综合工具[6]。近年来,学术和工业界利用Vivado HLS开展了大量工作,其中张俊涛等人设计了FFT IP核[7];王春江等人设计了一套运动目标检测系统[8];齐乐等人设计了一套实时图像去雾系统[9]。然而, HLS工具综合结果与手工Verilog输入之间差异性的对比却鲜有人研究。所以本文提出在Vivado HLS工具中使用C++语言设计移位寄存器,将HLS工具综合出来的Verilog代码与手工设计的Verilog代码进行对比,通过两者之间的差异来评估HLS工具在硬件设计上的效率与功能性。因为功耗/能量效率是评估HLS工具的最重要指标之一[10]。所以,我们将需要对比两种设计统一放到测试系统中进行时序、功耗和资源使用量的对比,以达到评估其效能的目的。测试的软件平台为Vivado 2019.2,并选用Xilinx Kintex-7系列FPGA。

实验结果证明, HLS综合出来的设计整体表现与手工设计的Verilog设计基本持平,但因为HLS工具综合的设计使用的是状态机逻辑,所以其在时序和资源使用的表现上略有不足。然而,HLS工具所具备的加速设计周期的优点以及降低硬件开发门槛的特点,仍能在复杂的电路设计中发挥其作用。