真空栅介质场效应晶体管自热效应模型

2021-08-05苏亚丽赖俊桦钱俊杰叶雨欣张国和

苏亚丽,赖俊桦,钱俊杰,叶雨欣,张国和

(1.西安石油大学机械工程学院,710065,西安;2.西安交通大学电信学部微电子学院,710049,西安; 3.中国科学院微电子研究所,100029,北京)

受到高功率密度、低热导率材料、紧凑几何结构与高表面积与体积比等因素的影响[1-2],沟道内热量无法及时散出,晶格温度迅速上升,导致在20 nm及以下工艺节点被广泛运用的三维立体器件[3-5]环栅硅纳米线场效应晶体管(GAA SiNWs FET)存在严重的自热效应,诱发热载流子注入(HCI)和偏置温度不稳定性(BTI)等二级物理效应,严重威胁器件和电路的性能与可靠性。因此,纳米器件自热效应导致性能衰退的机制和改善热特性的新器件结构设计成为了近年来研究的重点和难点。

真空栅介质鳍式场效应晶体管(FinFET)是将传统FinFET[6-8]的固态栅氧化层通过刻蚀工艺去除后所形成一种新型FinFET结构,有效地改善了纳米器件HCI和BTI等物理效应[9]。但是,鳍形沟道与底部埋氧层(BOX)存在大面积接触使得BOX层仍然能够俘获高能热载流子进而影响沟道内电势分布,导致HCI和BTI等可靠性问题无法从根本上解决。Han等采用悬空硅纳米线作为沟道提出了一种气体环绕的真空栅介质GAA SiNWs FET[10],有效地解决了HCI和BTI对器件性能影响的问题。然而,真空气体作为栅介质层,其热导率(0.025 W·m-1·K-1)不足固态栅介质SiO2热导率(1.4 W·m-1·K-1)的2%,真空栅介质GAA SiNWs FET将具有更明显的自热效应。因此,需要深入分析器件内复杂的热生成与热扩散过程以揭示真空栅介质GAA SiNWs FET的自热效应机理。

目前,国内外在数值模拟预测自热效应引起的纳米器件性能衰退的方面进行了大量的研究[11],但是,在这些数值模拟研究中尚未见采用硅纳米线热导率解析模型用于修正三维纳米器件的热电数值模拟仿真模型。硅纳米线热导率存在严重的尺度效应和温度依赖关系[12],采用与温度和尺寸无关的热导率模型,如Park和Chung等在3D V-NAND flash存储器自热效应分析[13]和FinFET热SPICE建模研究[14]中采用的常数热导率,已无法衡量微纳尺度材料热输运能力[15]。这将导致所建立的数值模拟模型在结构参数设计优化过程中无法准确表征尺寸和温度变化给热传输性能带来的影响,在纳米器件热传输特性预测中造成较大误差。

本文将通过考虑温度与结构尺寸对热导率的影响,量化表达声子散色平均自由程与截面尺寸的依赖关系,建立起硅纳米线沟道的热导率模型。通过对真空栅介质GAA SiNW FET自热效应数值模拟分析,揭示器件内复杂的热生成与热扩散机制,探讨真空栅介质导热间隙与气体压强对纳米器件热传输运能力的影响,为发展真空栅介质器件自热效应抑制方法和模型预测理论奠定基础。

1 器件结构与关键参数设定

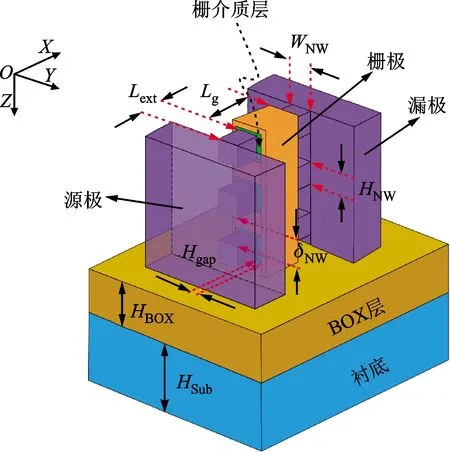

图1为垂直堆叠GAA SiNWs FET器件结构示意图,GAA SiNWs FET器件三维结构、YZ截面和俯视图分别如图1a、1b和1c所示,其中X轴平行沟道方向,Y轴水平垂直沟道方向,Z轴竖直垂直沟道方向。器件沟道由Ch1、Ch2和Ch3这3根硅纳米线垂直堆叠而成。传统的固态栅介质垂直堆叠GAA SiNWs FET器件一般采用HfO2作为栅氧化层介质。为方便对比分析两种器件结构散热能力,本文在保证其他参数不变的情况下,将固态栅介质器件的HfO2栅氧化层替换为气体材料来构建真空栅介质场效应晶体管的器件结构模型。

WNW—沟道宽度;HNW—沟道厚度;Lg—沟道长度; Lext—延伸区长度;Hgap—栅介质层厚度;HBOX—埋氧层厚度; HSub—衬底厚度;δNW—纳米沟道间距。(a)三维示意图

(b)截面图

(c)俯视图

在TCAD数值模拟仿真中,沟道和源漏分别进行原子浓度为5×1016cm-3的p型本征掺杂和1020cm-3的n型重掺杂。源、栅和漏热电极表面接触热阻为2×10-8m·K·W-1[16]。纳米尺度界面热阻对器件热传输特性有着极为重要的影响,因此在GAA SiNWs FET的高精度自热效应研究中需要考虑硅/二氧化硅界面热阻,其大小为9.09×10-9cm2·K·W-1[14]。源漏硅热导率为62 W·m-1·K-1[17],BOX层二氧化硅热导率为1.4 W·m-1·K-1。器件尺寸参数为:Lg=40 nm,Lext=25 nm,WNW=4 nm,HNW=4 nm,Hgap=5 nm。

结合器件物理参数与材料电学与热学特性,考虑纳米尺度载流子波动特性与载流子弹道输运效应,采用密度梯度量子修正模型(Density Gradient Model)、考虑温度与载流子散射的Philips载流子模型、高电场饱和模型和考虑载流子界面散射的薄层模型,修正TCAD中描述半导体器件行为的基本物理方程,包括,漂移-扩散方程以及热力学模型等,实现GAA SiNWs FET TCAD热电数值模拟仿真。

2 硅纳米线热导率模型推导

为在GAA SiNWs FET热电数值模拟仿真中能够精确预测器件内温度场分布与准确评估器件自热效应,需要建立起可用于器件仿真的温度和尺寸依赖的、基于物理参数的有源区硅热导率解析模型。GAA SiNWs FET内声子平均自由程要远大于器件有源区尺寸,声子热传输过程呈现强烈的弹道输运现象导致经典的傅里叶热扩散定律已无法揭示纳米沟道的热传输机制。通过捕捉影响声子弹道输运过程最基本的物理信息,考虑纵向和横向声子模对热导率的贡献,Holland提出了热导率的修正模型[18]。将声子弛豫时间、声子运动速度和材料尺寸等与声子弹道输运紧密相关的物理量包含于材料热导率模型,表示如下

(1)

式中:下标i=L,T,TU分别表示为单个纵向声子模态和两个横向声子模态;Θ为德拜温度;T为材料温度;vi为不同声子模态对应的声子速度;CV,i(T)为温度依赖的比热容;τi(T,NA)为温度T和掺杂浓度NA依赖的声子弛豫时间;η是考虑声子边界散射后用于修正声子弛豫时间的系数,该参数和材料特征尺寸与声子平均自由程的比值(H/ι)相关;χ=hω/(2πkBT)是声子振动频率,其中h和ω分别是普朗克常量和声子振动角频率。

Holland热导率模型过于复杂,难以植入TCAD软件以进行三维电热耦合数值模拟分析,因而针对立方晶体结构硅材料,本文引入声子平均速度进一步简化热导率模型,其表示如下

(2)

从式(2)可以看出,通过近似之后,Holland模型的热导率与声子弛豫时间、材料尺寸与热容呈正比关系。考虑热传输的尺度效应,通过η(H/ι)系数修正声子弛豫时间,结合已有的体硅材料热导率模型,即可建立起微纳尺度硅热导率模型。Vasileska等对体硅材料热导率模型进行了深入的研究与探讨[19],结果表明在250~1 000 K宽温度范围内硅热导率的温度依赖关系可以表示为

(3)

式中:a=0.03;b=1.56×10-3K-1;c=1.65×10-6K-2。因此,立方晶体结构的微尺度单晶硅热导率模型可以简单方便的表示成体硅热导率与衰减因子的乘积形式,表达式如下

λ=λBulkη

(4)

纳米硅薄膜平面内尺寸要远大于垂直平面内厚度,揭示纳米硅薄膜传热机制是纳米全耗尽绝缘体上硅MOSFET自热效应研究的基础。硅薄膜厚度对声子散射的限制占据主导地位,热导率呈现出很强的厚度依赖关系。McGaughey等对厚度依赖的纳米硅薄膜热导率进行了深入的研究,提出基于体硅模型的纳米硅薄膜热导率的修正模型[20]。修正系数ηFM是硅薄膜厚度的函数,表示如下

(5)

式中:ξ=3kBvHFM/(2λBulkΩ)是无量纲长度,其中Ω是晶胞体积,HFM为硅薄膜厚度。此时,纳米硅薄膜热导率模型可以表示为λFM=λBulkηFM。

不同于纳米硅薄膜内声子散射机制,GAA SiNWs FET中声子散射同时受纳米线沟道截面高度与宽度等尺寸的限制,热导率在厚度限制的基础上将会进一步降低。为得到适用于修正硅纳米线热导率的修正系数(ηNW),本文通过求解Gray近似下的硅薄膜与硅纳米线热导率修正系数的关系,结合表达式(5)得到硅纳米线热导率的修正系数。在Gray近似下,硅薄膜热导率的修正系数如下

(6)

硅纳米线的热导率修正系数可表示为

(7)

式中:ιNW_FM为硅纳米线中声子平均声子自由程;HNW为硅纳米的高度;αFM与αNW为拟合参数,αFM=2αNW;ιFM_MFP与ιNW_MFP分别为硅薄膜与硅纳米线中平均声子自由程,可以表示如下

(8)

其中φ0为常数,当声子传播方向与边界平行时φ0=0。结合表达式(6)~(8),可得硅薄膜和硅纳米线中的热导率修正系数关系

(9)

因此,计入截面横向与纵向尺寸限制的硅纳米线热导率模型可利用纳米硅薄膜的修正系数得到,表示如下

(10)

3 结果与讨论

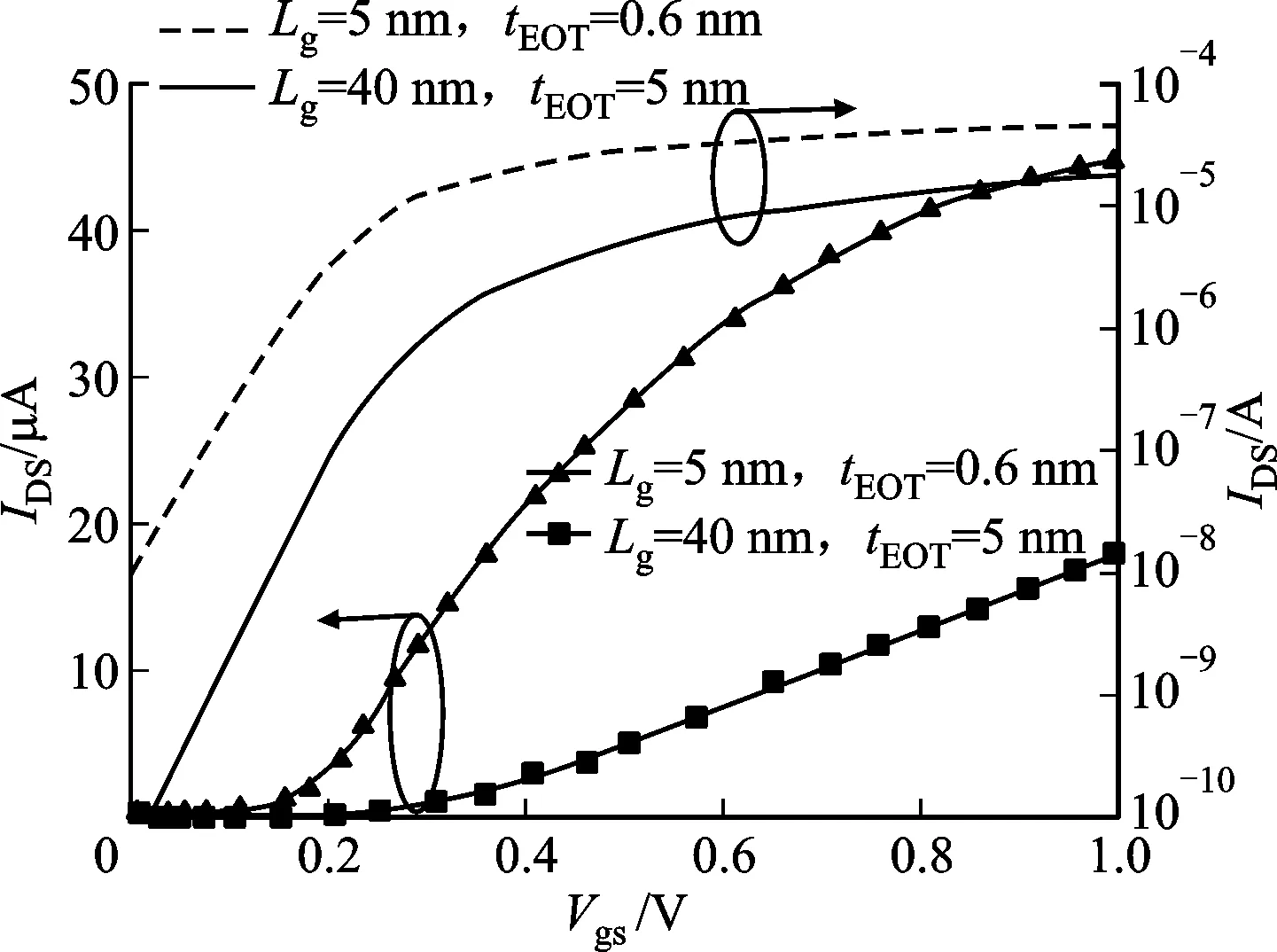

图2给出了量子效应修正模型下的特征尺寸为40 nm与5 nm的GAA SiNWs FET输出特性曲线。由图2可见,短栅与长栅器件都具有较好的性能,但是短沟道效应使得5 nm器件关态电流上升了2个数量级。40 nm器件的等效氧化层厚度(EOT,用符号tEOT表示)为5 nm,5 nm器件EOT为0.6 nm。本文为了更好地研究真空栅间隙对真空栅介质环栅纳米线场效应晶体管自热效应的影响,选用EOT更厚的40 nm器件作为本文的基准参考器件。

图2 5 nm与40 nm GAA SiNWs FETs器件输出特性曲线Fig2 Output characteristics of 5-nm and 40-nm GAA SiNWs FETs

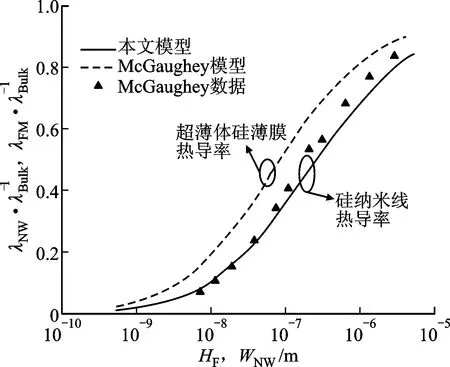

图3所示为纳米硅薄膜与硅纳米线热导率相对于薄膜厚度(用符号HF表示)与纳米线宽度的变化关系。McGaughey等在工作中只给出了硅薄膜热导率的解析模型[17],而对于硅纳米线只给出了数值解。从图3中可以看出,本文所提出的硅纳米线热导率解析模型与McGaughey所计算的数值模型结果吻合得很好。本文模型通过纳米尺度下弹道输运过程的硅纳米线与纳米硅薄膜之间的自由程近似关系得到硅纳米线热导率,当特征尺寸大于100 nm时,声子弹道输运过程将会减弱,模型中的弹道输运过程自由程的近似在大尺寸下将会产生一定的偏差。随着硅尺寸不断减小,硅热导率由于急剧增加的声子边界散射而不断的降低。同样是10 nm的尺寸,硅薄膜热导率将衰减至体硅材料的20%。硅纳米线由于声子散射同时受截面内两个维度尺寸的限制,热导率进一步降低至体硅材料的10%。可见,边界效应对硅纳米线内热传导有着重要的影响,要实现对GAA SiNWs FET自热效应的精确模拟分析,就需要在热电仿真中考虑器件边界对沟道热导率空间限制而产生的尺度效应。

图3 纳米硅薄膜与硅纳米线热导率随尺寸变化关系Fig.3 Relationships between nanoscale silicon film and SiNW thermal conductivities and size

图4 固态栅介质GAA SiNW FET漏端延伸区内沿Z轴方向的温度分布与热生成Fig.4 Temperature distribution and heat generation along the Z direction in drain extension region of solid gate dielectric GAA SiNW FET

图4所示为固态栅介质GAA SiNW FET漏端延伸区内沿Z轴方向的温度分布及热生成结果。GAA SiNWs FET中3根垂直堆叠纳米线沟道Ch1、Ch2、Ch3都存在与之对应的热生成尖峰,这意味着相比于FinFET等单沟道器件,GAA SiNWs FET有着多个等效热源。多个热源的热量积累分别在纳米线沟道中产生了3个温度极高的热点。可见,多热源将会导致GAA SiNWs FET有源区内产生的热量更容易积聚,使得热生成与扩散过程变得更加复杂。

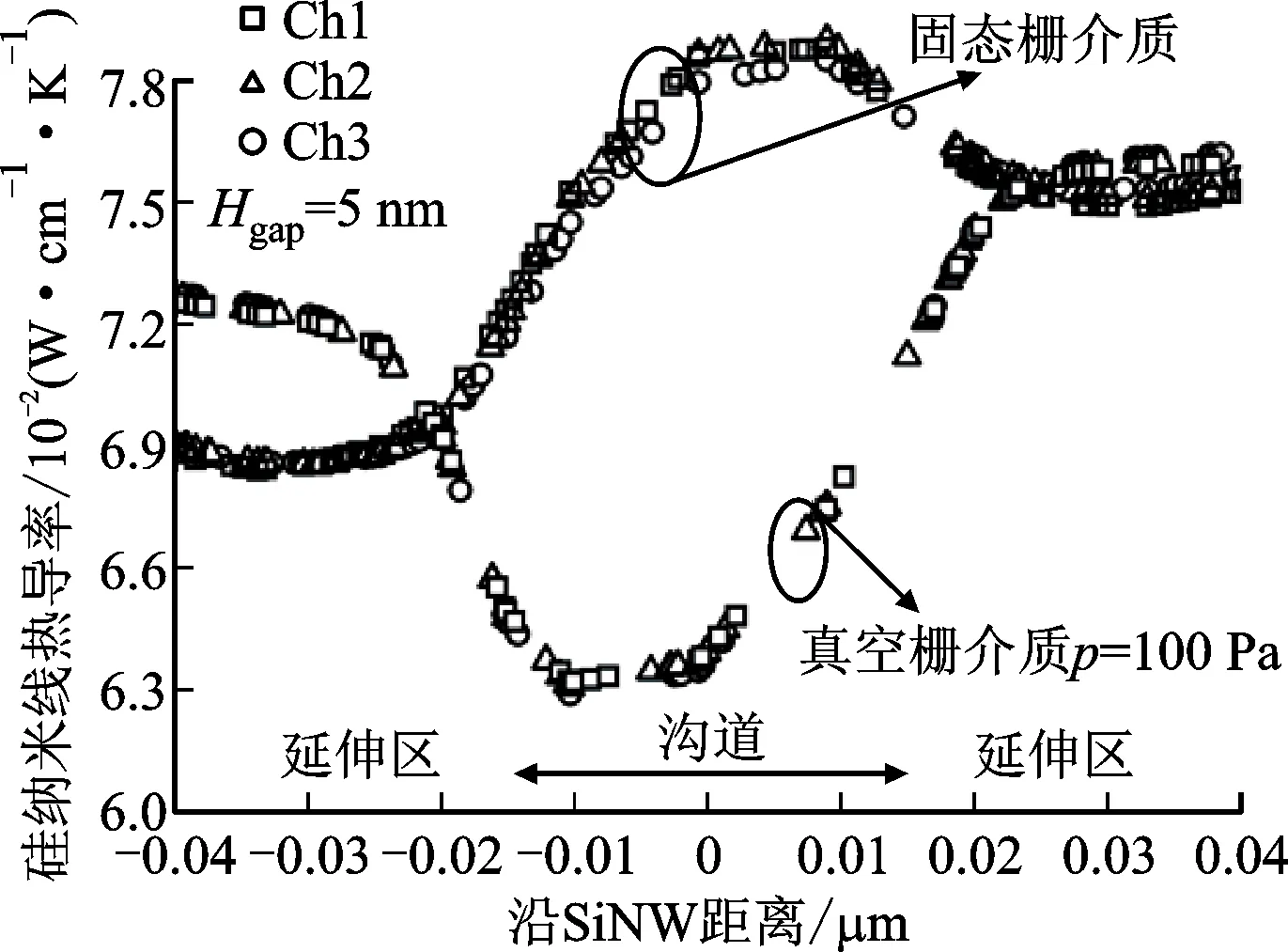

沿纳米线长度方向的热传输特性决定了GAA SiNWs FET对自热效应的抑制能力。图5给出了真空与固态栅介质GAA SiNWs FET纳米线沟道热导率沿长度方向的变化关系。从图5可知:热导率随空间位置的变化而变化;真空栅介质GAA SiNWs FET遭受着更加严重的自热效应,从而导致固态栅介质GAA SiNWs FET硅纳米线热导率在沟道区域整体比真空栅介质GAA SiNWs FET硅纳米线热导率要高。受到温度和尺寸的双重限制,沿沟道硅热导率将从体硅的145 W·m-1·K-1降低至8 W·m-1·K-1。纳米尺度下温度与尺寸效应对硅纳米线热导率的影响不可忽略,只有将热导率这种依赖关系完整的考虑进数值模拟分析才能够实现更高精度的纳米半导体器件自热效应分析预测。

图5 真空与固态栅介质GAA SiNWs FET纳米线沟道热导率分布Fig.5 Thermal conductivity distribution of SiNW for vacuum and solid gate dielectric GAA SiNW FETs

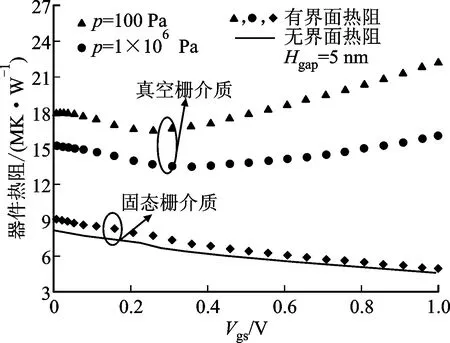

图6 真空栅介质气压和界面热阻对GAA SiNWs FET自热效应的影响Fig.6 Influences of gas pressure and interfacial thermal resistance on self-heating effect in GAA SiNWs FET

图6给出了栅介质种类、气体压强和界面热阻对GAA SiNWs FET自热效应的影响。图6结果表明,真空栅介质器件存在更为严重的自热效应,将真空栅介质替换成固态栅介质能够迅速地降低器件热阻,在考虑硅/二氧化硅界面热阻(ITR)后,固态栅介质GAA SiNWs FET的热阻在栅极和源极偏压Vgs为0时增加了25%,界面热阻的引入进一步恶化了器件的自热效应。随着Vgs继续增加,沿着纳米线横向扩散的热量占总热量的比重增加,弱化了界面热阻对器件的作用,最终使得有无界面热阻2种情况下的器件热阻趋于相同。真空栅介质的气体压强由102Pa增加到106Pa,在栅源偏压Vgs=1 V偏置时的真空栅介质器件热阻由2.2×107K·W-1下降至1.6×107K·W-1。这表明一定程度上增加气体压强,能够在不影响器件驱动能力的情况下抑制器件自热效应。因为增加气体压强将提升间隙内气体热导率,其表达式如下

(11)

式中:λp0为一个大气压下气体的热导率;ζ为氮气的能量调节系数;p表示气体压强;Hgap为栅氧化层间隙。纳米间隙内气体分子热传输是弹道热运输,因此,不仅压强会影响气体热导率,栅氧化层导热间隙对气体热导率的影响同样很大。

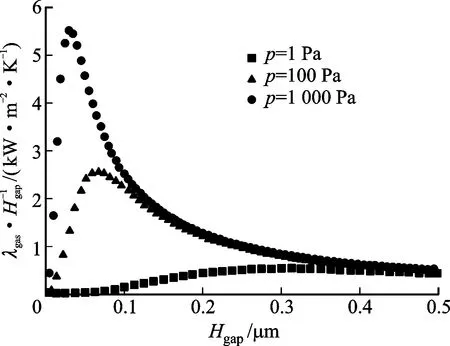

图7 不同气压下栅介质热导与导热间隙的关系Fig.7 Relationships between thermal conduction and gap in different gas pressure

图7所示为在不同气体压强下导热间隙对GAA SiNWs FET栅极热导的影响。图7表明:压强增加使得栅间隙内气体热导率增加,真空栅介质层热导随之上升;在气体压强不变的情况下,随着Hgap增加,真空栅介质的热导先增加后减小。这是由于Hgap的增加会增长热传输路径的同时,也会增加气体弹道输运的热导率,从而使得热导率不减反增。最大热导处栅氧化层厚度Hgap与气体压强相关,随着气压增加而不断减小。因此,为了能够更好的抑制器件自热效应,需要在器件的工作环境气压和栅介质层间隙之间折中考虑。最大化器件的散热能力,有助于提高器件性能与增强器件可靠性。

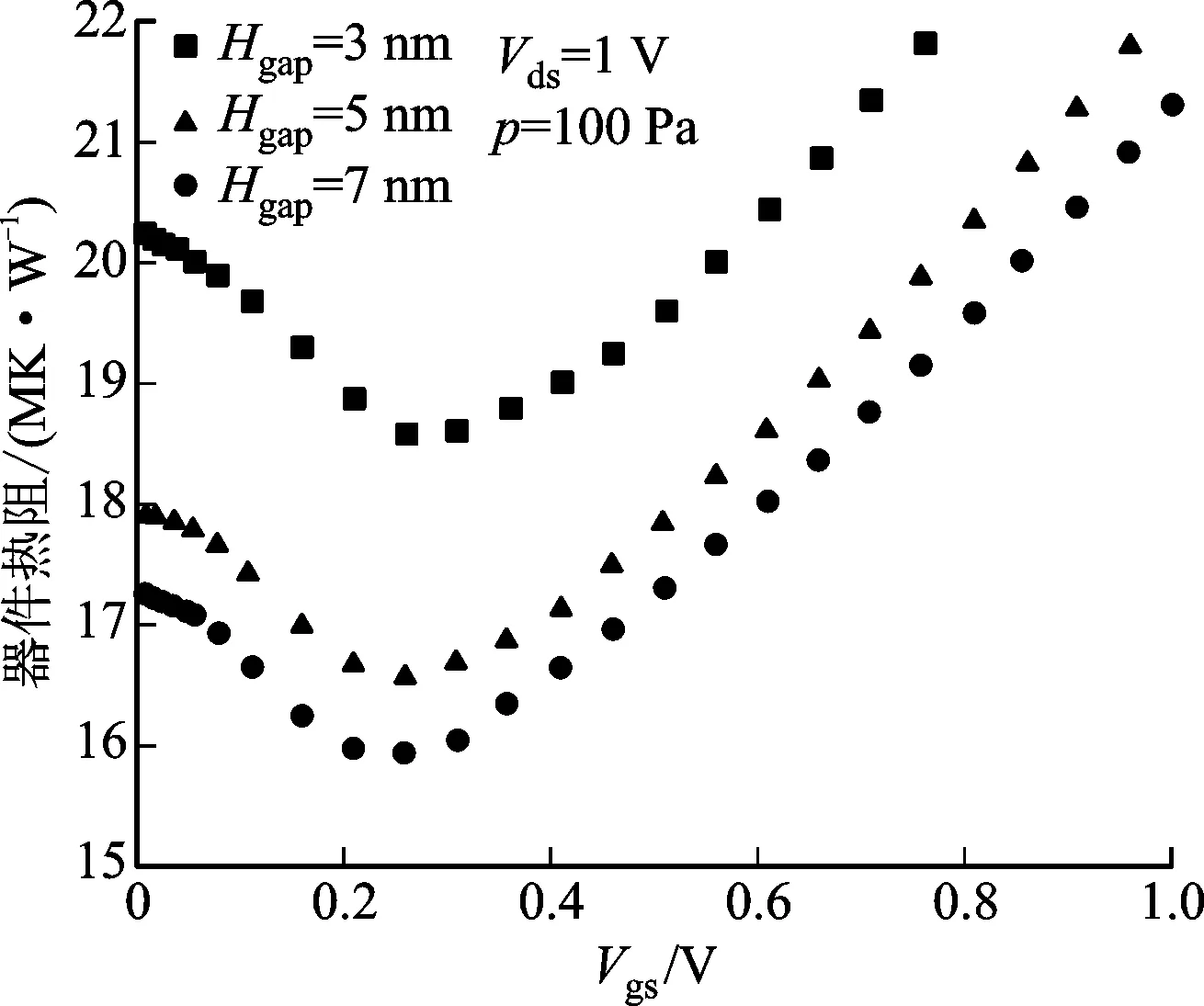

图8给出了导热间隙Hgap对GAA SiNWs FET整个器件热传导能力的影响。从图8可知:增加导热间隙Hgap,器件热阻减小,热传输能力增加;随着Vgs偏压由0上升到0.3 V左右,器件热阻随着偏压增加而减小。在低气压真空栅介质GAA SiNWs FET中,受栅介质的极低热导率的影响,热源产生的热量主要沿纳米线沟道向环境传输,纳米线热导率的大小决定了器件的热传输能力。这是由于:Vgs增加使得沟道内电子浓度增加,电-声子耦合增强了器件的散热能力,热阻从而减小;当栅压偏置进一步增加,GAA SiNWs FET的功率增加,温度急速上升,硅纳米线沟道的热导率迅速降低,导致器件热阻反而增加。结合图6可以更进一步证明,气体压强越高,栅氧层热导率越高,0.3 V之后热阻上升的趋势越小,在固体栅氧层中该趋势消失并反向减小。

图8 不同导热间隙下GAA SiNWs FET热阻随Vgs偏置的变化Fig.8 Variation of GAA SiNWs FET thermal resistance with Vgs in different thermal conduction gap

图9所示为栅、源和漏极接触热阻与器件热阻的关系。由图9可知:接触热阻增加使得GAA SiNWs FET中主要散热通道热阻增加,从而导致器件整体热阻增加;当栅接触热阻增加到一定程度时,由热源向栅接触的热扩散通道的热阻急剧增加并远大于热源-源极,热源-漏极和热源-衬底等三路散热路径的热阻。此时,器件的热阻由源、漏和衬底等通道的热阻决定。继续增加接触热阻,对器件的整体热阻的贡献将会很小,器件整体热阻保持不变。对比发现,增加栅极接触热阻导致器件热阻变化最快。从中可以推测出器件热源位置距栅极热接触最近,器件散热能力与栅接触热阻最为相关。因此,器件热设计工程师可以通过优化栅极热接触结构与材料来降低接触热阻,从而达到对GAA SiNWs FET器件自热效应抑制的效果。

图9 接触热阻与器件热阻的关系Fig.9 Relationship between contact thermal resistance and device thermal resistance

4 结 论

本文考虑硅纳米线截面高度与宽度同时对声子散射的限制,建立了温度与尺寸依赖的硅纳米线沟道热导率解析模型,能够有效评估GAA SiNWs FET中存在的自热效应。通过对比分析固态栅介质和真空栅介质对GAA SiNWs FET热传输能力的影响,发现真空栅介质器件由于受低热导率气体的影响遭受着更加严重的自热效应,器件内热源位置离栅极区域最近,对栅极材料与结构的热特性最为敏感。在器件设计时,可以通过折中考虑气体压强和栅极介质层间隙距离等参数,采用高热导率栅材料和设计大面积栅等方法最大化真空栅介质GAA SiNWs FET散热能力,以达到有效抑制器件自热效应的目的。