更低功耗、更高带宽!LPDDR内存的过去和现在

2021-06-20李实

李实

内存芯片的重要性在今天愈发凸显,无论是PC还是手机、平板还是游戏主机,都无处不闪现着内存芯片的身影。不过,不同产品使用的内存往往存在一差异。除了我们常见的DDR、GDDR外,在移动设备上还存在着一种专用的低功耗内存,那就是LPDD。今天,本文就和你一起走近LPDDR内存,探寻这种专门面向低功耗市场的内存的过去、现在和未来。

LPDDR是目前广泛使用在移动设备和低功耗设备上的内存产品。LPDDR的全称是Low-Power DDRSDRAM,中文名称是低功耗双倍数据速率同步动态随机存取存储器。在一些文章中,LPDDR也被称为mDDR也就是移动DDR,“m”的意思是“mobile”,这是针对其应用市场所提出的名称。相比常见的DDR内存,LPDDR的特点是“LP”,也就是低功耗。因此它被广泛使用在包括手机、平板电脑、低功耗设备等对功耗比较敏感的场合。除了功耗外,LPDDR相比DDR,还在芯片面积、位宽、电压、频率、预取值、总线设置等方面作出了一系列的适应性改善,以便更符合低功耗设备的应用需求。

回望历史:LPDDR从第一代到第三代

从初代LPDDR算起的话,LPDDR产品发展到今天,经历了LPDDR、LPDDR2、LPDDR3、LPDDR4、LPDDR4X以及LPDDR5等多代次。其中,真正的巨变发生在LPDDR4时代,也正是从这个世代开始,LPDDR开始和DDR逐渐分道扬镳,走上了独立发展的道路。

LPDDR:脱胎于DDR,面向功耗敏感市场

在移动计算设备刚兴起的时候,人们意识到用于桌面的DDR内存在移动设备上使用时存在很多问题,包括过大的芯片面积,较高的电压导致较高的功耗等。因此,三星、美光、英特尔、英伟达等厂商联合起来推出了一种新的内存技术规范,这种内存电压更低,仅为1.8V,相比之下DDR内存的电压高达2.5V。此外,这种新的内存技术规范的面积相对更小一些,更适合在“寸土寸金”的移动设备内部使用。技术方面,考虑到移动设备对能耗的敏感程度,因此新的产品加入了一些节能特性,比如深度睡眠模式(DeepPower Down Mode,用于休眠状态大幅度降低功耗),可配置的自刷新以及温度补偿自刷新(减少刷新次数从而降低功耗)等,使得新产品在功耗上相对DDR有比较大幅度的下降。此外,数据位宽方面,传统的DDR的數据位宽是64bit,而考虑到当时移动设备的计算能力较弱,过大的数据总线带宽没有意义且占据太多的布线面积,因此这种新的存储产品将10界面的位宽缩减至32bit(厂商可以根据需要配置16bit甚至8bit使用),这也在很大程度上降低了产品的功耗。

在拥有了新的低电压、小尺寸和新的节能技术加持后,为了和传统的DDR区分开来,这种新的存储颗粒被人们称之为LPDDR或者mDDR。不过,LPDDR在早期并没有统一的规范,首批使用LPDDR内存的移动产品包括大名鼎鼎的iPhone3系列手机、三星Galaxy系列手机和平板电脑等。

在产品型号方面,初代LPDDR包含了LPDDR 400和LPDDR 533(后者也被称为LPDDRe,e是“enhance”也就是“增强”的意思)两种产品,由于基本规范脱胎于DDR,LPDDR的预取值也是2n,内部时钟频率为200MHz-266MHz,10频率同为200MHz-266MHz,数据传输速率为400MT/s-533MT/s,在32bit线下的数据带宽可达1.6GB/s-2.1GB/s,也能完全满足当时移动设备对带宽的需求。

新的LPDDR带来了一个全新的市场,并且这个市场获得了快速发展。为了规范产品和市场行为,JEDEC也在2008年底推出了针对LPDDR的规范JESD209B。在此之后,LPDDR被JEDEC纳入标准统一管理中,从而成为业界的统一标准。

LPDDR2:崭露头角,拓展规格

LPDDR的成功不是没有原因的,移动计算时代的大潮汹涌而来。在这种情况下,JEDEC也加紧努力,“规范走在产品前”的思想开始指导LPDDR2的发展。JEDEC在2009年4月就推出了全新的LPDDR2规范JESD209-2F。新的规范扩大了LPDDR2的产品范围,将非易失性内存纳入其中,并且还带来了更高的内存密度、更好的性能、更进一步缩小的封装尺寸以及大量降低功耗的技术。

根据规范内容,LPDDR2实际上分为LPDDR2-S2、LPDDR2-S4以及LPDDR2-N三种产品。其中前两种都是传统的易失性存储设备,最后一种LPDDR2-N是非易失性存储设备,这种存储芯片往往会被使用在特殊场合,比如一些执行单一功能,任务量和计算量都比较小的物联网设备、工业设备中,比如智能电表、工业计算机等。对一般用户来说,重点还是易失性存储器。

对于LPDDR2-S2、LPDDR2-S4而言,其最大的差别在于前者使用2n预取,后者使用4n预取。其中前者在市场上并不多见,主要用于和LPDDR过渡的一些场合,后者才是LPDDR2的主力军。相比之前的LPDDR,LPDDR2的电压再度大幅度降低至1.2V,节能效果更为出色。另外,所有LPDDR2器件都在命令,地址(CA)总线上使用DDR架构,并采用了lObit位宽(前代LPDDR采用的19bit SDR总线,一次只能在单一方向传输数据),这条总线包含了命令、地址和存储区,行缓冲区信息,这样设计使得内部总线复杂性降低并带来了一些能耗的减少。在特色功能方面,LPDDR2带来了新的低电平操作,使得LPDDR2芯片可以根据情况进入活动、空闲、自刷新或者深度睡眠状态,LPDDR2能结合实际情况选择它的运行状态,更有利于节约功耗。

在产品型号方面,LPDDR2带来了LPDDR2 800和LPDDR2 1066(后者被称为LPDDR2e)两种规格,当然,这个数据是针对LPDDR2-S4而言。因为预取值提升至4n,所以LPDDR2 800和LPDDR2 1066的实际内部时钟频率、10频率等相比之前的LPDDR都没有变化,均运行在200MHz和266MHz的频率上。相应地,LPDDR2的数据传输速率就提升至800M T/s和1066M T/s,在32bit(可选16bit方案,带宽减半)下的带宽也提升至3.2GB/s和4.2G B/s,相比上代LPDDR翻倍。

LPDDR2的寿命周期比较长。从2009年提出规范开始,直到2012年5月,替代LPDDR2的LPDDR3规范才开始提出。考虑到规范发布后一般半年后才有产品推出,LPDDR2的真正产品寿命周期差不多大约接近4年。

LPDDR3:全面改善,提高速度

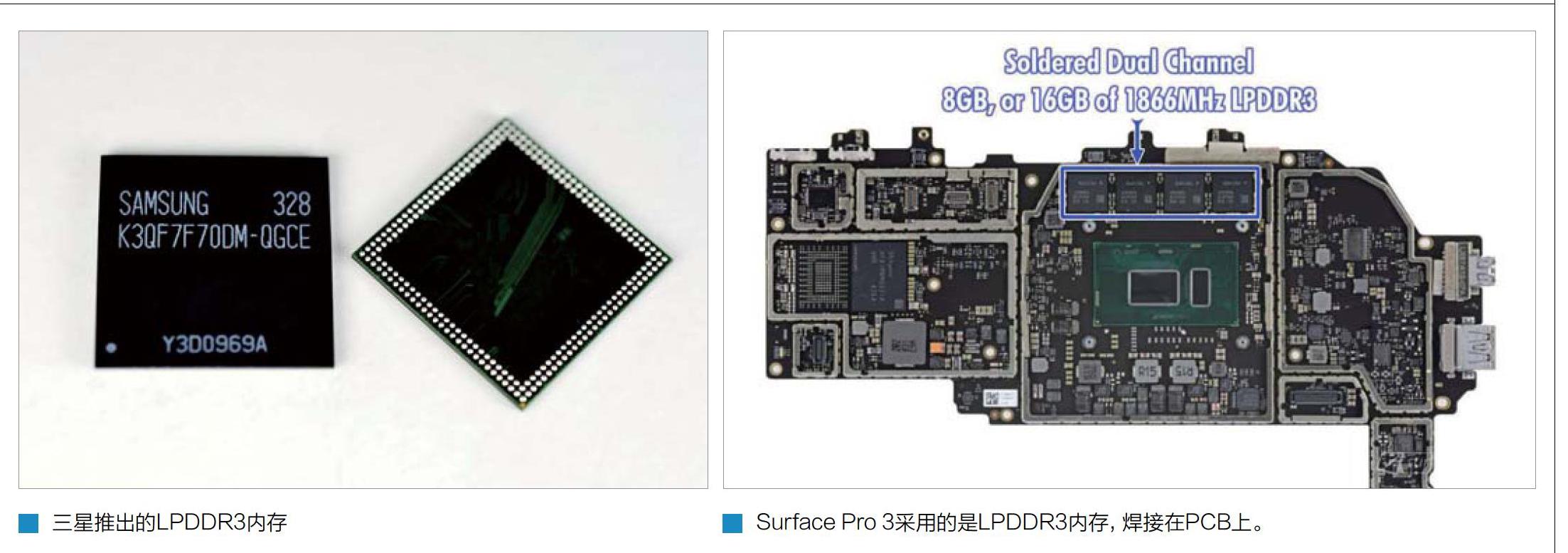

201 2年5月,JEDEC发布了LPDDR3规范,白皮书代码是JESD209-3。相比之前的LPDDR2,LPDDR3将改善的重点放在了数据传输速率和带宽方面,同时在保留LPDDR2功耗控制功能的情况下还做出了一些优化。另外,在封装方面,LPDDR3开始支持POP封装或者离散型封装,其中前者非常重要,POP堆叠类型的封装为进一步减小移动设备内部的面积打下了基础。

LPDDR3出现的背景是移动计算设备使用的SoC性能提升速度较快,在LPDDR2难以满足的情况下需要新的规格来加强数据传输带宽。因此LPDDR3将数据预取值翻倍至8n,可以在和LPDDR27相同的内部时钟频率的情况下使得数据传输带宽翻倍。值得一提的是,LPDDR3规格中并不包含针对非易失性存储设备的规格,考虑到这类设备多用于工业或者物联网产品,在当时也的确没有太强的性能需求。

LPDDR3首先推出的标准是LPDDR3 1600,DRAM的内部时钟频率为200MHz,但是8n预取的设计使其数据传输速率高达1600MT/s,在32bit配置下(可选16bit方案,带宽减半)带宽可达6.4GB/s,基本和同期桌面DDR产品在可比条件下相当。另外,LPDDR3后期还推出了增强版的LPDDR3e,内部时钟频率提升至266MHz,数据传输速率高达2133MT/s,带宽也在32bit配置下(可选16bit方案,带宽减半)提升至8.5GB/s,基本达到了之前LPDDR2的2倍以上。LPDDR3搭配的产品非常多,包括著名的苹果iPhone 5s、Macbook Air、三星Nexus 10以及微软的Surface Pr03。后期高通推出的骁龙800和骁龙600也都提供了对LPDDR3的支持。

虽然LPDDR3的速率更高,但是其在架构设计上还是延续了之前LPDDR2的那一套。考虑到移动计算发展速度越来越快,内存也需要加入更多的特性,尤其是针对移动设备进行一些改变,因此在LPDDR3发布之前的2012年3月,JDEDC就召开会议讨论下一代LPDDR内存的发展,三星等厂商在2012年1 2月30日就推出了新一代LPDDR产品的样品,其速度高达3200MT/s,并且在能耗方面有更出色的表现。随后,在经过长达一年多的协调和技术验证后,LPDDR4规范在2014年8月正式发布,LPDDR3时代宣告落幕,LPDDR进入了全新发展周期。

LPDDR4:全新架构,为移动计算打牢基础

夸张一点来说的话,LPDDR3和之前的LPDDR产品都可以看作桌面DDR内存的变种,只是加入了诸如节能、降耗、缩小面积等特性来满足移动设备的需求。而随着移动计算进一步发展,LPDDR3这样继续根据之前的技术路线改进的发展方式开始无法满足市场需求了,尤其是在高清视频、高清摄影等功能逐渐成熟后,移动设备对内存带宽提出了极高的要求,这是之前LPDDR3以及其相关架构难以做到的。因此,JEDEC需要一种全新架构的产品来满足移动计算的需求并继续在能耗和带宽方面进行平衡。

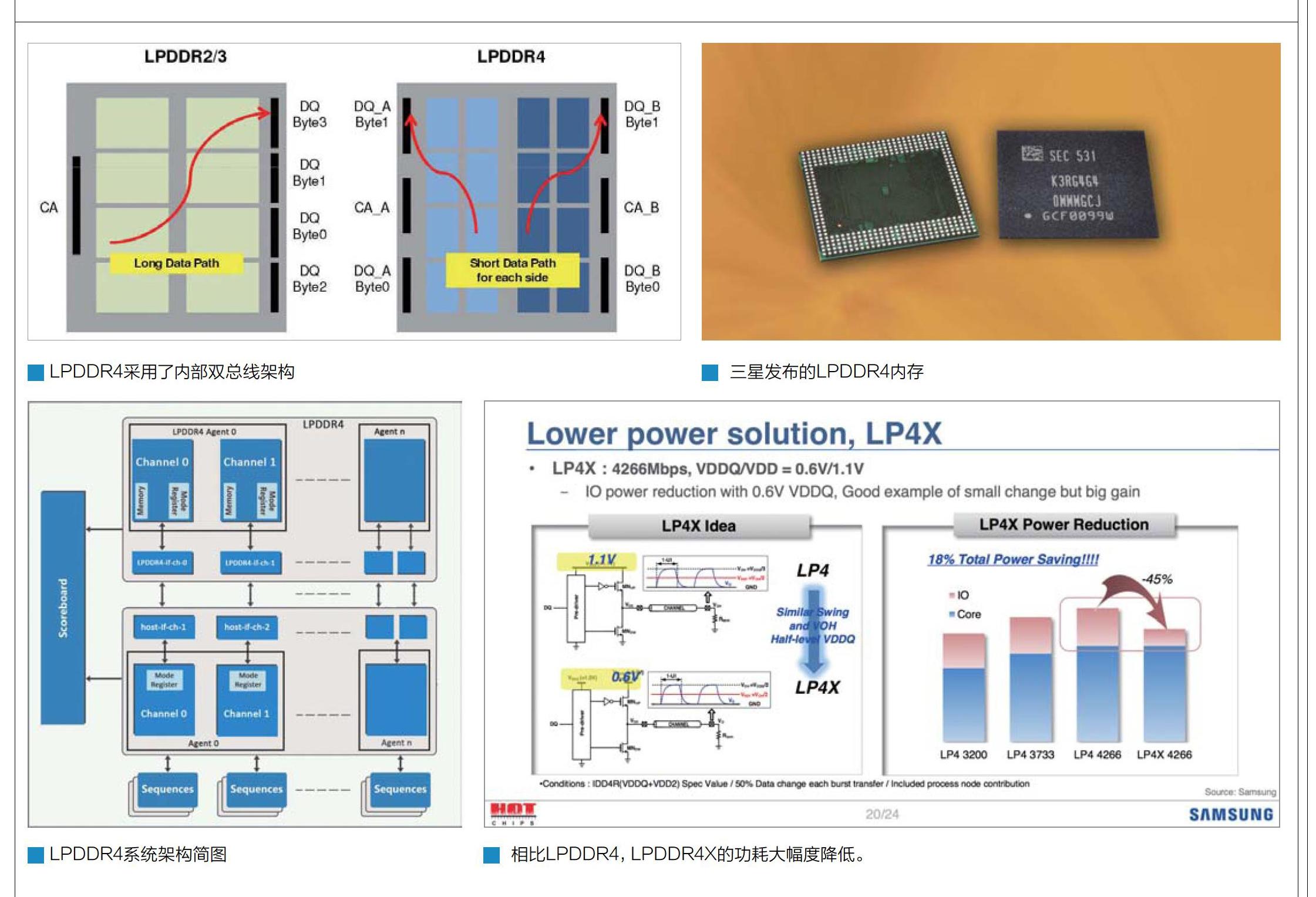

这就是LPDDR4。新的规范在2014年8月发布,其实际产品早在2012年底就出现在各种演示上了。相比LPDDR3,LPDDR4带来了几大改进。首先是工作最低电压从之前的1.2v进一步降低至l.lv,不断降低电压带来了能耗减少。其次,LPDDR4改用了16n预取值,通过预取值翻倍,LPDDR4可以在不继续提升内部时钟频率的情况下提高带宽。第三,LPDDR4的内部总线从之前的32bit改为2个16bit,总带宽依旧是32bit,这样改进使得内部数据存取效率大幅度提升,并在一定程度上降低了存储部分的功耗。除了上述三种重要改进外,LPDDR4的CA总线从之前的10位DDR命令(继承自LPDDR2时代)改为6bit的SDR总线,但是加入了多周期命令功能,由于新的总线只在数据传输的上沿或者下沿传输信息且位宽更窄,能耗更低,其他的一些改进还包括通过专用的命令启动自刷新,封装尺寸进一步缩小、数据密度提升等。

由于大幅度更新了内部架构,因此LPDDR4整体效能表现更为出色。业内的例证显示,和基于4GbLPDDR3的2GB内存相比,采用8Gb的LPDDR4颗粒的2GB内存在功耗方面降低了40%。在产品方面,LPDDR4带来了LPDDR4 3200这样的规格,其内部时钟频率为200MHz,10速度为1600MHz(注意2個16bit总线),但是数据传输速率来到了3200MT/s,因此最终在32bit的位宽下,LPDDR4 3200的带宽达到了12.8GB/s的水平。

LPDDR4之后,在三星的倡议下,JEDEC又在201 7年3月发布了JESD209-4-1规范,确定了新的LPDDR4X。LPDDR4X是LPDDR4的技术扩展版本,和之前的“e”增强版本有所不同的是,LPDDR4X除了在频率、性能上有所加强外,还带来了进一步的功耗节省设计。在新的规范中,LPDDR4X IO部分的电压从l.lv降低至0.6V,数据存储部分的电压维持不变。

对LPDDR家族的产品来说,其频率分为两个部分,分别是数据存储部分频率和10频率。继续细分的话,数据存储部分频率可以分为内部时钟频率和内部物理频率。在本文的描述中,大家可以清楚地看到LPDDR的内部时钟频率始终不会超过266MHz,一般只有200MHz和266MHz这2个规格。对于内部物理频率而言,考虑DDR带来的内部时钟频率倍数的话,那么实际上LPDDR内存的数据存储部分一直都在100MHz和133MHz两个频率上运行。对内存这种产品而言,其频率并不会太高,较低的频率有助于确保内存在低电压下运行时的稳定性和可靠性,同时低电压又带来了能耗降低。虽然内部时钟频率和内部物理频率一直没有提升,但通过预取值不断翻倍又翻倍,比如从2n到4n、8n再到16n-LPDDR4的预取值是LPDDR的8倍,LPDDR的数据传输速率一直在提升。比如内部时钟频率都为200MHz,LPDDR4 3200的数据传输速率达到了3200MT/s,相对应的在LPDDR 400上则只有400MT/s。

那么这和10频率又有什么关系呢?由于10部分承担的是LPDDR内存对外的数据传输,在预取值提升后,10频率就不得不进一步提升以跟上越来越大的数据吞吐量。从LPDDR到LPDDR4,10频率从200MHz一路提升至1600MHz。高频率运作下的10部分带来了较高性能的同时,也产生了比较高的功耗。因此,在LPDDR4X上,三星率先提议将10电压降低至0.6v,这带来了总线和IO部分功耗的显著降低。因此,新的LPDDR4X功耗得以进一步降低,性能得到了同步提升。

LPDDR4X还带来了新的LPDDR4X 4266型号,其内部时钟频率提升至266MHz,预取值还是16n,双总线方案,数据传输速率达到了4266MT/s,在32bit位宽配置下带宽达到了17G B/s,进一步提高了低功耗设备在存储方面的性能。

不过,虽然LPDDR4X在内核改进方面和LPDDR4相比非常微小,但是LPDDR4X和之前所有代次的LPDDR内存一样,都无法实现向后兼容,这是因为LPDDR4较高的电压会导致LPDDR4X的10部分无法正常工作,不过和桌面内存有所不同的是,LPDDR4X这样的产品主要用于OEM厂商制造使用,用户几乎不存在更换的机会,因此也不会带来额外的兼容性问题。

由于LPDDR4X带来了功耗的降低和性能的提高,因此在移动设备中大获成功,大量高端手机、平板甚至笔记本电脑都采用LPDDR4X作为内存使用,LPDDR内存迎来了其发展的黄金时刻。

LPDDR5:带宽翻倍,比拼高端桌面平台

在LPDDR4X带来了辉煌后,LPDDR5也开始紧锣密鼓地准备了。2019年,JEDEC发布了JESD209-5规范,正式带来了LPDDR5标准。

从架构角度来看,LPDDR5保留了LPDDR4时代使用的16n预取值,但是加入了在桌面DDR4上使用的区块组( Bank Group)概念。简单来说,之前的LPDDR内存如果内部有8个或者16个区块的话,那么它们是以串行的方式来读写的,O号区块读写完成后再去读写1号区块、2号区块,以此类推。但是在区块组概念出现后,一个内存中会根据情况被划分为2个或者4个或者更多的区块组,数据并行进入每个区块组进行读取操作。这相当于在内存的内部实现了并行存取。因此LPDDR5才可以在不提高预取值和频率的情况下,仅仅依靠区块组和10部分的频率提升来大幅度提升数据带宽。

除了引入区块组的概念外,LPDDR5还带来了包括新的可扩展时钟架构,解决了CA总线的速度无法跟上数据总线速度提升的问题。新的设计使得CA总线可以有条件以数据总线1/4或者1/2的速度运行,这使得CA总线的稳定性和可靠性都得到了提升。另外,LPDDR5还加入了决策反馈均衡器(DFE),减少了对

为什么DDR4还比LPDDR4“慢”

本文的介绍凸显了LPDDR4的优势,那么既然LPDDR这么好,为什么不引入桌面平台呢?实际上这个问题的答案也是明确的。我们以目前主流的LPDDR4和DDR4作为对比解释—下。

先来看看DDR4内存的基本规格。目前DDR4并没有采用16n预取值,而是依旧采用了8n预取值,但是其实际运行的物理频率从200MHz起跳,直到更高的400MHz、533MHz等,同时还加入了区块组的概念。可以说,DDR4和LPDDR4在架构设计上是完全不同的两个产物,它们基本上没有任何技术上的关联。同时,DDR4具备了桌面内存所有的特性,比如64bit位宽、更大的容量、更高的电压和相对较低的延迟值。

这样来看相比LPDDR4,首先要明确的是DDR4内存的位宽更大,单条内存能够实现的带宽更高。目前所有主流DDR DIMM内存的位宽都是64bit,搭配桌面级别CPU的128bit通道,2根DDR4 4266规格的内存就可以实现4266MT/sx64bitx2/8=68.3G Bls。相比之下,即使是LPDDR4X 4266这样的LPDDR4家族的顶级型号,其位宽仅为32bit,单个LPDDR4X 4266的带宽数值是4266MT/sx32bit/8=17GB/s。如果搭配桌面CPU的话,需要4个内存通道才能完全匹配,虽然最终总带宽也可以达到和桌面CPU相同的水平,但是更多通道带来了更复杂的主板设计、内存控制器设计以及使用上的麻烦,显然是不合算的。

其次,虽然移动平台的LPDDR通过降低电压等手段实现了低功耗,但是世上没有免费的午餐,LPDDR的低功耗也需要付出代价,那就是较高的延迟值。举例来说,LPDDR3 2133的延迟值一般在lOOns左右,即使是延迟更高、近似规格的DDR4内存,其延迟值也只有大约70ns,低了一大截,如果選择DDR3做比较的话,延迟值还会更低。对于这种情况,一篇名为《A Performance&PowerComparison of Modern High-Speed DRAM Architectures》的论文专门作出了研究。在仿真结果下,以带宽完全相同的DDR4和LPDDR4作对比的话,DDR4的每周期指令数要比LPDDR4高6%,延迟值显著更低。对现代高频率CPU来说,尤其是桌面CPU频率接近5GHz的情况下,更高的延迟值将会严重影响CPU的性能发挥。

因此,一般情况下,同代LPDDR内存是要弱于同时代的DDR内存的,其核心原因就是它的带宽更低、延迟值更高。目前,LPDDR内存在PC中的应用仅限于超便携、超轻薄或者对续航有要求的设备,也并非以性能作为主要方向。接收数据的符号间干扰(ISI),从而提高了接收数据的余量。此外,LPDDR5还带来了包括链路ECC校验、增加至3个FSP等设计,这些设计都在很大程度上增强了LPDDR5在高数据传输速率下的稳定性。

在功耗和电压方面,LPDDR5目前支持多组低电压设置。在较高的频率下运行时,LPDDR5支持1.05V的核心电压和0.5v的10电压,在较低频率下运行时,这两个电压数值会分别降至0.9V、0.3V,以进一步节约能源降低能耗。相比LPDDR4,LPDDR5的低电压带来了显著的功耗降低。另外,LPDDR5还带来了更新版本的深度睡眠模式,新模式相比旧模式能带来更低的闲置功耗,三星给出的数据是LPDDR5的深度睡眠模式消耗的功耗是LPDDR4X的一半,值得期待。总的来看,三星的评估数据是LPDDR5的功耗相比LPDDR4X大约降低了20%,这个成绩也相当不错了。

产品规格方面,目前LPDDR5推出的产品主要是LPDDR5 5500,但是JEDEC宣称LPDDR5最终将运行在LPDDR5 6400的速率上,在相同位宽配置下,其性能是LPDDR4 3200的2倍。举例来说,在32b.t的位宽配置下(需要2个16bit的LPDDR5组成双通道),LPDDR5 6400能带来高达25.6G B/s的带宽,如果是LPDDR55500的话,这个数据22G B/s,相比位宽为32bit的LPDDR4X,LPDDR5带宽至少提升了29%,最多可以提升49%。

值得注意的是,正如上段提到的,目前推出的LPDDR5内存的位宽都只有16bit,这一点和之前的LPDDR4家族以及LPDDR3等产品是不同的,前代产品的位宽最高可配置为32bit。LPDDR5减少位宽的原因可能是考虑到其本身即使是现在的较低规格版本,在16bit下带宽就超过10GB/s( 5500MT/sx16bit/8=11GB/s),对很多设备来说这个带宽已经足够了,因此降低位宽可以增加LPDDR5的市场适用范围。针对高端SoC来说,即使LPDDR5采用了16bit位宽设计,还可以采用多通道技术来实现带宽翻倍,这也不是太难的操作。

在LPDDR5的产品量产方面,目前三星和美光两家厂商是推动的主力,国内合肥长鑫也计划在2022年之前推出LPDDR5内存。具体来说,三星之前宣布将旗下EUV光刻机用于D1z DRAM的大规模量产,其最重要的产品就是LPDDR5内存。目前三星推出了两代LPDDR5內存,其中一代采用DUV制造,工艺节点代号为Dly,新的一代就是前文所说的D1z。在改用EUV制造后,三星显著提高了芯片的存储密度并缩小了面积。Dly工艺节点的LPDDR5芯片容量可选8Gb和12Gb两种,但是D1z就进化至12Gb和16Gb了。在面积方面,同为12Gb的颗粒,Dly产品的面积为53.53平方毫米,D1z仅为43.98平方毫米,工艺进步的效果显著。美光方面也计划在近期推出采用EUV技术的16Gb LPDDR5内存,不过相比三星的产品,美光的芯片面积略微大了一些,16Gb的LPDDR5面积为68.34平方毫米,相对应的三星的产品只有61.20平方毫米。

更加节能、更加高速:LPDDR的未来

从本文的介绍可以看出,LPDDR在发展过程中,从脱胎于DDR到走上独立发展的路线,以及现在LPDDR5的带宽逐渐赶上桌面平台,同时功耗又在不断降低,堪称走出了一条高性能、低功耗的独立之路。对于移动设备和低功耗设备来说,LPDDR的高带宽和低功耗特性是非常令人满意的。未来LPDDR内存还将在这条道路上继续发展,给我们带来更多轻便、节能但是高速的产品。