HEVC中率失真优化算法的动态可重构实现*

2021-03-01谢晓燕邓军勇刘新闯胡传瞻

杨 坤,蒋 林,谢晓燕,邓军勇,刘新闯,胡传瞻

(1.西安邮电大学电子工程学院,陕西 西安 710121;2.西安科技大学集成电路实验室,陕西 西安 710054;3.西安邮电大学计算机学院,陕西 西安 710121)

1 引言

与H.264/AVC编码技术相比,HEVC(High Efficiency Video Coding)帧内预测模式由原有的9种增加到35种,即DC 模式(模式0)、Planar模式(模式1)和33种角度预测模式(模式2~模式35)。率失真优化算法作为帧内预测模式选择的判别依据,每一次模式选择都涉及一个完整的编码过程,是帧内编码过程中最复杂的算法之一[1]。针对如此高复杂度的计算,仅仅从算法角度进行优化无法满足实时视频编码的需求,所以国内外学者已经开始把视频算法向专用硬件上转移[2],通过硬件实现率失真优化算法已经成为一种趋势。

使用专用硬件进行率失真优化算法的实现方式主要有2种:针对特定规模和针对固定大小编码块的硬件设计。针对特定规模的硬件设计虽然能满足算法实现的需要,但是结构固定,不能根据处理速度的需求改变硬件实现的规模。文献[3]提出一种支持8路并行的率失真优化实现方法,可同时进行8种预测模式的计算,在减少计算时间的同时增加了硬件资源的消耗;文献[4]设计了一种支持3路并行的率失真优化结构,虽然减少了资源消耗,但每次只能进行3种模式的并行计算,若选择模式增加,计算时间会大幅增加。针对固定大小预测块的实现方法虽然能减少硬件的资源消耗,但固定块大小的预测方式降低了编码压缩效率,文献[5-7]均设计了一种支持4×4大小预测块的率失真优化算法的硬件结构,虽然减少了资源消耗,提升了计算精度,但该设计对于平坦图像的计算量增加,且仅针对4×4大小的预测块。文献[8-10]所设计的硬件结构虽然支持不同大小的预测块、预测模式齐全的率失真优化算法,但硬件实现过于复杂,资源消耗大。通过专用硬件实现率失真优化算法,虽然提升了性能,减少了算法的执行时间,但资源消耗过多,灵活性较差,难以针对不同的应用需求进行灵活切换。可重构阵列处理器能够根据不同视频图像处理需求,灵活配置处理元逻辑功能和处理元之间的连接方式,既具有一定的灵活性,又具有计算的高效性。

因此,本文基于项目组前期研究的视频阵列处理器,提出一种动态可重构的率失真优化实现方法,将不同配置的率失真优化算法初始化在可重构阵列的指令存储中,基于上下文切换的重构机制及指令下发网络,实现不同规模、不同大小预测块的率失真优化算法之间的动态重构,并且可以根据计算时间和视频质量的不同需求,对阵列结构的规模和执行模式进行重新调度。

2 率失真优化算法分析

率失真优化算法的关键研究内容是如何得到编码码率和编码失真,传统的率失真优化算法中,要想得到失真和码率需要经过一系列复杂操作[11],编码复杂、计算量大,如图1所示。HEVC使用哈达玛变换来计算率失真代价,这一率失真优化算法为:

J=SATD(s,p)+λmodeRmode

(1)

其中,SATD(s,p)为经过帧内预测后得到的残差块的SATD,s表示原始像素值,p表示预测像素值,Rmode是编码当前模式所需要的比特数,λmode是拉格朗日因子。SATD是指将残差信号进行哈达玛变换后再求各元素绝对值之和。

Figure 1 Block diagram of rate distortion optimization algorithm

HEVC采用递归分割四叉树的方法将编码树单元CTU(Coding Tree Unit)分割成不同大小的编码单元CU(Coding Unit)、预测单元PU(Prediction Unit)和变换单元TU(Transform Unit)。这种划分方式虽然提高了率失真优化算法对最优模式选择的准确性,但针对不同大小的预测块进行计算时,需要重复遍历35种预测模式,大大增加了从最小块到最大块递归计算的复杂度。

而可重构阵列处理器结合了专用硬件的计算性能和通用处理器的灵活性,能够根据当前视频序列的特点,动态配置所需要的硬件结构,率失真优化算法的可重构实现既能保证算法的灵活切换,又能减少硬件资源的消耗。因此,在可重构阵列处理器上实现率失真优化算法是解决计算复杂的一种有效方法。

3 率失真优化算法的动态可重构实现

3.1 动态重构机制

为了满足率失真优化算法灵活切换的需求,使用可重构视频阵列处理器来进行算法的映射实现[12]。全局控制器为可重构机制的核心部分,其上层为主机接口,下层为多个处理元簇PEG(Process Element Group)组成的阵列处理器,每个PEG包含 16个处理元PE(Process Element)。当处理器资源有限却有多个算法需要进行映射时,为了减少硬件资源消耗,将不同配置的算法指令初始化在同一PE不同的指令存储中,如图2所示。这种基于上下文切换的重构机制能够根据用户需求在多个算法之间进行切换,最终使用户能够管理和控制资源。

Figure 2 Structure of context switched array processor

全局控制器通过在主机接口和阵列处理器之间形成一个H型的层次化的编程网络,在确保每一条指令都能同时到达PE的同时,实现对阵列资源的控制和管理。当主机接口对阵列处理器进行访问时,全局控制器收到来自主机接口的总线信息,总线信息包含地址位信息、标志位信息和指令信息。其中标志位信息用于判断执行数据反馈、指令下发还是配置调用;地址位信息完成每一个PE的地址划分,保证不同的PE对应不同的地址;指令信息用来决定PE所执行的指令。通过地址信息、标志信息和指令信息共同决定每个PE在某时刻所执行的特定指令。基于上下文切换的重构机制,将不同配置的率失真优化算法指令初始化在同一PE不同的指令存储中,通过配置调用、指令反馈和指令下发操作来实现率失真优化算法在视频阵列处理器上的动态重构。

3.2 率失真优化算法的并行化设计

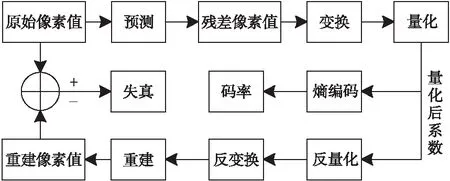

由于在进行率失真优化算法的计算过程中,不同预测模式之间相互独立,因此可以通过并行计算来减少算法的计算时间。本文提出的基于可重构阵列的率失真优化实现方法,采用4条路径和8条路径并行的方式,进行帧内预测模式选择的率失真优化算法的并行映射。图3为4条路径并行的率失真优化算法的映射图。

Figure 3 Mapping map of rate distortion optimization algorithm

具体的执行过程如下所示:首先将不同预测模式经过帧内预测后所求得的残差值和码率分别加载到PE00、PE01、PE02和PE03中;分别在PE10、PE11、PE12和PE13中计算各个模式下的SATD值;在计算SATD值的同时,分别在PE30、PE31、PE32和PE33中计算率失真优化算法中所需要的系数λ;待SATD值和系数λ计算完成后,通过邻接互联寄存器,将所求得的SATD和λ传入PE20、PE21、PE22和PE23中,并通过移位和加法运算得到各个模式下所需要的率失真代价RD-cost(Rate Distortion-Cost);通过比较选出具有最小RD-cost值的模式,即代表选择出的最优预测模式。

3.3 率失真优化算法可重构实现

规模重构是指率失真优化算法在不同阵列规模上的重构实现,以满足针对计算时间和视频质量的不同需求选择不同的阵列规模。首先在4×4规模的阵列中,将4条路径并行的算法指令初始化到指令存储器中的0~254号地址中;在8×4规模的阵列中,将8条路径并行的率失真优化算法指令初始化到指令存储器的255~511号地址中。然后获取算法计算时所需的数据,进行4路并行的率失真优化算法的计算。如应用需求对处理速度要求高,则基于上下文切换的重构机制,全局控制器下发配置调用指令,执行存放在255~511号地址中的8路并行的率失真优化算法指令,进行8路并行计算。在通过配置调用进行配置切换的同时,也可通过全局控制器进行指令下发,将多路并行的算法指令下发到阵列中去,实现率失真优化算法在不同规模的可重构阵列上的灵活切换。

Figure 5 Mapping map of pattern reconfiguration

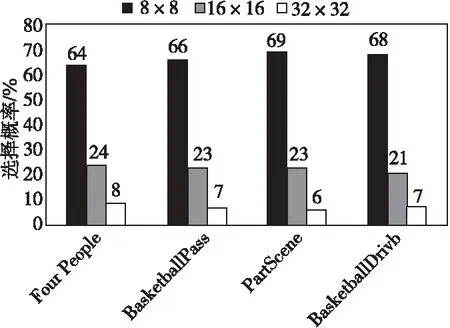

HEVC 采用递归分割四叉树的方法把块分割成不同大小的编码块[13],块重构可以实现不同块大小的率失真优化算法的动态重构。在HM16.0官方软件下对不同测试序列下的CU划分进行统计,结果如图4所示。

Figure 4 Statistics of block division under different test sequences

从图4中可以看出,8×8大小的编码块被选择的平均概率为67%,16×16大小的编码块被选择的平均概率为23%。因此,本文主要选用8×8和16×16大小的编码块进行块重构切换。首先将8×8大小编码块的算法指令初始化到指令存储器中的0~254号地址中,将16×16大小编码块的指令初始化到指令存储器的255~511号地址中。然后获取算法计算时所需的数据,默认进行8×8大小编码块的率失真优化算法的计算,如若不满足CU的划分模式,则全局控制器下发配置调用指令,执行初始化在255~511号地址中的8×8大小编码块的率失真优化算法。也可进行指令下发,将4×4~32×32大小编码块的率失真算法指令下发到阵列中去,根据用户的需求,实现不同块大小的率失真优化算法在可重构阵列上的灵活切换。

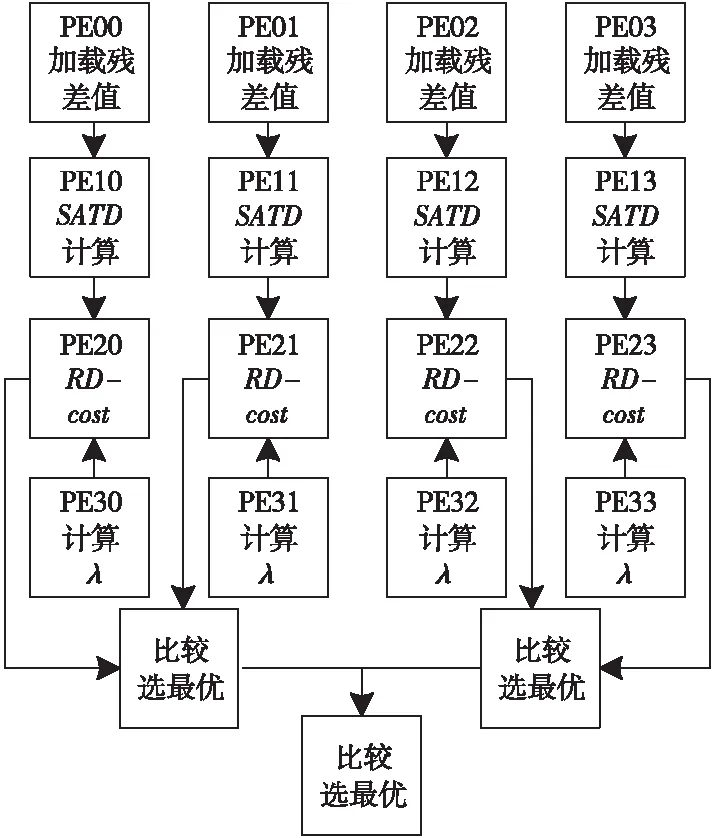

4 帧内预测模式的重构实现

HEVC通过率失真优化选择出最优的预测模式后,根据最优的结果判断帧内环路最终执行哪一种预测模式。同时发送反馈指令,使可重构阵列处理器可以根据收集到的反馈信息进行指令下发,通过指令下发网络发送最优的预测模式指令,完成不同模式的重构。如图5所示,本文使用8×4规模大小的可重构阵列来进行帧内环路的重构实现,PEG00为帧内预测过程,PEG01为率失真优化过程。分析HEVC软件HM16.0在不同测试序列下选择的模式,结果显示Planar模式、DC模式、垂直模式、水平模式、角度模式18 被选中的概率共占94.34%,因此本文选取了这5种预测模式来进行模式预测。在计算这5种预测模式的率失真优化算法时,若最优模式分别为Planar模式、DC模式、垂直模式、水平模式、角度模式18,则将结果分别存到PEG01中PE33的数据存储器中的0,1,2,3,4号地址中。通过指令下发网络下发反馈指令,读出PEG01中PE33的数据存储器中的地址数据,从而判断最终执行哪一种预测模式,指令下发网络再下发相应的预测模式指令,进行后续的计算。

5 实验结果及性能分析

5.1 测试方法及结果

为了验证本文提出的可重构实现方法的可行性,基于可重构阵列结构进行验证。方法如下:首先将所需要的测试数据存入片外存储,然后将并行方案的指令初始化到指令存储器中,最后在可重构阵列结构上通过Questasim 进行仿真验证,通过XILINX公司的ISE14.7开发环境对设计进行综合,得到相应的网表文件,并分析其性能。最后在参考软件HM16.0中测试编码性能,并将本文方法放入帧内环路中,在可重构阵列处理器测试平台上进行验证测试[14]。实验结果表明,工作频率为156.62 MHz,电路规模为87 632 Flip-flops,本文方法在可重构处理器测试平台上具有良好的可视效果。

图6统计了高清测试序列Beauty_1920×1080.yuv使用不同大小编码块的率失真优化算法,完成一帧图像的运行时间。

Figure 6 Run time to complete a frame of image

首先将测试序列通过Matlab软件转换成可重构阵列结构能识别的二进制数值,并将该数据放入可重构视频阵列的输入存储器中,分别通过配置调用和指令下发这2种方式进行测试验证。结果显示,运行时间最长为17.6×10-3s,帧率为56 fps,满足1920×1080@30 fps视频序列的实时编码要求,可以看出本文提出的可重构实现方法能够适应高清视频图像。

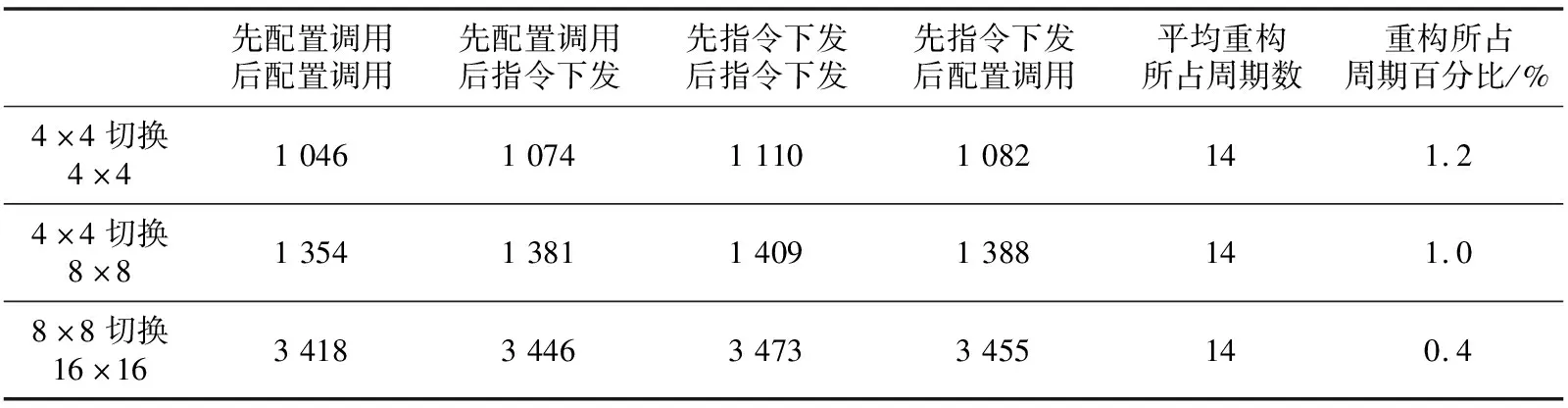

表1统计了不同配置的率失真优化算法通过不同方式进行重构切换的总周期数以及重构所占的时钟周期数。通过表1可以看出,不论是相同大小编码块还是不同大小编码块的率失真优化算法,通过配置调用或指令下发这2种方式进行重构切换时,重构所占的时钟周期数都很小,不会对算法执行的总周期数产生较大的影响。以4×4大小的块切换8×8大小的块为例,平均重构仅占14个时钟周期,仅占总执行时间的1.0%。因此,本文提出的可重构实现方法可以实现快速切换。

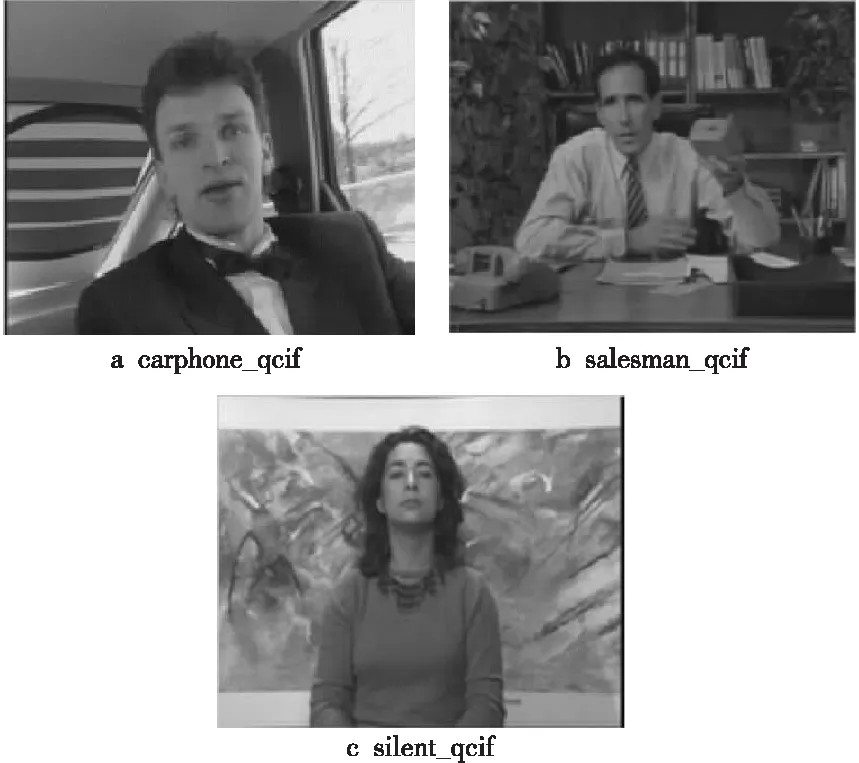

以标准测试序列:carphone_qcif、salesman_qcif和silent_qcif为例,使用本文的可重构率失真优化实现方法作为帧内预测模式选择的判别依据,在BeeCube公司的BEE4搭建的可重构视频阵列处理器测试平台上进行验证测试,如图7所示为一个完整I帧的测试结果。其中,图7a为测试序列carphone_qcif在可重构视频阵列处理器上的测试结果,图7b为测试序列salesman_qcif在可重构视频阵列处理器上的测试结果,图7c为测试序列si-lent_qcif在可重构视频阵列处理器上的测试结果。由图7可见,测试结果具有良好的可视效果。

Figure 7 Test results

Table 1 Reconfigurable switching cycles

5.2 性能分析

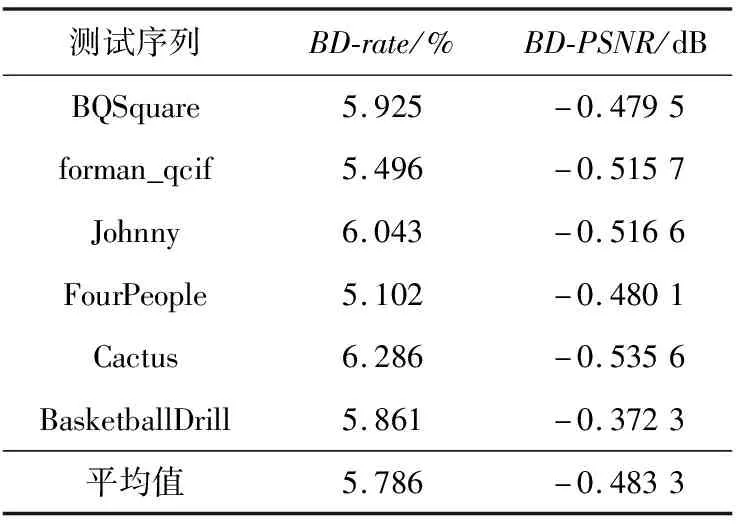

本文在参考软件HM16.0上对编码性能进行测试,使用6组不同视频内容的测试序列在全I帧的配置下的实验结果如表2所示,通过M33标准代码计算得出BD-rate和BD-PSNR。通过表2可以得出,平均BD-PSNR为5.786%,平均BD-rate为-0.483 3 dB。

Table 2 Coding performance analysis

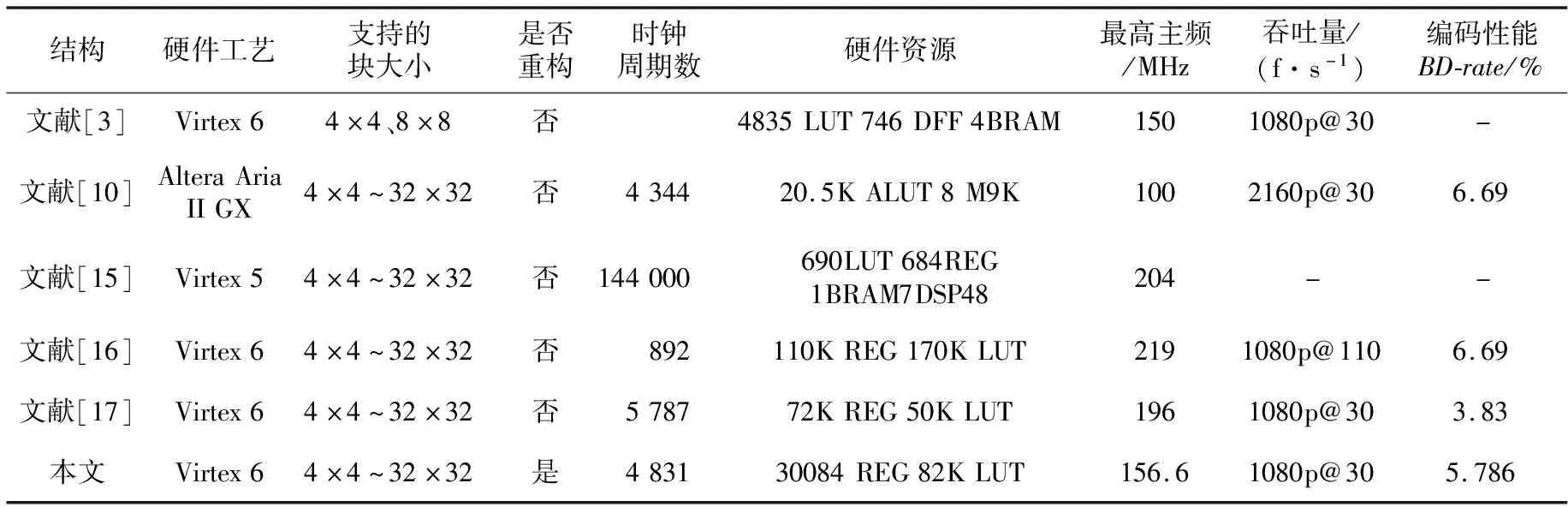

实验所设计的可重构阵列处理器用Verilog HDL语言描述,以标准测试序列akiyo_qcif作为测试序列在Questasim 10.1d工具下进行功能仿真验证,采用XILINX公司的ISE14.7开发环境进行综合,选用BEEcube公司的BEE4系列开发板进行FPGA测试,结果如表3所示。本文所提出的可重构实现方法,支持各个块大小的率失真优化算法,使用测试序列akiyo_qcif进行测试,实现32×32块大小下的算法判别时,花费4 831个时钟周期。

从表3中可以得到,在吞吐量相同的情况下,与文献[3]方法的结构设计相比,本文方法的结构设计在支持大小为4×4~32×32的编码块的同时,最高主频相差不大,且支持动态可重构;文献[10]方法的结构设计的吞吐量比本文方法的结构设计更优,但编码性能相比本文的设计较差,在时钟周期数基本相同的情况下,最高主频增加了56%;文献[15]方法的结构设计虽然可以支持任意大小的PU,硬件资源消耗较少,但十分耗费时钟周期;文献[16]方法的结构设计的吞吐量优于本文的设计,并且执行过程中仅仅消耗892个时钟周期,但相比于本文方法的结构设计,其编码性能较差,且硬件资源消耗增加了150%;文献[17]方法的结构设计引入了头比特估计的方法,简化了率失真优化算法计算的过程,但其硬件设计不能灵活实现不同块算法之间的切换,本文方法的结构设计与之相比,在吞吐量相同的情况下,虽然编码性能有所降低,但硬件资源减少了8.2%,执行的时钟周期数减少了16.5%,可以实现不同配置算法之间的快速切换。

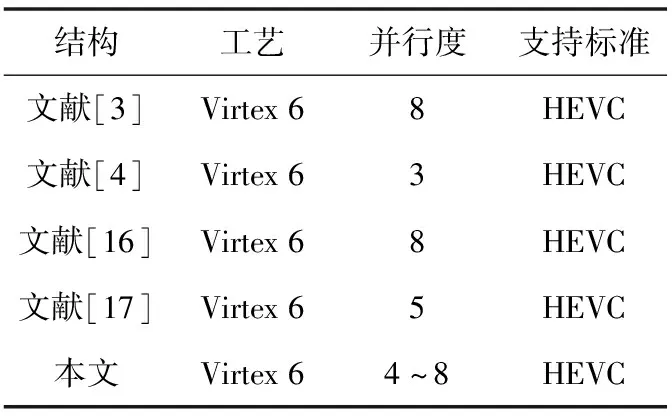

表4为可同时进行多种预测模式处理的并行度对比。本文的可重构实现方法支持4~8路并行的处理方式,可以根据应用处理速度的需求的不同进行选择,在并行方式的选择上比文献[3,4,16,17]方法更加灵活。

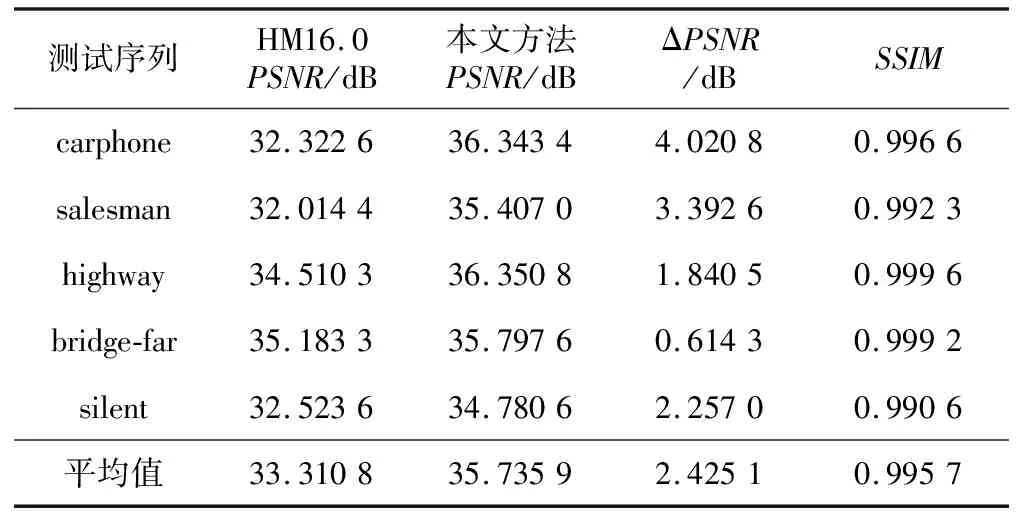

使用本文方法作为帧内预测模式的判断依据,选取了5组测试序列在BEEcube公司的BEE4系列开发板搭建的可重构阵列处理器测试平台上进行验证测试。峰值信噪比PSNR(Peak Signal to Noise Ratio)和结构相似性SSIM(Structural Similarity Index Measurement)是2种常用的图像质量评价指标。对一个完整I帧的测试结果图像进行分析,如表5所示,相比在HM16.0测试一个完整I帧的结果,本文方法的平均PSNR值增加了3.223 dB,平均SSIM值为0.999 3。

Table 3 Structural comparison

Table 4 Parallelism comparison

Table 5 Test performance analysis

6 结束语

本文针对基于视频阵列处理器HEVC灵活的编码块增加了率失真优化算法硬件实现的难度,难以实现阵列规模和不同块的灵活切换的问题,提出一种支持动态可重构的率失真优化实现方法。该方法基于上下文切换的重构机制,能够灵活地对不同配置算法进行切换,并且最大限度地利用可重构阵列处理器。实验结果表明,本文方法对于率失真优化算法的可重构实现,可以达到实时处理的需求,可以快速实现不同规模、不同块大小算法之间的灵活切换。对比文献[17]方法,在支持多个块大小的情况下,本文方法使用的硬件资源减少了8.2%,算法执行的时钟周期数减少了16.5%,最突出的优点是可以根据计算时间和视频质量的不同需求,对阵列结构的规模和执行模式进行重新调度。