Ti,N 共掺杂4H-SiC 复合增强缓冲层生长及其对PiN 二极管正向性能稳定性的改善*

2021-02-06李传纲鞠涛张立国李杨张璇秦娟张宝顺张泽洪

李传纲 鞠涛 张立国 李杨 张璇秦娟 张宝顺‡ 张泽洪

1) (上海大学材料科学与工程学院,上海 200444)

2) (中国科学院苏州纳米技术与纳米仿生研究所,苏州 215123)

“双极型退化”现象严重阻碍了4H-SiC 双极型器件如PiN 二极管等的产品化,其微观机理是电子-空穴复合条件下层错由基面位错处的扩展.为遏制“双极型退化”现象,不仅要消除漂移层中的基面位错,还需要通过生长复合增强缓冲层的方法阻止少子空穴到达含高密度基面位错片段的外延层/衬底界面.本文采用钛、氮共掺杂的方式进行缓冲层的生长,通过钛掺杂进一步降低缓冲层中的少子寿命.首先确定了钛掺杂浓度和钛源摩尔流量之间的定量关系,在此基础上制备了含钛、氮共掺杂缓冲层结构的4H-SiC PiN 二极管,并在正向电流密度100 A/cm2 的条件下保持10 min,测量其正向压降随时间的变化.与无缓冲层结构、仅含高浓度氮掺杂缓冲层结构的4H-SiC PiN 二极管相比,含钛、氮共掺杂缓冲层的二极管的正向压降稳定性得到了明显改善.

1 引 言

碳化硅(silicon carbide,SiC)双极型器件如PiN 二极管长时间处于正向偏压时,其开态压降会随时间增大,这种现象被称为“双极型退化”现象.2001 年,Lendenmann 等[1]首次报道了这种SiC双极型退化现象,引起了人们对SiC 双极型器件长时间工作的稳定性以及可靠性问题的关注.研究发现,SiC 外延漂移层中的基面位错(basal plane dislocation,BPD)是导致双极型退化的根本原因:在电子-空穴复合条件下,BPD 会发生硅核分位错(Si-core partial)的滑移从而导致肖克利类型层错(Shockley-type stacking fault,SSF)扩展,引起器件导通电阻的增加[2−4].双极型退化现象阻碍了SiC 电力电子器件向超高压领域的发展,是业内亟需解决的关键问题之一.

针对从SiC 衬底延伸进入漂移层的BPD[5],研究发现通过增强BPD 在外延层/衬底界面处向贯穿刃位错(threading edge dislocation,TED)的转化来降低漂移层中的BPD 密度,可有效避免层错扩展[6]; 另外,BPD-TED 转化位点靠近外延层/衬底界面,此处BPD 密度高,在大的正向电流密度下高浓度少子(空穴)的注入也会使电子-空穴复合在此处发生,从而引起层错扩展[7].对于前者,研究发现使用熔融KOH 腐蚀衬底或图形化衬底表面、提升外延生长速率以及间断式生长等技术手段[8−10]可以提高BPD-TED 转化率.目前优化后的外延生长条件可以使得SiC 外延层中的BPD 密度降至0.1 cm–2以下; 针对后者,Mahadik 等[11]提出在漂移层和衬底之间插入一层低少子寿命的缓冲层,通过有效降低到达BPD-TED 转化位点处的少子浓度,有望遏制转化位点处的电子-空穴复合,从而避免层错扩展.

复合增强缓冲层的名称最早出现于2016 年Tawara 等[12]的报道.作者采用高浓度氮(N)掺杂(Nd= 9.3×1018cm–3)的方式,主要通过增强俄歇复合来降低4H-SiC 缓冲层中的少子寿命,其室温值为38 ns,比7.7×1017cm–3氮掺杂条件下的250 ns 显著降低.在此基础上制备出含高浓度N 掺杂缓冲层结构的PiN 二极管,测试结果显示,含10 µm,Nd= 1×1018cm–3复合增强缓冲层的PiN 二极管与含0.12 µm,Nd= 4×1017cm–3复合增强缓冲层的PiN 二极管相比,开态压降的稳定性得到明显改善,即使在几百A/cm2电流密度下通电若干小时,开态压降的增加也不超过10 mV(18 A/cm2测 试 条 件).2017 年,Miyazawa 等[13]研究发现,相比仅高浓度N 掺杂,过渡金属杂质如钒(V)、钛(Ti)的加入可进一步降低外延层中少子寿命.N 掺杂浓度5×1018cm–3以及V 掺杂浓度7×1014cm–3条件下,外延层室温少子寿命低至13 ns[14].2019 年,Murata 等[15]进一步研究得到,含2.4 µm N 和V 共掺杂缓冲层结构(Nd= 1 ×1018cm–3,Nv= 1×1014cm–3)的4H-SiC PiN 二极管在600 A/cm2正向电流密度条件下维持1 h,开态压降的增加不超过20 mV (486 A/cm2测试条件).2017 年,Tawara 等[16]通过N、硼(B)共掺杂的方式将4H-SiC 外延层少子寿命降低至30 ns以下(Nd= 6×1018cm–3,NB= 8×1016cm–3),并且制备出含N,B 共掺杂缓冲层结构(Nd= 4 ×1018cm–3,NB= 7×1017cm–3,2 µm)的正向压降稳定的PiN 二极管,600 A/cm2正向电流密度下维持1 h,没有发现层错扩展.

事实上,对SiC 晶体进行过渡金属掺杂的技术更早被应用在单晶生长中.SiC 基或GaN 基高频器件需要用到高电阻率的晶圆,而早期通过纯化工艺很难将背景掺杂浓度降至1010cm–3以下.V 是第一个在SiC 中用作深能级补偿中心来降低自由载流子浓度、制造半绝缘晶圆的元素.研究发现,V 在4H-SiC 中为两性杂质,其类受主能级(n 型SiC 中)为Ec– (0.81—0.97) eV,类施主能级(p 型SiC 中)为Ev+ (1.3—1.5) eV[17,18].后来随单晶生长技术的进步,SiC 半绝缘晶圆逐渐采用在高纯晶体中引入本征点缺陷深能级的方法来制造.与单晶生长相比,采用化学气相沉积(chemical vapor deposition,CVD)的SiC 外延生长更容易对杂质的掺杂浓度进行精准控制.除V 元素以外,Ti 元素也被尝试用来降低缓冲层中的少子寿命[13].作为CVD 石墨件中常见的过渡金属杂质,早期文献显示Ti 在n 型4H-SiC 中会产生两个类受主能级Ec– 0.12 eV 和Ec– 0.16 eV[19,20].Miyazawa 等[13]的实验结果显示,N 掺杂浓度5×1018cm–3、Ti 掺杂浓度5×1014cm–3条件下,外延层室温少子寿命低至11 ns.这说明在降低少子寿命的效果方面,Ti 掺杂与V 掺杂效果相近,并且有可能更有效.然而,业内对Ti 掺杂复合增强缓冲层的研究很少,且尚无来自器件性能的验证.因此,本文在原SiC CVD 外延设备气路基础上新添加Ti 掺杂气路进行了Ti 掺杂外延实验.实验研究了Ti 掺杂浓度随Ti 源摩尔流量的变化规律,并制备了含Ti,N共掺杂缓冲层结构的4H-SiC PiN 二极管,对其开态压降的稳定性进行了测试.结果显示,相比于无复合增强缓冲层的PiN 二极管以及含高浓度N 掺杂复合增强缓冲层的PiN 二极管,含Ti,N 共掺杂复合增强缓冲层的PiN 二极管开态压降的稳定性得到了明显改善.

自SiC 双极型退化现象首次发现后的5—6年,业内迅速积累了对缺陷结构、缺陷能级、退化现象的驱动力和激活能等方面的物理理解,并因此对SiC 外延层内的BPD 密度提出了很高要求.随着SiC 外延技术的提高,这个要求现在已可以满足.因而近几年来有关SiC 双极退化现象的研究报道主要集中在如何遏制BPD-TED 转化位点处的层错扩展、对机理问题更细致深入的调查以及器件结构设计与性能验证.本工作初步证实了Ti 掺杂复合增强缓冲层的有效性,在此基础上将进一步对含复合增强缓冲层结构的SiC PiN 二极管的退化现象开展深入研究,对缓冲层结构进行优化,以期最终实现零开态压降漂移.

2 实 验

2.1 4H-SiC 漂移层及缓冲层的外延生长

本实验所使用的衬底是Si 面4°斜切偏向[11−20]方向的n+型4H-SiC 4 in (1 in = 2.54 cm)商业衬底,被划分为15 mm×15 mm 的方形小片; 同质外延实验在自主搭建的4 in 垂直式热壁CVD 系统中进行(图1(a)).本实验采用的生长温度为1575 ℃,压强为75 Torr (1 Torr ≈ 133.322 Pa);采用SiH4-C3H8-H2-HCl 反应体系,其中H2流量30 slm (1 slm = 1 L/min),SiH4流量 为15 sccm(1 sccm = 1 mL/min),HCl 流量200 sccm,生长速率5—8 µm/h.外延掺杂分别将氮气(N2)、液态四氯化钛(TiCl4)用作N 源和Ti 源.载气、生长用源气和掺杂气体通过一个倒漏斗形的喷嘴进入反应腔室,喷嘴的锥形角度为45 °,距离衬底6 mm,衬底基座在生长过程中缓慢旋转(约2 r/min).

实验过程中采用单稀释和双稀释两种方式进行Ti 掺杂,所使用Ti 掺杂气路示意图如图1(b)和图1(c)所示.在Ti 掺杂过程中,TiCl4源瓶压力(Pbub)通过电子压力控制器(electronic pressure controller,EPC)固定为800 Torr,源瓶温度范围为19.1—20.7 ℃.通过调节各气体流量控制器(mass flow controller,MFC)可控制最终进入腔室的TiCl4摩尔流量,从而控制SiC 中的Ti 掺杂浓度.稀释管路中用H2作载气,进入源瓶的载气F1(MFC1 控制)被Ti 源饱和,流出源瓶后立即与另一股载气F2(MFC2 控制)混合.与单稀释管路不同的是,双稀释管路中稀释后的混合气体只有一部分F3(MFC3 控制)的气流进入反应室,适用于更低Ti 掺杂浓度的外延生长实验.

图1 (a) 4H-SiC CVD 外延设备示意图; Ti 掺杂(b)单稀释和(c)双稀释管路示意图Fig.1.Schematics of (a) the CVD reactor for 4H-SiC epitaxial growth,(b) single-dilution pipe and (c) double-dilution pipe of TiCl4 gas delivery.

4H-SiC PiN 二极管结构中复合增强缓冲层的N 掺杂选取的是C/Si = 0.7,N2流量为200 sccm的生长条件,掺杂浓度为1.01×1019cm–3; Ti 掺杂条件依据Ti 掺杂生长实验的结果确定,将在后面3.1 节中介绍; 缓冲层厚度为2 µm,漂移层厚度为12 µm,C/Si = 1.0,背景非故意N 掺杂浓度为2×1016cm–3.

2.2 4H-SiC PiN 二极管制备

图2 (a) 含Ti,N 共掺杂缓冲层结构的SiC PiN 二极管结构示意图; (b) TRIM 模拟的Al 注入浓度箱型分布Fig.2.(a) Schematic of the cross-sectional structure of a 4H-SiC PiN diode with Ti and N co-doped buffer layer; (b) box-profile of Al concentration by TRIM simulation.

实验中制备的4H-SiC PiN 二极管的示意图如图2(a)所示.p 层结构由离子注入完成.TRIM软件模拟的Al 离子注入的箱型深度分布曲线如图2(b)所示,包含300 nm,Al 浓度1×1019cm–3的p+层和200 nm,Al 浓度1×1020cm–3的p++层.其中p+层注入在室温实施,p++层则采用了500 ℃的高温注入工艺.两步注入完成之后对样品进行1650 ℃,30 min 的激活退火.为防止高温下SiC 表面粗糙化,退火前在样品上、下表面均通过光刻胶固化制备了碳膜.退火后碳膜在等离子去胶机中由纯氧等离子体工艺去除.二极管的下电极沉积200 nm Ni 金属,在N2气氛下1000 ℃快速退火2 min,与背部n-SiC 形成欧姆接触; 上电极沉积Ti/Al (30/100 nm)金属,在N2氛围下950 ℃快速退火2 min,与激活后的p++-SiC 形成欧姆接触.注入区域为圆形,定义了二极管的直径从320—820 µm.为考察复合增强缓冲层对4H-SiC PiN 二极管正向性能稳定性的影响,本实验同时制备了无缓冲层的二极管及含高浓度N 掺杂缓冲层的二极管,除缓冲层外,其他参数均与图2 相同.

2.3 材料表征与器件测试

4H-SiC 漂移层和缓冲层的生长表面使用Nomarski 显微镜进行检测,通过表面形貌缺陷的长度可以推测外延层厚度; 利用水银探针台C-V 测试来获取漂移层掺杂浓度; 样品中的Ti 掺杂浓度以及注入区的Al 浓度通过二次离子质谱(secondary ion mass spectroscopy,SIMS)测试获得; 利用高压高流探针台对有/无缓冲层结构的4H-SiC PiN二极管进行电学测试,观察100 A/cm2电流密度下偏置10 min 后PiN 二极管正向压降的变化情况.很显然,SiC PiN 二极管的正向电压稳定性和所施加的正向电流密度相关.本实验选取100 A/cm2这个文献中较为典型的测试电流密度,关注具有不同缓冲层结构的SiC PiN 二极管之间正向压降稳定性的差异.事实上,有关电子-空穴复合条件下层错扩展的临界电流密度以及位错滑移的热力学仍是业内尚未充分研究的问题.

3 结果与分析

3.1 Ti 掺杂缓冲层的生长

单稀释条件下,进入反应室的TiCl4摩尔流量nTiCl4-S(mol/min)可由下式计算:

式中,PTiCl4为TiCl4的蒸气压,Pbub为源瓶压力,F1为MFC1 控制的进入源瓶的载气流量(sccm),Vm= 22414 cm3/mol.

双稀释条件下,进入反应室的TiCl4摩尔流量nTiCl4-D(mol/min)可由下式计算:

式中,F2为MFC2 控制的进一步稀释源气的载气流量,F3为双稀释管道中MFC3 控制的最终进入腔室的混合气体流量.

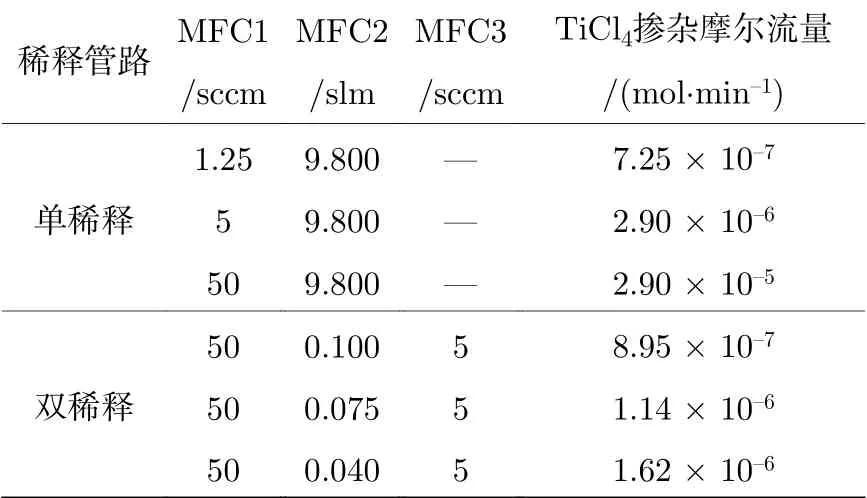

单稀释、双稀释Ti 掺杂实验参数如表1 所列.单稀释TiCl4摩尔流量范围为7.25×10–7—2.90 ×10–5mol/min,双稀释TiCl4摩尔流量范围为8.95 ×10–7—1.62×10–6mol/min.双稀释条件下的Ti掺杂浓度取对数后与TiCl4摩尔流量取对数后基本呈线性关系,如图3 所示.图中直线是仅对双稀释的数据点进行的线性拟合,得到的斜率为1.2,略高于1.0.图中虚线仅是为了方便指出单稀释的掺杂浓度变化趋势.从图3 还可以看到,TiCl4摩尔流量非常接近的单稀释方式所获得的Ti 掺杂浓度比双稀释方式要略高.当TiCl4摩尔流量高达2.90×10–5mol/min 以及Ti 掺杂浓度为3.71 ×1016cm–3时,对应数据点会明显向下偏离虚线所指出的变化趋势.此掺杂条件下4H-SiC 缓冲层表面如图4(b)所示.可以看到缓冲层表面遍布条状形貌缺陷,缺陷长度方向与台阶流方向近似垂直.而在Ti 掺杂浓度较低时(< ~1.00×1016cm–3),4H-SiC 缓冲层表面呈现典型外延表面形貌,未见条状缺陷,如图4(a)所示,对应Ti 掺杂浓度3.70 ×1015cm–3.与此观察结果类似,Miyazawa 等[14]报道了在无HCl 的生长气氛中进行V,Ti 掺杂可能会导致4H-SiC 外延表面出现高密度形貌缺陷的实验现象.本文的实验观察也发现,在同样的TiCl4摩尔流量条件下,无HCl 外延所得到的Ti 掺杂浓度要高于含HCl 外延.高浓度Ti 掺杂所引发的条状形貌缺陷的结构与成分还需要进一步研究,图3中单稀释方式最高TiCl4摩尔流量所对应的数据点明显向下偏移,表明条状形貌缺陷可能富Ti,从而使外延生长的Ti 掺杂效率降低.

表1 Ti 掺杂实验参数Table 1.Experimental parameters of Ti doping.

图3 Ti 掺杂浓度随TiCl4 摩尔流量的变化Fig.3.Relationship between Ti doping concentration and TiCl4 mole flow rate.

图4 Ti,N 共掺杂4H-SiC 缓冲层表面形貌(Nd = 1.01 ×1019 cm–3) (a) Ti 掺杂浓度为3.70×1015 cm–3; (b) Ti 掺杂浓度为3.71×1016 cm–3Fig.4.Optical microscope images of the Ti and N co-doped 4H-SiC buffer layer surface with Ti doping concentrations of (a) 3.70×1015 cm–3 and (b) 3.71×1016 cm–3.Both with Nd = 1.01×1019 cm–3.

值得说明的是,图3 中双稀释方式的数据点彼此比较靠近,可能给线性拟合的斜率造成较大误差(1.2 相比于理想情况的1.0).而单稀释与双稀释的掺杂效率差别可能是由管路中TiCl4的实际状态与(1)式、(2)式有所差别造成的.

依据以上结果,选取了双稀释条件下TiCl4摩尔流量8.95×10–7mol/min,对应Ti 掺杂浓度3.70×1015cm–3,作为Ti,N 共掺杂缓冲层生长的Ti 掺杂条件.

3.2 4H-SiC PiN 二极管正向性能测试

制备完成4H-SiC PiN 二极管后,对其施加正向电流密度100 A/cm2持续10 min,并对正向偏置10 min 前后的正向电流-电压曲线进行测量.图5(a)、图5(c)、图5(e)分别给出了无缓冲层结构、含仅高浓度N 掺杂缓冲层结构、以及含Ti,N 共掺杂缓冲层结构的二极管正向偏置时正向压降随时间的变化,图5(b)、图5(d)、图5(f)给出了正向偏置前后的电流-电压曲线对比.

图5 无缓冲层、仅含高浓度N 掺杂缓冲层、含Ti 和N 共掺杂缓冲层的4H-SiC PiN 二极管的正向特性 (a),(c),(e)在100 A/cm2 电流密度下10 min,正向压降随时间的变化; (b),(d),(f)正向偏置前后正向电流-电压曲线的对比Fig.5.(a),(c),(e) Change of forward voltage drop vs.time and (b),(d),(f) comparison between the forward I-V characteristics before and after being biased for 10 min at a current density of 100 A/cm2 for 4H-SiC PiN diodes without a buffer layer,with a highly N-doped buffer layer,and with a Ti and N co-doped buffer layer.

从图5 可以看出,在100 A/cm2的电流密度下,经过10 min,无缓冲层结构的4H-SiC PiN 二极 管 的 正 向 压 降 由5.46 V 增 加 至9.49 V,仅 含N 掺杂缓冲层结构的PiN 二极管正向压降由6.03 V 增加至7.71 V,而含Ti,N 共掺杂缓冲层结构的PiN 二极管正向压降基本维持在4.50 V.造成正向压降漂移的层错扩展可能来自于外延层中的BPD、外延层/衬底界面处BPD-TED 转化位点、以及器件工艺过程中可能引入的BPD.这些BPD 的结构不尽相同,位于二极管中不同位置所对应的电子-空穴复合率也不一样.以上因素皆会影响到器件的正向性能.然而考虑到三种器件的区别仅在于缓冲层结构,因而认为Ti,N 共掺杂缓冲层对4H-SiC PiN 二极管正向压降增大起到明显的改善作用.也就是说,Ti 的掺入进一步降低了缓冲层中的少子寿命,从而有效地阻止空穴到达缓冲层/衬底界面,遏制了层错由界面附近BPD-TED转化位点处的扩展,提高了4H-SiC PiN 二极管正向压降的稳定性.后续工作将在此基础上对Ti 掺杂复合增强缓冲层进行更深入、系统的研究,并与文献中对V 掺杂复合增强缓冲层的报道进行对比[13−15].

值得说明的是,图5(a)和图5(c)显示无缓冲层结构的PiN 二极管的正向压降的增加呈现明显的“台阶”,经过一段时间会有一个明显的增大; 而含高浓度N 掺杂缓冲层的PiN 二极管的正向压降的增加较为连续.这个现象在实验中所测试的二极管中有一定共性,推测其对应着位错滑移/层错扩展的不同微观机制,需要进一步研究.

4 总 结

本文采用单稀释和双稀释两种方式进行了Ti 掺杂4H-SiC 同质外延研究,得到了Ti 掺杂浓度与TiCl4摩尔流量之间的定量关系,并在此基础上制备了含Ti,N 共掺杂缓冲层的4H-SiC PiN 二极管.与无缓冲层结构及仅含高浓度氮掺杂缓冲层结构的PiN 二极管相比,含2 µm Ti 掺杂浓度3.70×1015cm–3,N 掺杂浓度1.01×1019cm–3缓冲层结构的二极管经10 min,100 A/cm2电流密度测试后显示正向压降稳定性得到显著改善,验证了Ti,N 共掺杂方式制备复合增强缓冲层是遏制4H-SiC PiN 二极管“双极型退化”的有效途径之一.本工作为进一步深入研究不同缓冲层结构下器件内部层错扩展的微观机制、临界电流密度、缓冲层结构的设计与仿真、以及最终实现无退化的双极型SiC 电力电子器件打下了基础.

感谢中国科学院苏州纳米技术与纳米仿生研究所纳米加工平台和纳米真空互联实验站提供的实验和测试帮助.