宽带电力线载波通信芯片的FPGA验证

2021-01-21迟海明周春良赵东艳王于波唐晓柯

迟海明,周春良,赵东艳,王于波,唐晓柯

(北京智芯微电子科技有限公司,北京 100192)

随着微电子技术的进步,集成电路的发展日新月异,人们对低成本、低功耗、高性能的芯片设计不断地提出更高的要求。片上系统(SoC)设计理念就是在这样的追求中发展了约20年。随着SoC设计复杂度不断增高,功能验证的难度也在不断加大,更加耗时。现场可编程逻辑阵列(FPGA),经过约30年的发展,不仅可以作为单一逻辑功能部件来使用[1-3],更已达到片上系统调试的性能要求,在容量上可以通过一片或多片FPGA装下整个SoC的数字部分[4]。FPGA原型验证是将SoC数字部分以及一部分数模混合部分,一致的或通过一定约束的改变,映射到FPGA中进行软硬件协同开发调试。其目的,一是为了对设计有直观的了解,可以在芯片流片前展示整个系统的设计概念,做协议互联互通测试;二是希望软件可以和硬件同步开发,提高整个系统的开发效率;三是可以作为参考模型辅助芯片调试。文中以最新一代电力专用宽带电力线载波通信芯片为例,介绍FPGA原型验证的设计流程以及应用。

1 宽带电力线载波通信芯片

1.1 研发背景

随着智能电网建设的推进,通信速率低、可靠性差的窄带电力线载波通信技术作为本地接入方式,已不能满足用电信息交互的需求。在这样的背景下,宽带电力线载波通信技术规范得以提出。基于国家电网新标准[5]并兼容南方电网标准[6]的高速宽带电力线载波通信芯片[7-8],从提出经过不断增强,目前已经大规模量产[9-12]。

1.2 芯片结构

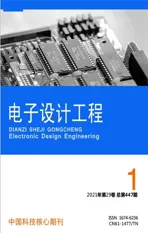

芯片结构如图1所示。芯片采用AMBA总线架构,第一级为32位AHB总线。主设备包括CPU核和系统DMA控制器。从设备有SDRAM控制器及其配置接口、系统DMA控制器、SPI Flash控制器、BootROM、SRAM控制器、AHB2APB桥以及电力载波通信加速器(PLC)。第二级总线为APB总线,连接的设备有定时器、PWM模块、GPIO接口、UART接口、SPI接口、I2C接口以及系统控制单元(SCU)。芯片的模拟部分包含低抖动的系统PLL以及高性能、低功耗的模拟前端(AFE)。其中,AFE又包含高精度模数/数模变换器(AD/DA)、低通滤波器(LPF)以及可控增益放大器(PGA)。

图1 芯片结构

1.3 电力载波通信物理层设计

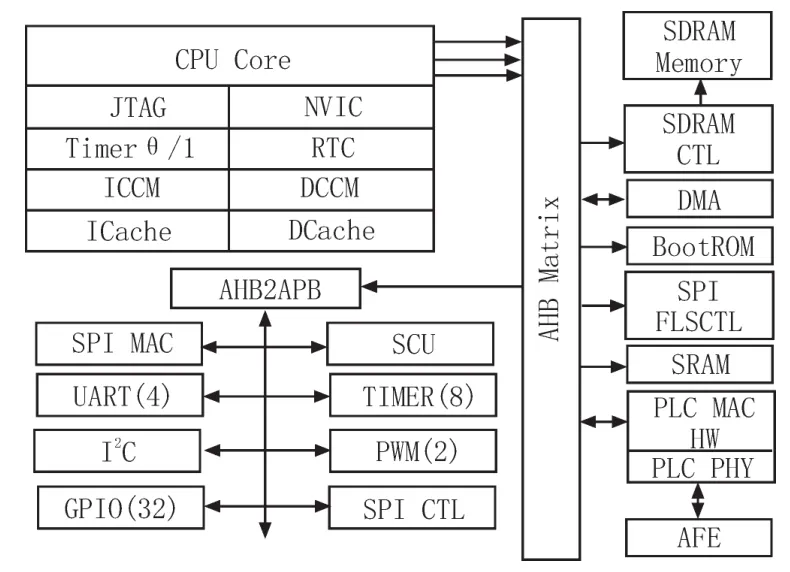

FPGA原型验证的主要工作是对载波通信物理层加速器进行协议验证及性能验证。物理层收发结构如图2所示。包括:加扰/解扰、信道Turbo编码/解码、信道交织/解交织、分集拷贝/分集合并、星座映射/解映射、IFFT/FFT、同步定时、数字前端以及信道数据采集。

图2 物理层收发结构

2 FPGA原型验证平台设计

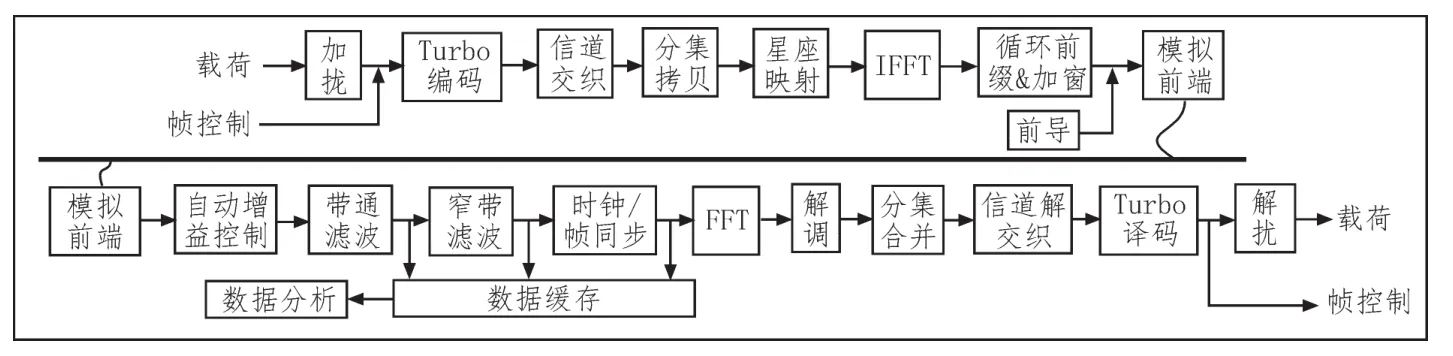

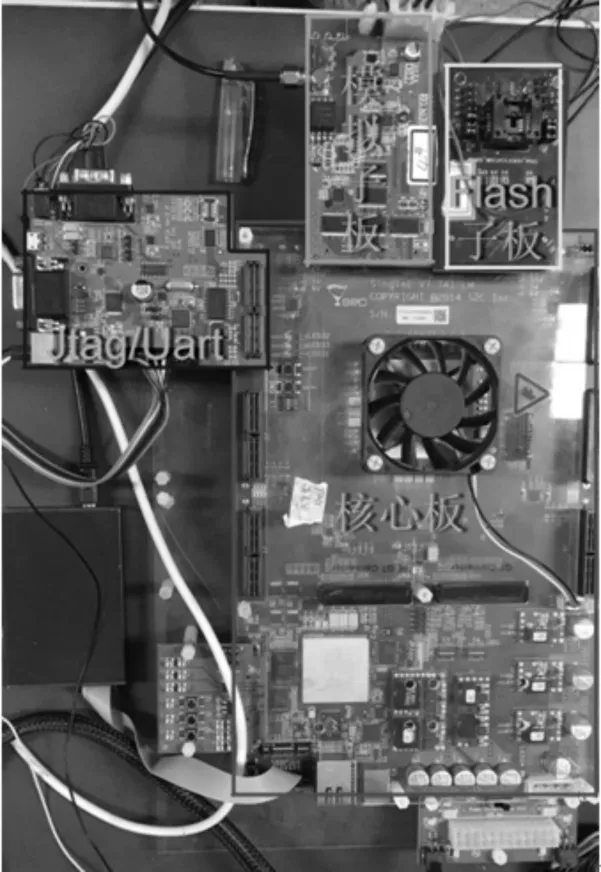

对于一个很大的ASIC设计,如果资源有限,就不得不将设计进行分割映射到多片FPGA,通过接口互联来实现原本内部信号的连通[13]。这对板级设计以及调试带来更大的难度,应尽量避免。文中FPGA验证平台环境分为硬件和软件两部分,如图3所示。硬件部分的主体是带有Virtex7 2000T-FLG1925的核心板。2000T-FLG1925型号可以支持到2 000万门的ASIC设计[14],足够容纳所述设计的数字部分。核心板具有专用高速I/O接口,连接JTAG/UART子板、模拟子板和FLASH子板。软件部分包括FPGA设计软件VIVADO、FPGA核心板配置软件以及SoC驱动开发/调试环境 Metaware IDE/Debugger(MDB)。

图3 FPGA原型验证平台结构

PC机USB口通过DigilentJTAG仿真器连接到JTAG/UART子板,负责加载驱动程序以及载波信息数据传输。FLASH子板作为程序数据存储区。模拟子板负责数模/模数转换、滤波和放大,最终信号可耦合到电力线或同轴电缆进行收发。

3 FPGA设计流程

3.1 前端设计移植

FPGA与芯片前端设计的不同之处在于硬件单元种类有限、结构固定、连接关系冗余[15]。因此要将不能映射到FPGA中的部分进行移植,改变时钟及所涉及路径的约束。文中所述设计移植的原则是:只进行独立IP的替换及与之相关的逻辑修改,最大限度保证芯片与FPGA设计的一致性。芯片中的系统PLL部分替换为时钟管理(MMCM)资源,去掉大部分时钟门控机制并将其余改为数据门控。模拟IP替换为片外性能相近的第三方芯片,内部与模拟IP相关接口根据第三方芯片进行修改并引到FPGA管脚。对第三方模拟芯片的控制也做了相应的增加。

3.2 前端设计验证

在上板调试FPGA前,应首先对移植的设计进行功能验证。如果前端设计阶段进行的功能验证不够充分,依靠在板级调试阶段通过内建逻辑分析(Chipscope)手段去排查逻辑功能错误,既耗时又难以获取足够的观察时间及信号数目。通过复用基于覆盖率驱动的芯片验证环境[16]进行FPGA设计验证,保证功能检验结果的一致性。对于功能而言,不针对FPGA额外构建测试用例,而是复用已有的芯片测试用例,从功能的角度考察移植是否正确。对于外部接口电路的改动,可以构建针对FPGA的特殊用例。除了针对第三方模拟接口做了单独的验证用例外,其余均复用芯片验证用例,功能覆盖率达到100%。

3.3 FPGA设计软件流程及实现结果

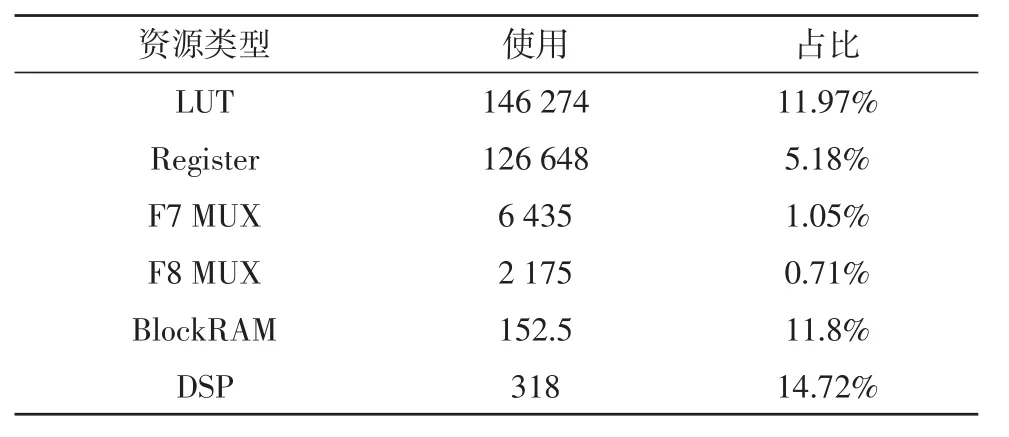

设计采用Synopsys的Synplify进行综合,以输出更好的综合结果。将PRJ格式的设计及策略脚本文件与FDC格式的约束文件输入综合工具,综合输出EDF格式的网表文件。然后,将EDF网表文件及XDC格式的时钟及管脚约束文件通过TCL脚本文件附带一定的工具策略输入到Vivado进行布局布线,输出用于FPGA下载的BIT文件。最终时序分析报告没有出现时序违例,所占资源结果如表1所示。

4 FPGA原型验证平台应用

FPGA原型验证板级调试主要通过驱动软件对原型设计进行操作,测试CPU、总线、接口以及电力线载波物理层加速器的功能。图4是FPGA硬件平台实物图。将功能子板插接到核心板的专用高速I/O接口,从而连接到FPGA的管脚。利用核心板配置软件配置FPGA,用DigilentJTAG仿真器连接PC机USB口和Jtag/Uart子板,启动Metaware IDE,在线修改寄存器值,触发硬件操作,观察各部分硬件功能是否达到预期结果。在产生新的系统需求时,通过修改RTL代码重新回归FPGA自动化流程,实现快速评估。协议软件通过采用Metaware IDE在线调试,实现软硬件协同开发。

表1 FPGA资源占用结果

图4 FPGA硬件平台

通过搭建两套验证平台,实现物理层在不同调制模式下的收发功能。用带可调衰减的同轴线连接收端和发端模拟板同轴接口。用串口线连接收端和发端的Uart子板的RS-232串口。将编译好的接收端驱动程序用MDB通过DigilentJTAG仿真器下载到接收端Flash子板中,然后将仿真器接到发送端Jtag子板,通过命令行触发测试启动。原始信息通过发送端Jtag子板传入FPGA进行发送端处理,调制信号耦合到模拟线路。调节可调衰减器可模拟线路衰减行为,接收端在解调后将信息通过串口传回发送端,发送端校验后更新测试结果的报表信息。等所有调制模式遍历测试结束,查看最终报表,可知所遍历的模式全部成功。

通过将发送或接收端FPGA原型验证平台替换为协议电表模块,并将模块通过串口连到PC机,通过模块软件配置电表与平台之间以不同调制方式进行信标帧通信,查看串口上报的CRC校验结果来判断协议的一致性。

5 结 论

文中针对宽带电力线载波通信芯片的原型验证需求,介绍了一种FPGA原型验证平台,描述了基于此平台的FPGA开发流程及实现结果。通过载波通信物理层收发调制模式遍历的测试以及协议一致性测试,说明平台的调试方法达到预期目的。在芯片回片后,可将接收或发送平台之一替换为芯片基板,为芯片调试提供协助。多套平台还可连入电力线组网,为上层软件的早期调试提供载体。