具有GPS时间同步功能的高精度数字钟的设计

2020-12-03吕念芝肖志雄

吕念芝,肖志雄

(福州理工学院 工学院,福建 福州 350001)

GPS(global position system)是美国研制的导航、授时和定位系统。GPS时钟已成为世界上传授范围最广、精度最高的时间发布系统之一,GPS接收机接收到的GPS时钟与国际标准时间(UCT-universal co-ordinated time)保持高度同步[1-2]。

时间同步技术对于电力系统的正常运行和故障诊断都起着至关重要的作用。特别是在故障测距和继电保护等领域,时间和同步的精度将直接影响最后的分析结果[3]。

当前的数字钟普遍采用晶振时钟计数显示北京时间,存在较大的累计误差。时钟误差过大很难在对时钟精度高和稳定性要求高的电力系统中得到应用。为了解决普通时钟存在的低精度问题,采用FPGA技术,设计了具有高精度的数字钟,该方法可以消除晶振的累计误差,得到和GPS同步的时钟信息和高精度的秒脉冲。同时,该方法在一个芯片内完成,具有简单实用、体积小、功耗低的优点,具有较强的抗干扰性。该设计方案在以Altera的EP4CE6F17C8为核心器件的硬件平台上得到验证。

1 基于FPGA的整体实现方案

实现高精度的数字钟,需要提取出来GPS接收机发送出来的IRIG-B(DC)码中包含的时间信息,主要包含小时、分钟和秒信息,同时提取出高精度的秒脉冲信号。提取出来的时间信息再通过显示模块输出到对应的数码管。显示控制模块包含三部分:控制模块、扫描模块和译码模块。硬件中数码管采用共阳接法,动态显示数据。整体硬件功能示意图如图1所示。

图1 整体硬件功能示意图Fig.1 Overall hardware function diagram

2 FPGA的内部电路设计

在设计FPGA内部电路时,采用QuartusII12.0软件进行开发,使用超高速硬件描述语言(Verilog HDL)和原理图相结合的模块化设计。这种模块话设计不仅可读性强,也易于修改,提高了程序的设计效率[4]。

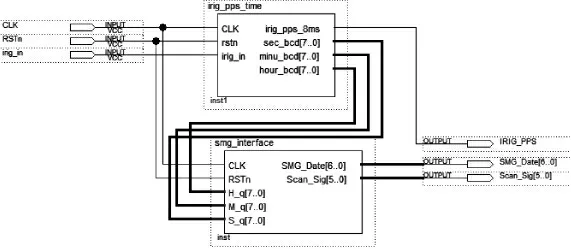

现场可编程逻辑器件FPGA芯片[5]内部的顶层电路如图2所示。顶层电路由irig_pps_time解码电路和smg_interface显示控制模块电路组成。图2中解码模块电路对输入的B(DC)码进行解码,识别和提取出时间信息和解调秒脉冲信号。解调出的秒脉冲信号直接作为输出信号。时间信号以BCD码的形式输出给控制显示模块使之当前时间能正确的显示在7段数码管上[6]。

图2 FPGA内部的顶层电路Fig.2 Top-level circuit in FPGA

2.1 解码模块

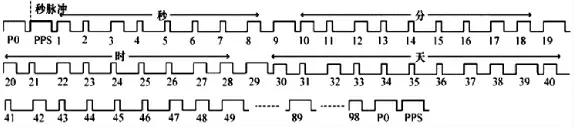

IRIG_B码(DC)共有3种码元,每一个码元占用10 ms的时间,逻辑“0”和逻辑“1”所对应码元的高电平分别为2和5 ms,P码元是位置码元,对应的高电平为8 ms的时间。B码为1 s传送1帧,每1帧所包含的时间信息如果3所示。在图3中,连续2个P码元为1帧的开始[7-8]。

图3 IRIG_B(DC)码每帧的信息Fig.3 Information per frame of IRIG_B(DC)

2.1.1 PPS秒脉冲提取

IRIG-B码的时帧周期是1 s,包含100个码元,每个码元周期为10 ms,因此需要生成1个脉冲clk_1k。此外还需要1个采集数据的脉冲(data_bit_clk),此脉冲周期也是1 ms。

data_bit_clk这个信号主要用在解码程序里面,一个时钟采集1个数据位(1 ms里面只采集1个数据)。

帧头的意义:irig_code是一个数据寄存器,每1 ms的时间里面存放1个采集到的数据,这样irig_code寄存器就会每个1个ms数据就会改变1次,当里面的数据是20’hFF3FC,表示帧头已经检测到了。

当第1次检测到帧头并配合解码脉冲(irig_code=20’hFF3FC&data_bit_clk),产生1个低989 ms高11 ms的脉冲(mask)。mask与irig_data_in与运算,产生的信号就是秒脉冲irig_pps。

2.1.2 时间解码

B码秒脉冲输入信号:irig_data_in,解码时间时钟:data_bit_clk。因为B码编码中0、1,P码即:每个码元宽度为10 ms,因此用irig_bit_cnt记录位的次数,周期是10。10个irig_bit_cnt构成1个码元,irig_slot_cnt记录码元个数。又因为每10个码元有1个位置识别标志,构成1个时隙,因此用irig_frame_cnt记录时隙的次数,周期是10,10个irig_frame_cnt构成1帧。

用sec_spl寄存器保存暂时的秒信息,这个寄存器是一个8位寄存器。高四位保存秒的个位信息,低四位保存秒的个位信息(都是BCD码表示)。秒信息是在第2个10 ms脉冲之后的第3、4、5、6和8、9、10个10 ms(码元)。

用minu_spl寄存器暂时保存分信息,这个寄存器是8位的。分的十位信息用高四位保存,分的个位信息用低四位保存。分的信息是B码的第11个码元开始,这个时候irig_frame_cnt=4'h1,即第2个100 ms时隙,在这个时隙里面,分的个位和十位信息包含在第2、3、4、5和7、8、9个10 ms(码元)。

用hour_spl这个寄存器暂时保存时信息,这也是一个8位的寄存器。时信息的个位信息是其低四位,高四位保存时的十位信息。时的低信息是在22、23、24、25和27、28个10 ms(码元)。

2.2 控制显示模块

控制显示模块包含3个子模块:数码管数据控制模块、数码管扫描模块、数码管显示译码模块,具体的FPGA电路如图4所示。

开发板上安装了6个共阳数码管,可以显示6个数字(从左往右依次显示小时、分钟、秒)。6个数码管的7段驱动信号是SMG_Date[6..0],分别对应数码管的g..a段。驱动信号是“低电平有效”。6个数码管的列扫描信号是Scan_Sig[5..0]。Scan_Sig[5]选择的是小时的十位,Scan_Sig[4]选择的是小时的个位,Scan_Sig[3]选择的是分钟的十位,Scan_Sig[2]选择的是分钟的个位,Scan_Sig[1]选择的是秒的十位,Scan_Sig[0]是秒的个位。分别对应的是来选择哪个数码管。

图4 FPGA控制显示模块Fig 4 .Control and display module of FPGA

3 设计仿真

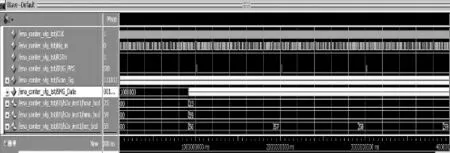

仿真测试平台是与quartusII 12.0[9]软件匹配的Modelsim,为加速仿真,在仿真过程中系统晶振频率设置为1 MHz(实际硬件平台频率为50 MHz)。irig_in设定为365 d,23 h,59 min,56、57、58、59 s。仿真长度为4 s,整体仿真结果如图5和图6。在图5中可以看到IRIG_PPS秒脉冲输出,同时解出对应时间分别为23:59:56、23:59:57、23:59:58和23:59:59。把图形放大可以看到SMG_Date[6..0]和Scan_Sig[5..0]对应的数值。图6是放大后的SMG_Date[6..0]和Scan_Sig[5..0]具体数值,此时解码时间为23:59:57。通过SMG_Date[6..0]和Scan_Sig[5..0]的数值此时数码管显示的正好是23:59:57。例如秒数值57,1 ms扫描信号Scan_Sig[1]=0(选择秒的十位数码管),SMG_Date[6..0]=0010010(数码管的驱动信号),1 ms扫描信号Scan_Sig[0]=0(选择秒的个位数码管),SMG_Date[6..0]=1111000(数码管的驱动信号)。仿真表明:解码电路设计正确且达到解码精度要求。

图5 FPGA整体仿真结果(1)Fig.5 The overall simulation results of FPGA(1)

图6 FPGA整体仿真结果(2)Fig.6 The overall simulation results of FPGA(2)

4 结论

通过IRIG_B(DC)码的解码和数据控制显示两方面详细介绍了基于FPGA技术的高精度数字钟的设计方案。该方案因为采用的是数码管显示,所以显示内容有限。后期可以通过液晶显示模块显示IRIG_B码中包含的跟多信息。比如:年、天数、是否闰年等信息。

仿真平台采用1 MHz时钟信号误差稍微高些,实际采用50 MHz的时钟信号,设计方案的总体延时小于300 ns。同时,该方案还输出高精度的秒脉冲信号,可以为其他设备提供需求。

随着数字同步网的建设,用户设备对标准时间信号的性能要求越来越高,本方案可以通过采用更高频率的主时钟信号和工作频率更高的FPGA芯片来满足用户设备不断提高的要求。