面向5G网络应用的精确时间同步协议测试与分析

2020-11-18李由由武建锋王康

李由由,武建锋,王康

(1.中国科学院国家授时中心,陕西 西安 710600;2.中国科学院大学,北京 100049)

0 引 言

5G网络正处在完善标准和培育产业化应用的时期,5G同步用于支撑5G网络和业务,包含频率同步与时间同步,频率同步要求与现有通信系统基本一致,但对时间同步提出了更加严格的要求.在4G时代,通常采用在基站加装卫星接收机的方式来满足通信系统对时间同步的需求,主要技术有卫星单频单向授时、卫星双向时间传递技术和卫星共视时间传递技术.在5G时代,若要通过卫星进行基站间的时间同步是不合适的.首先是5G具有密集组网的特点,基站距离短、密度大,如果每个基站都安装卫星接收机,会导致投资成本过大;其次5G室内基站占比将不断增大,出现卫星接收机获取不到信号的情况将越来越多.建设高精度的地面时间同步组网,在基站之间进行时间同步,逐步替代单一的基站卫星接收机授时方式,将有效解决上述问题.对于实现高精度的时间同步传输,由于精确时间同步协议(PTP)技术在电信网络中的大规模应用已经非常成熟,且易于实现互联互通,所以应在现有基础上对其进行优化.现有的PTP技术采用硬件时间戳的方式,同步精度可以达到亚微秒级,但无法满足5G时代对于时间同步的高精度要求,要发展具有更高精度的时间同步方法[1].

PTP协议的局限性在于频率分布效果差,只可保证绝对时刻信息的时间同步,但由于网络中各时钟自身的频率漂移及老化率特性不同,长时间导致钟差累积变大,最终失去同步.将同步以太网(SyncE)加入PTP技术中,利用时钟数据嵌入和恢复技术,实现频率的双向传递,可提高同步精度[2].WR(White Rabbit)协议又加入了全数字双混频鉴相器(DDMTD)技术,实现时钟主从端的相位测量和跟踪锁相,消除累积钟差,再次提升了同步精度,满足5G对高精度时间同步的要求.

本文提出了基于PTP+SyncE技术的两种方法,一种为基于DP83640芯片平台的方法,另一种为基于WR协议实现的方法,两种方法均达到了优于2 ns的同步精度,并给出了相应的试验分析.

1 面向网络的精确时间同步协议

PTP是针对分布式网络测控系统提出的精确时钟同步协议,基本原理是主钟周期性的发出同步信号校正同步所有网络节点的时钟,用软件实现精度较差,为微秒量级,用硬件实现可达纳秒级别;SyncE技术通过物理层实现时间频率分布,将主时钟的频率精确同步给网络中所有节点.基于PTP,依次将SyncE和DDMTD技术与之融合,成为具有更高精度的时间同步方法.

1.1 PTP同步原理

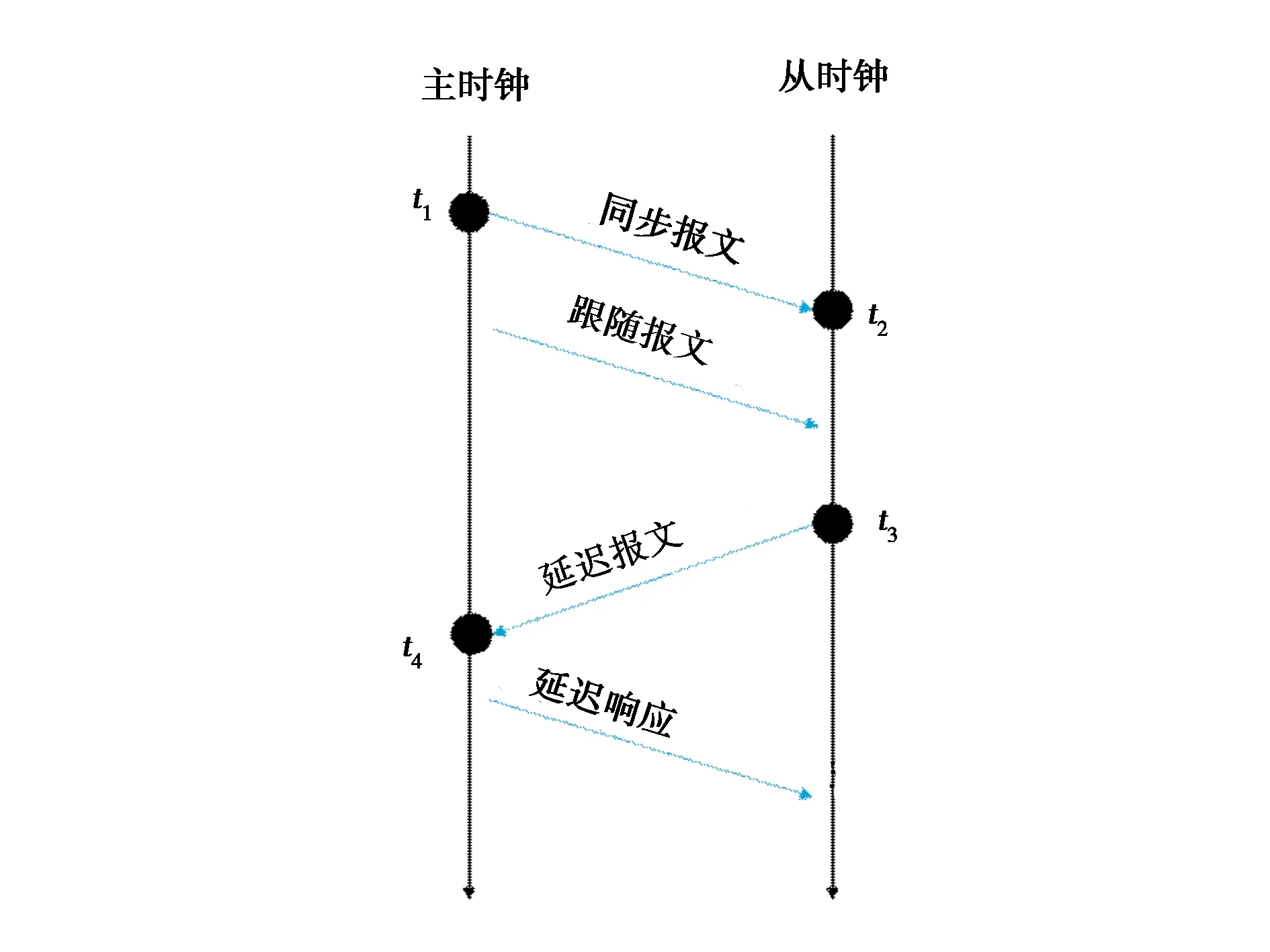

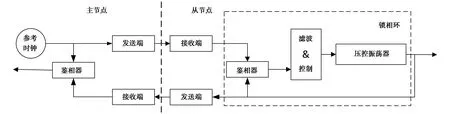

PTP协议把时钟分成主时钟和从时钟.主从时钟通过连续的交换报文发送与接收时刻的时间戳,然后根据同步算法对时钟计算偏差并进行自我调整,达到主从时钟同步的目的.PTP同步过程如图1所示.首先通过最佳时钟源算法确定区域内的主从时钟,然后二者周期性地交换带有时间戳的网络包[3].

图1 PTP同步过程原理图

t1时刻主钟发送同步报文(SYNE),将时间戳信息放在跟随报文(Follow-up)中,t2时刻从钟收到报文,t3时刻从钟发送延迟响应报文(Delay-request),主钟收到时刻记为t4,之后主钟再发送一个延迟响应(Delay-response),从时钟记录4个时间戳信息,根据PTP协议,可以计算出单向传输延时δMS=(t4-t3+t2-t1)/2,主从时钟偏移offsetMS=t1+σMS-t2,在计算出时钟偏差后进行调整[4].

1.2 SyncE+PTP同步原理

在SyncE中进行时钟分布,将编码后的时钟信号在物理层通过通信链路发送并同步到网络中的其他时钟节点.传统以太网通过时钟嵌入和恢复技术实现时钟同步,主钟在数据链路层中嵌入时钟和数据,从时钟的链路层通过恢复电路还原参考时钟,但还原后的时钟只在本级使用时钟信息,没有同步给下级时钟.因此,各级时钟之间没有相关性,他们是不同源的时钟.

不同于传统以太网,同步以太网全网基于来自主节点的高精度时钟源信息,所有节点构成一个可扩展的网络拓扑结构,子节点从数据链路中恢复出时钟,并通过节点内部的锁相环电路消除时钟恢复引起的抖动,然后将恢复出来的时钟作为本级时钟和下一级的参考时钟.采用SyncE技术实现物理同步的好处有很多:同步质量好,兼容现有同步网络;丢包、拥塞等网络问题不影响它的同步;技术成熟易实现[5].

SyncE虽然能很好地实现频率同步,但无法实现时间同步;PTP可以实现时间同步和相位同步,但实现时间同步时收敛时间长,同步报文交换频率过高导致通信链路负荷较大,同步精度受限于时间戳的精度,并且PTP报文经过复杂的数据网络引起的抖动不可控,同时没有考虑介质的非对称性,导致同步精度无法保证.

综合考虑这两种同步技术的优缺点,决定采用“PTP+SyncE”的联合方案,以SyncE为基础,实现PTP时间同步,这样避免了传输网络中频率同步收敛时间长的问题.此方案中,同步以太网实现频率同步,PTP实现时间和相位同步,PTP通过在硬件中插入和提取时间戳,同步精度得到提高,收敛时间进一步缩小.基于此联合方案,提出了WR和CuteNET技术方案.WR源于CERN欧洲核子中心同步应用,是基于以太网的扩展增强,实现亚纳秒级时间同步的技术;CuteNET技术,由国家授时中心自主研发,使用PTP+SyncE技术,实现亚纳秒级时间同步的技术.

1.3 PTP+SyncE+DDMTD同步原理

WR协议由三部分组成.SyncE利用时钟数据嵌入和时钟恢复技术,实现双向频率传递;网络精密时间同步协议(PTPv2)利用通信协议实现主从端延迟测量;DDMTD实现主从端相位测量和跟踪锁相.同时引入了同步链路的不对称估计.

1.3.1 时钟数据嵌入和时钟恢复

借鉴SyncE,WR利用时钟数据嵌入和时钟恢复技术实现频率源广播.主设备将时钟频率嵌入至链路层的数据码中,从设备的时钟恢复电路从链路层中恢复出参考时钟.所有设备的时钟来源于统一的稳定参考时钟(原子钟),逐级将时钟分布到所有连接的节点,使用专门的交换设备实现多个节点的扩展.相比较于基于DP83640的实现方案,增加了DDMTD实现更精确的相位测量.

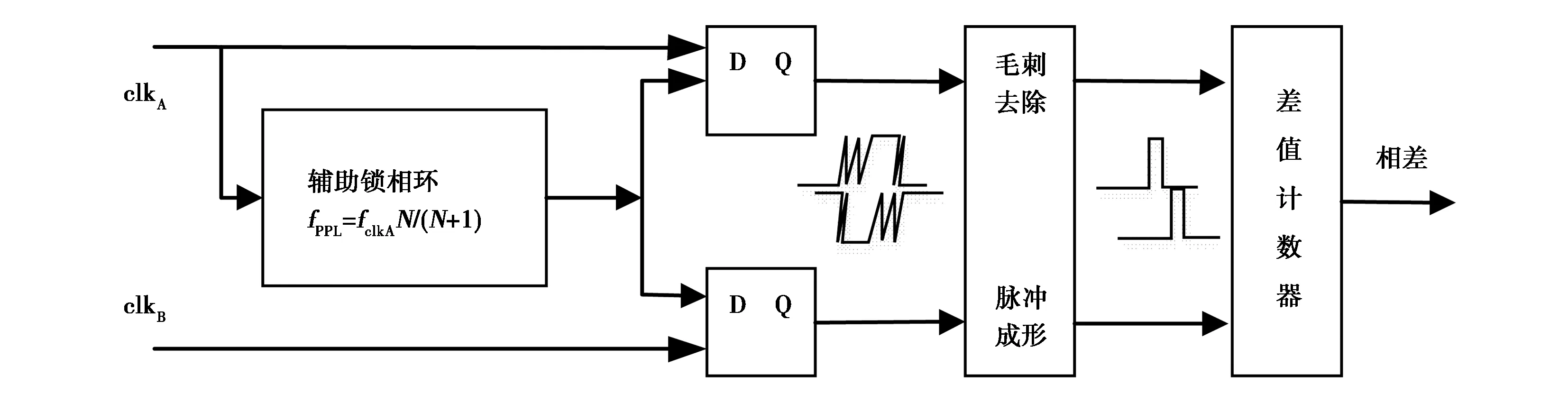

1.3.2 全数字双混频鉴相器

WR使用鉴相器精确测量数据恢复时钟与本地时钟的相位差并对时间戳进行校正,从节点的鉴相器与滤波控制电路以及压控振荡器构成了一个锁相环电路,实现从节点时钟的相位锁定和相位调整功能,从而将基于PTPv2的时钟同步技术带入亚纳秒级.

图2 数字双混频原理

工作原理如图2所示,利用外部锁相环产生一个辅助时钟信号,该信号频率与被测信号(clkA和clkB)的频率存在微小的差别(fPPL=N/(N+1)×fclk.在FPGA内部使用该辅助时钟信号分别对clkA和clkB进行采样.由于采样频率非常接近被测信号的频率,所以D触发器会输出一个非常低频的信号.被测信号的相位差在混频之后被放大,因此通过测量触发器输出信号的相位差可以计算出原信号的相位差,再通过锁相环实现相位跟踪和锁定的功能[6].

1.3.3 链路不对称估计

WR网络是基于千兆光纤以太网的同步网络,但PTP协议假定收发链路对称来计算同步时间偏差,未考虑因光纤收发采用不同波长而导致的收发时延不同,即忽略了收发链路的不对称性.WR协议定义了光纤非对称系数α,其为主端到从端光纤传播延时δMS与从端到主端光纤传播延时δSM的比值减1,即α=δMS/δSM-1,在构建同步链路前对α进行标定,实现对光纤非对称链路的补偿[7].

2 实验平台构建

2.1 PTP+SyncE平台构建

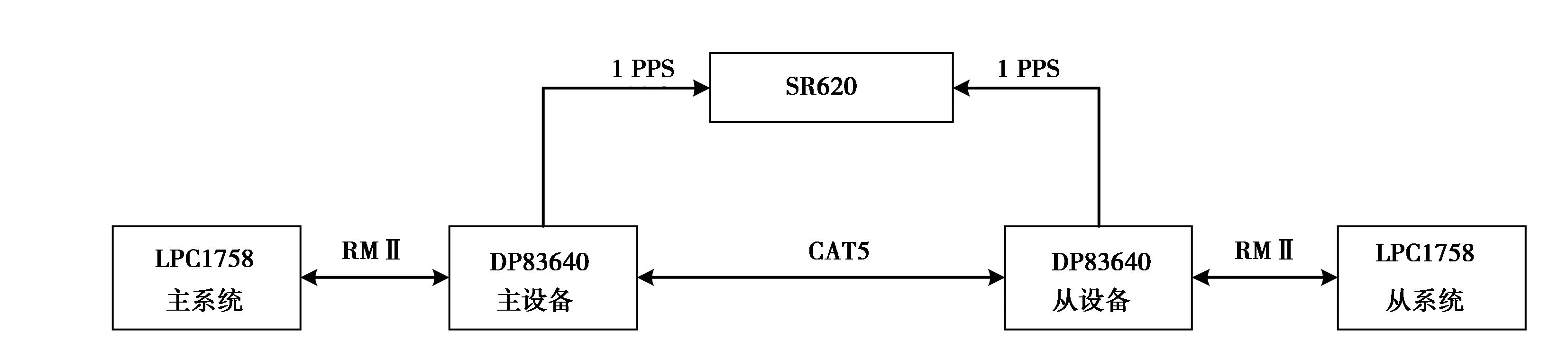

PTP+SyncE实验平台如图3所示,硬件部分由网络接口芯片DP83640和微处理芯片LPC1758组成,这两块芯片通过RMII主模式进行连接,微处理芯片负责PTP报文的收发,网络接口芯片主要功能模块有PHY以太网物理层接口、IEEE1588数据包检测与处理模块、IEEE1588控制和IEEE1588时钟.网络接口芯片负责对时间戳进行打戳,CPU通过读取网络接口芯片的内部寄存器,获得时间戳并记录下来,根据PTP协议处理时间戳得到主从时钟偏差和延迟[8].软件设计部分对PTP协议同步和UDP/IPv4网络协议进行实现,UDP协议把PTP报文作为协议的数据段来传递.实验时使用两块硬件平台点对点连接[9].

图3 实验平台结构

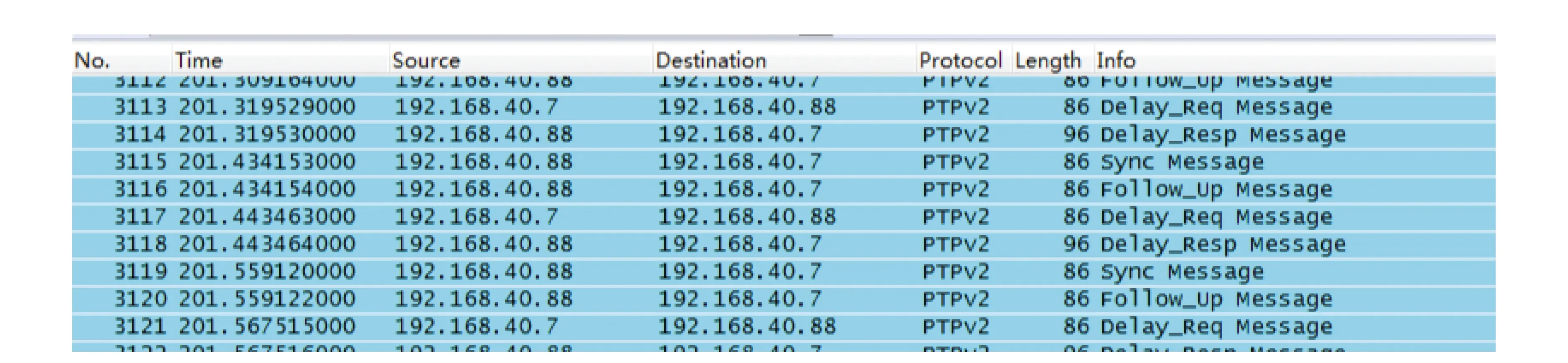

通过Wireshark软件捕获时钟模块与计算机之间传送的报文信息,以此来验证同步报文信息收发是否成功.如图4所示,设置主时钟的IP地址为192.168.40.88,设置从时钟的IP地址为192.168.40.7.由图4可以看出,能够正常地发送和接收同步报文,符合PTP标准规范要求.

图4 同步报文验证结果

2.2 WR平台构建

相较于DP83640平台,WR技术采用国外方案,搭建如图5所示的实验平台,使用两块Cute-WR-DP卡进行试验,此卡可以接收上一级时钟信息,也可作为主钟将时钟信息传递给下一级.将这两块板卡设置为主节点和从节点模式,主节点和从节点采用1 Gbps光纤收发器和波分复用的单模光纤连接,从节点通过收发端的以太网物理层数据时钟恢复技术和锁相环来恢复同步主节点的频率.鉴相器通过精确测量主从节点的相位差和校正时间戳,将同步精度提高到亚纳秒级别.

图5 WR实验平台

Cute-WR-DP提供了通用接口用于实现调试、数据通信以及本地配置等功能.WR在使用前需先标定参数.基于不对称系数构建的WR同步链路中需要标定的参数包括:主从端口固定收发时延、主从端光纤链路不对称系数α.其中,收发延时与设备本身和使用的光模块有关,在出厂时会进行标定,使用者也可试验测试,进行精确标定、更改参数;α系数在精度要求不高的时候可用默认参数,也可根据不同设备进行测试,自己标定[10].

3 测试与分析

3.1 PTP+SyncE同步精度测试

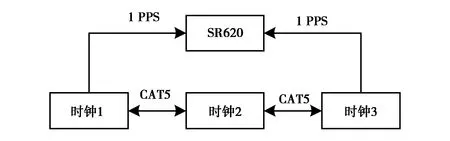

测试使用了3个时钟模块,利用网线连接,分别进行了两个时钟直连的双节点同步精度测试和三个模块串联的一、三时钟同步精度测试.

3.1.1 双时钟模块同步精度

为了测量主从时钟的时间同步偏差,搭建了如图6所示的同步精度验证系统.主从时钟模块通过RMII接口将LPC1758主系统与DP83640设备连接构成,通过50 m网线进行通信、同步连接.将主从设备分别产生的秒脉冲(1 PPS)信号输入到SR620时间间隔计数器里.输出的秒脉冲高电平均为3.3 V,故SR620触发电平设为1.5,无50 Ω负载.

图6 两时钟同步精度

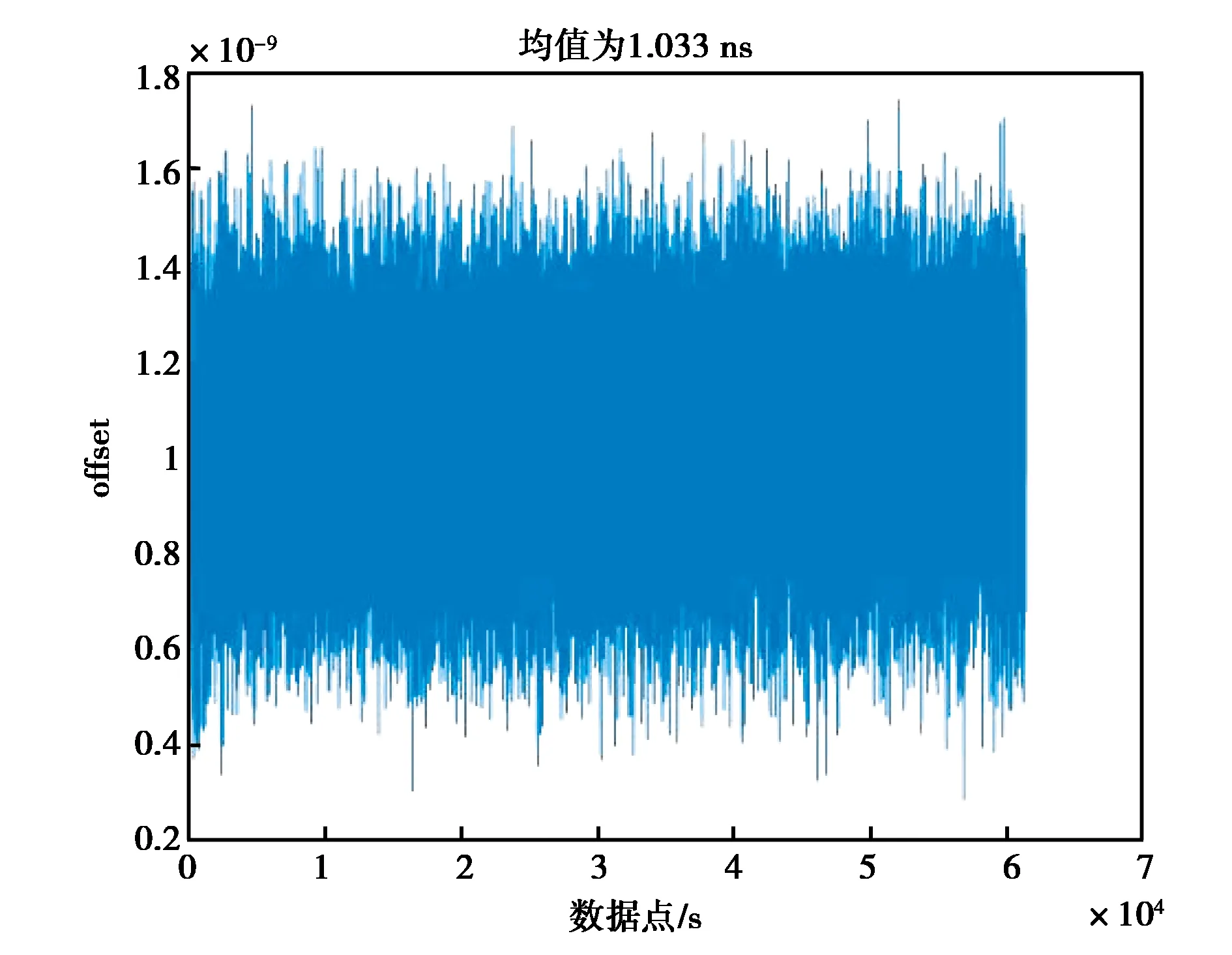

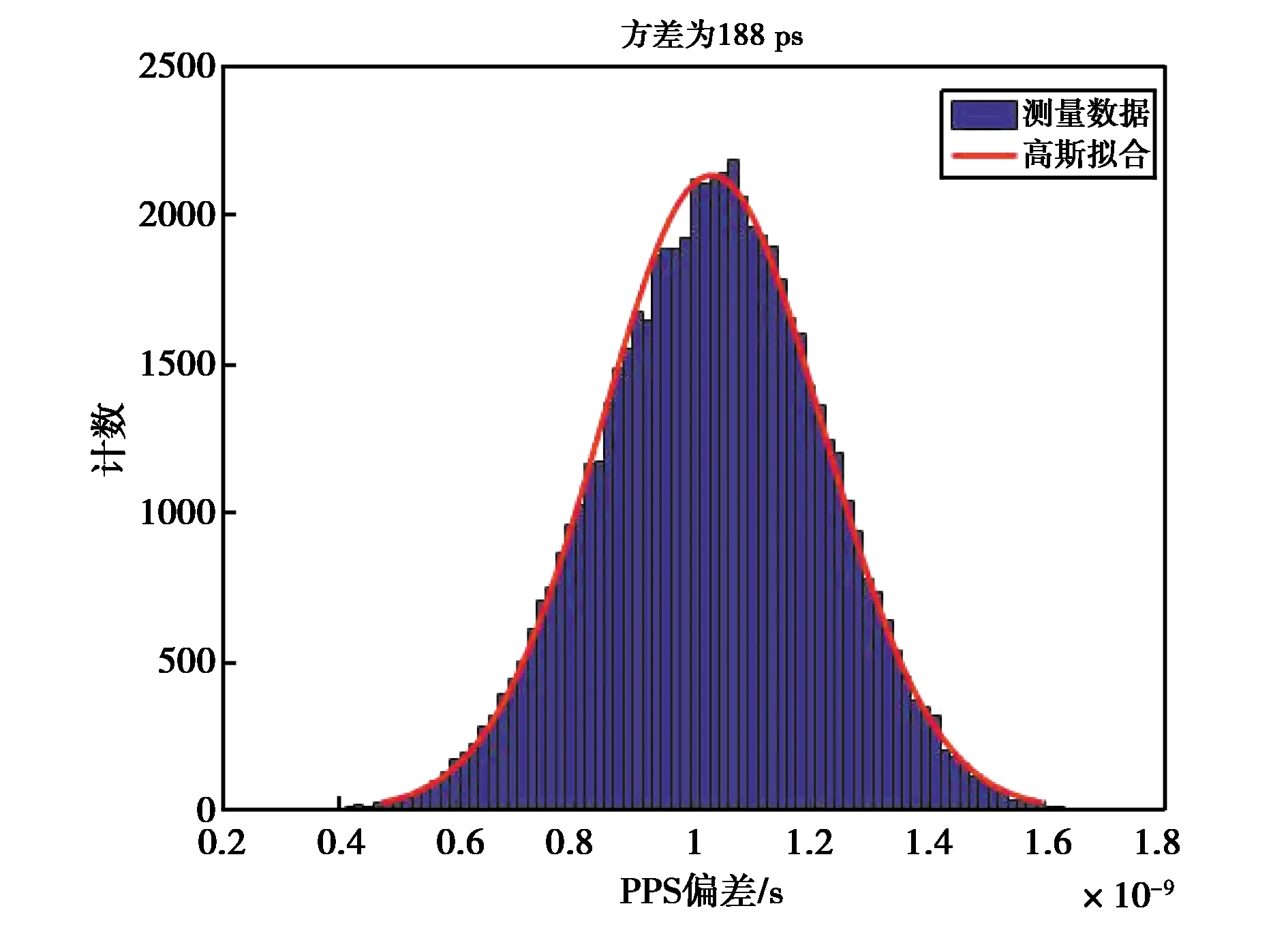

用Matlab对18个小时的测试数据进行分析处理,得到时间偏差的均值为1.033 ns,方差为188 ps,无异常野值.如图7、8所示.

图7 测试时间分布点图

图8 测试直方图

3.1.2 串联时钟模块同步精度

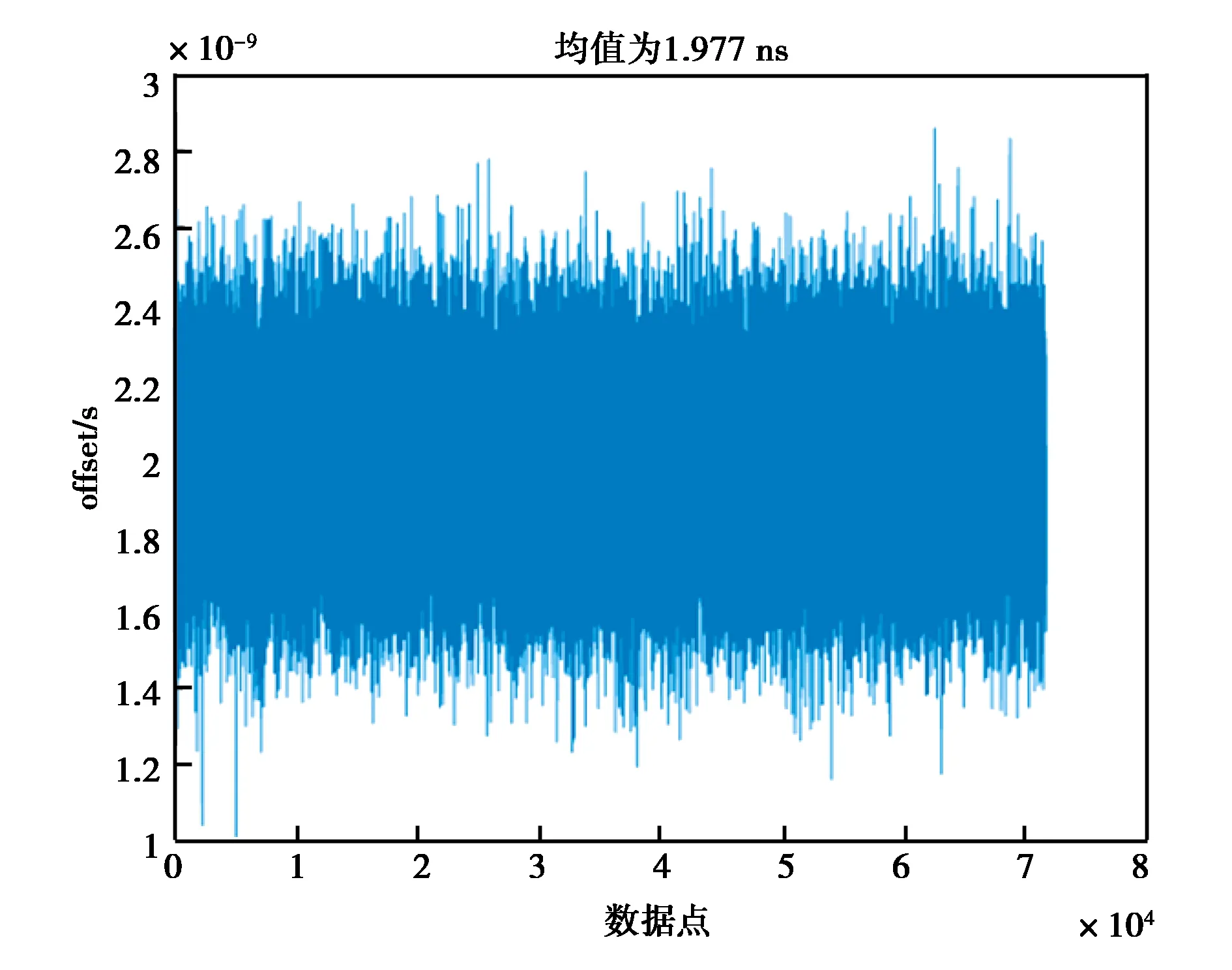

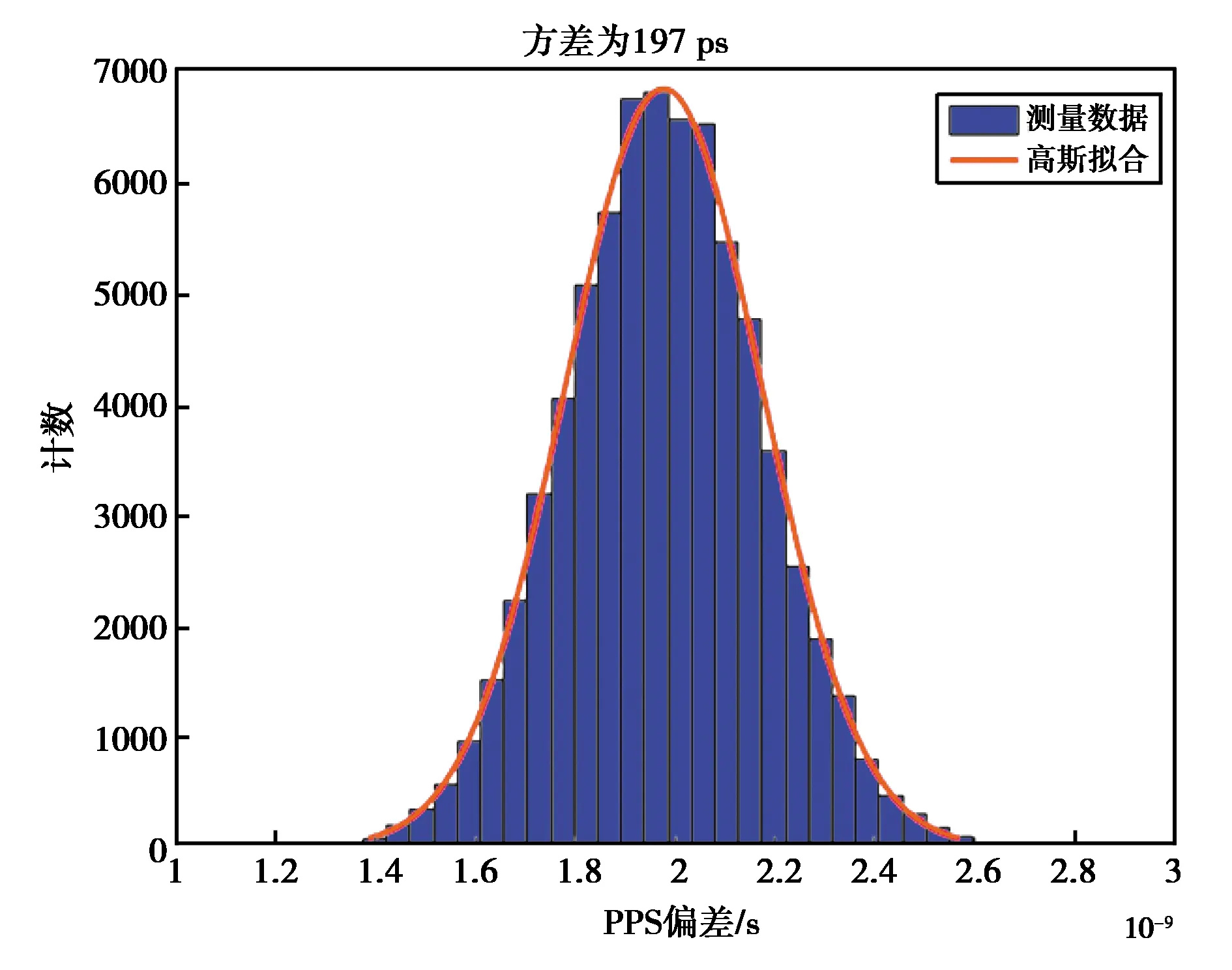

时钟模块组成三级串联拓扑结构,测试连接原理如图9所示.在和双时钟模块同步精度测量条件相同的情况下,测量结果如图10、11所示.通过Matlab数据分析,均值为1.977 ns,方差为197 ps,无异常野值.测试结果表明通过PTP+SyncE这种方法,可稳定实现优于2 ns的准确度和百皮秒的稳定度.由于频率需要经过二次恢复,与时间源的偏差加大,最终导致时间偏差加大.

图9 串联时钟模块同步精度

图10 测试时间分布点图

图11 测试直方图

3.2 WR同步精度验证

测试使用了3块Cute-WR-DP卡,利用单模复用光纤连接板卡,分别进行了两个板卡直连的双节点同步精度测试和三个板卡串联的一三节点同步精度测试.

3.2.1 双节点同步精度

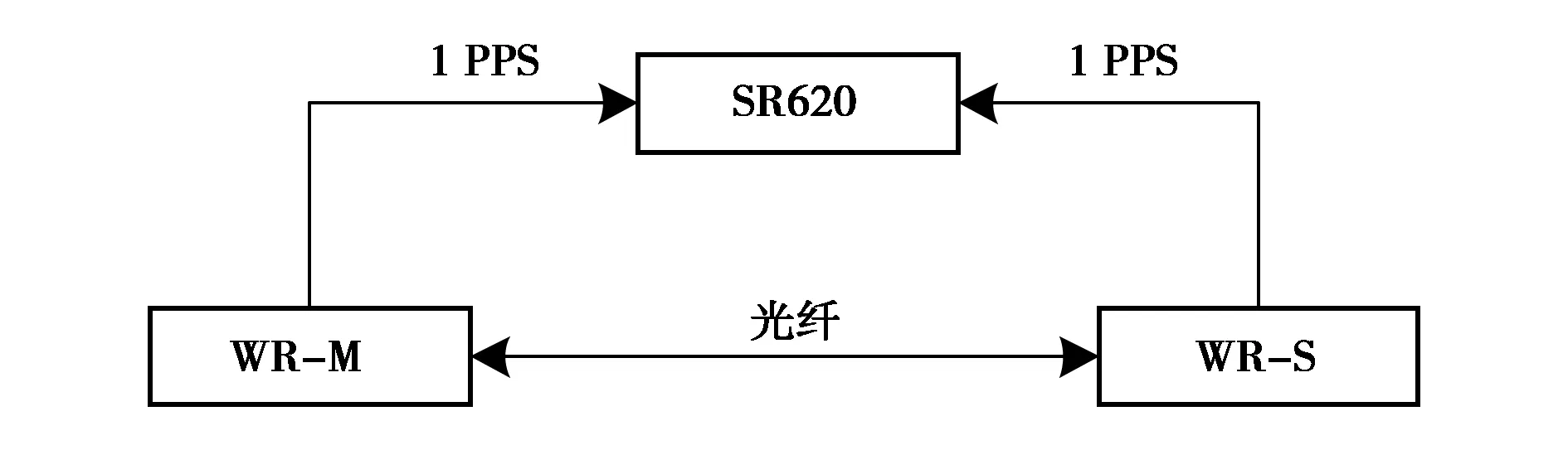

使用Cute-WR-DP卡作为WR节点通过单模复用光纤相连,分为主从节点,通过输出的秒脉冲信号测试其时间同步的不确定度,测试连接原理图如图12所示.

图12 WR双节点测试连接原理图

WR-M为主时钟,内部有晶振,可以产生固定频率,与WR-S从时钟通过单模复用光纤相连,主时钟光模块发出的光波长为1490 nm,从时钟光模块发出的光波长为1310 nm.二者同时输出秒脉冲(1 PPS)信号连接到计数器,即可测得二者之间的时间同步的不确定度.计数器的触发电平设置为1.5 V,计数器A口接主端,计数器B口接从端,都没有加50 Ω的负载.使用50 m光纤进行连接.测试结果如图13、14所示.

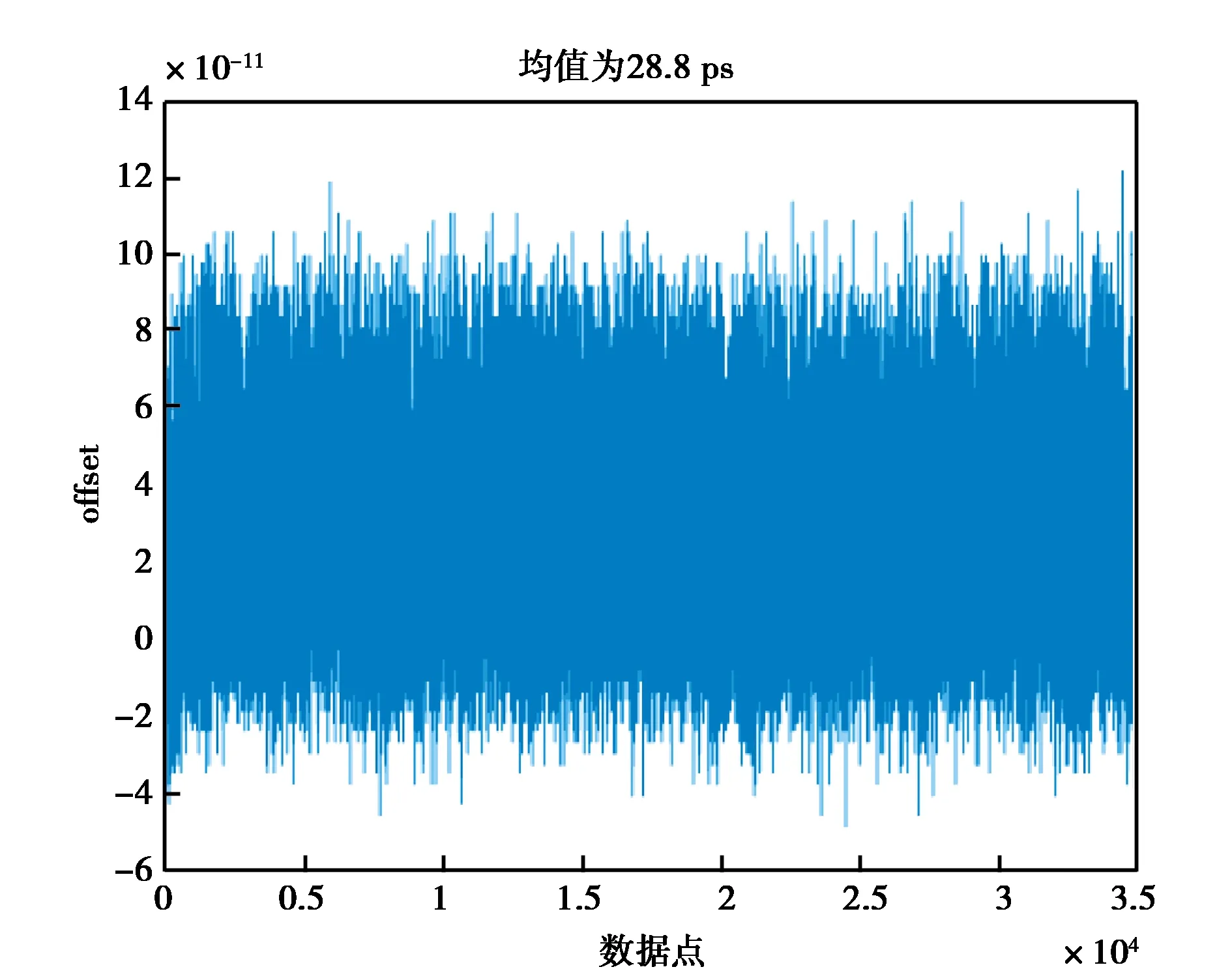

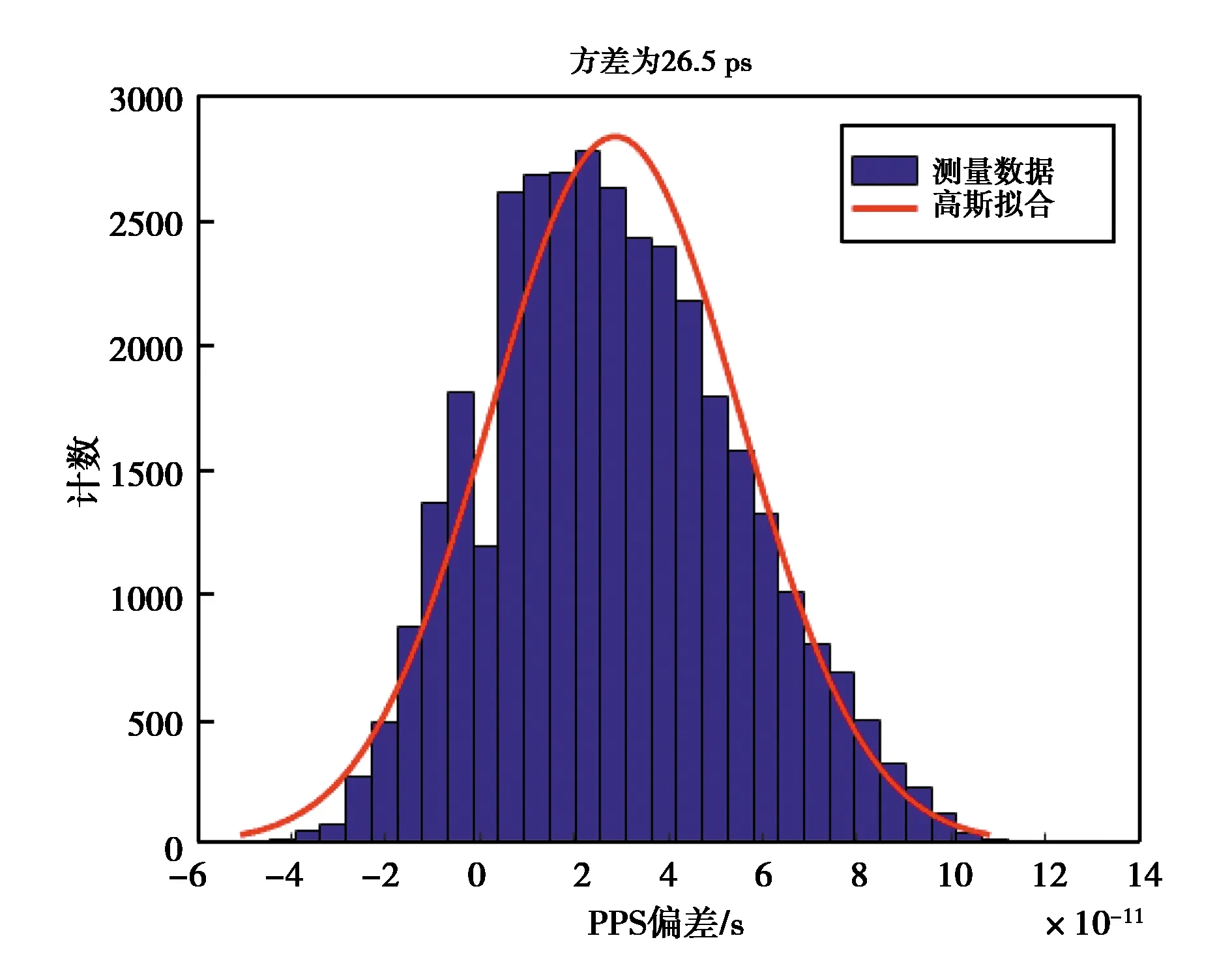

经过测试,通过Matlab数据分析,均值为28.8 ps,方差为26.5 ps,无异常野值.由于SR620计数器的精度为25 ps,当用其测得的时间偏差为28.8 ps的时候,测量结果误差在±25 ps.

图13测试时间分布点图

图14 测试直方图

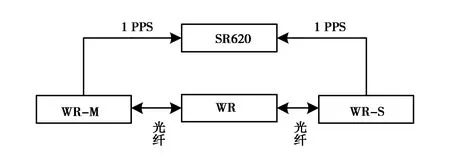

3.2.2 串联节点同步精度

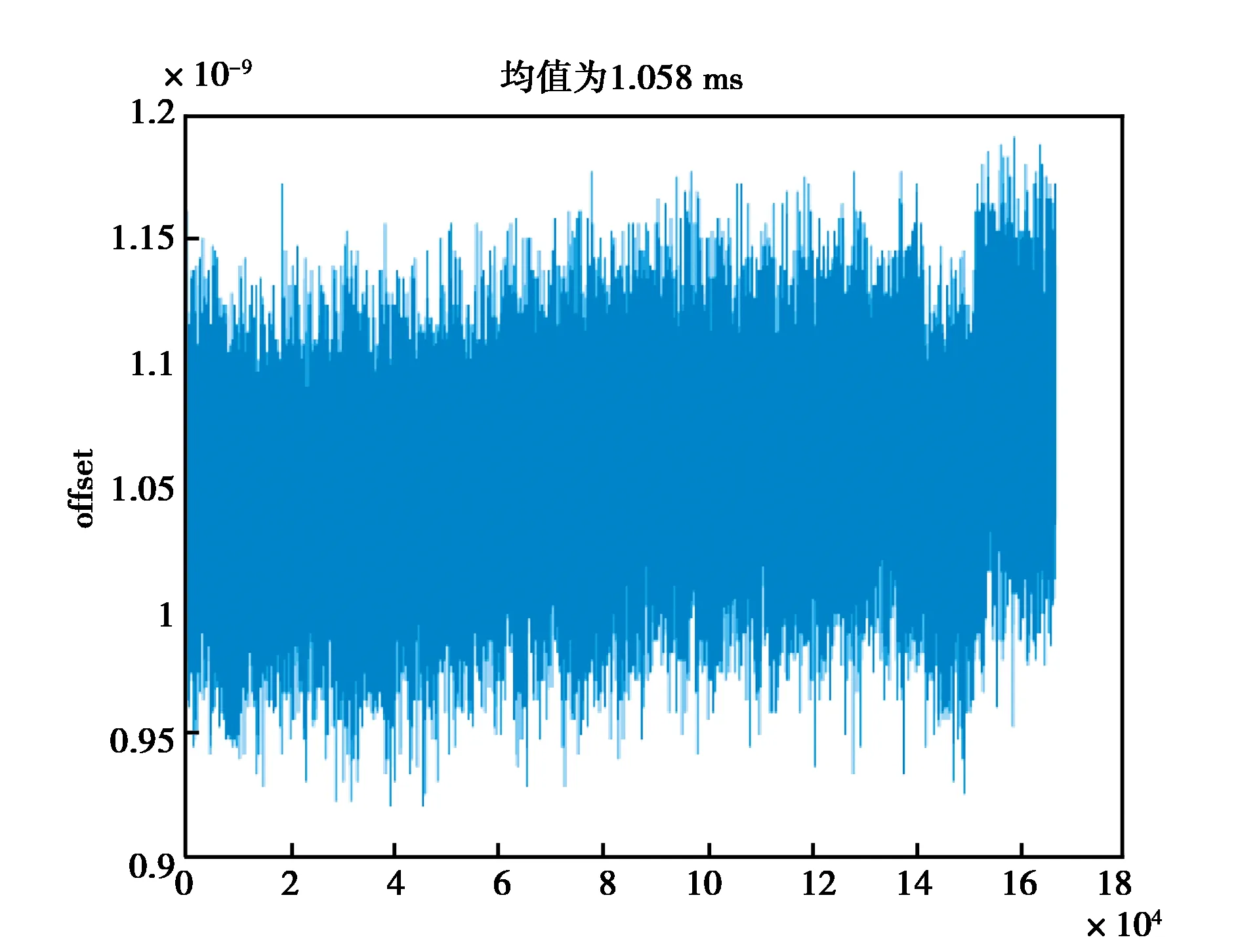

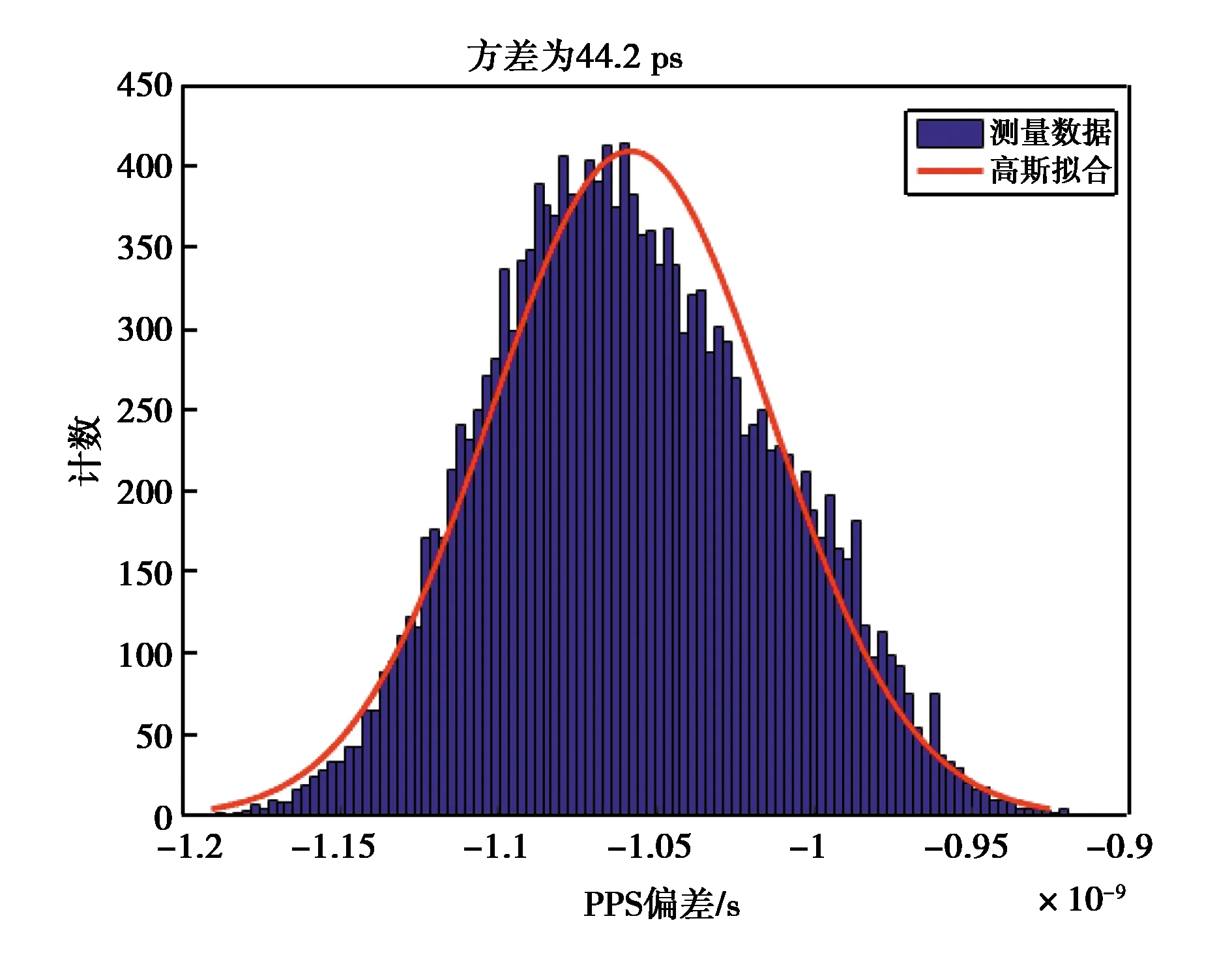

板卡组成三级串联拓扑结构,测试连接原理如图15所示.在和双节点同步精度测量条件相同的情况下,测量结果如图16~17所示.通过Matlab数据分析,均值为1.058 ns,方差为44.2 ps,无异常野值.说明通过WR也可以稳定地达到百皮秒的抖动,优于2 ns的准确度.可以发现,通过串联之后,同步精度有略微下降,是因为经过两次数据恢复,相差累积所致.

图15 WR三节点测试连接原理图

图16 测试时间分布点图

图17 测试直方图

4 结 语

通过两种方案的测试及比较,两种方案都可以取得优于2 ns的同步准确度.5G背景下,这两种方案都能满足高精度的时间同步要求,但各有优缺点.WR方案由于采用了双混频时差测量技术,能够取得较PTP+SyncE方案更好的抖动特性以及同步精度,正由于WR方案增加了双混频时差测量功能,导致构造复杂,成本增高,并且使用前需要进行预校准.PTP技术目前在电信网络中应用广泛、成熟度高、互联互通性好,在其基础上改进的PTP+SyncE方案易于实现,更适合作为基站间时间同步的传递技术.