基于CMOS电路的序列信号检测器的设计

2020-08-24保慧琴

保慧琴,李 茹,卫 霞

(西北工业大学明德学院信息工程学院,西安710124)

1 引言

序列信号检测器作为一种时序数字电路中最常用到的设计之一,可以从串行的数字码流中识别出一个指定的序列,因此在雷达、遥测、密码认证等领域中有广泛的应用。随着集成电路的快速发展,互补CMOS电路在集成电路中的应用占了98%以上。静态CMOS逻辑结构包含NMOS逻辑块和PMOS逻辑块,两者互补,因此在输入稳态时两个逻辑块轮流导通,电源和地之间没有直流通路,静态功耗几乎为0。同时,静态CMOS逻辑也是一种无比电路,摆幅可以达到-VDD[1]。

基于静态CMOS逻辑电路,在此设计一款“1111”序列信号检测器,其输入X为串行二进制数,当串行输入数据中连续出现四个“1”时,使其输出Z为1。

2 检测器设计

首先建立原始的状态转换图。“1111”序列信号检测器一共需要5个状态:S0代表接收到0以后的状态;S1代表接收到1个1以后的状态;S2代表接收到2个1以后的状态;S3代表接收到3个1以后的状态;S4代表接收到4个1以后的状态。原始状态转换图和状态转换表如图1、表1所示。

图1状态转换图

表1状态转换表 yn+1/Z

不论状态处在S0~S4的哪个状态,当输入为0时状态都会跳转回到S0状态,输出为0;S0是接收0以后的状态,如果输入为1,则状态跳转到S1状态,输出为0;S1是接收1个1以后的状态,如果输入为1,则状态跳转到S2,输出为0;S2是接收2个1以后的状态,如果输入为1,则状态跳转到S3,输出为0;S3是接收3个1以后的状态,如果输入为1则状态跳转到S4,输出为1;S4是接收到4个1的状态,如果输入为1则状态停留在S4,输出为1。观察表1可以发现,S3和S4这两个状态,在相同的输入作用下,有相同的输出,而且转换到相同的输出,所以S3和S4这两个状态是等价状态,可以合并为一个状态[2],从而将状态转换图和状态转换表简化为图2和表2所示。

图2简化后的状态转换图

表2简化后的状态转换表yn+1/Z

时序逻辑电路的状态是用触发器状态的不同组合来表示的,因此需要确定触发器的级数n。n个触发器一共有2n个状态组合,要获得M个状态组合,必须取2n<M≤2n。本设计中状态个数为4,所以需要2个触发器即可。2个触发器一共有00、01、10和11四个状态,需要将这四个状态进行状态分配。状态分配的原则有二,一是要使得最后的逻辑图最简,二是多余状态不产生死循环。因为设计中没有多余状态,所以不需要考虑死循环的问题,为便于按照顺序进行状态分配,令S0=00,S1=01,S2=10,S3=11。将表2中的字母形式的状态变换为二进制形式,即得到新的状态转换表,如表3。状态转换表表示触发器在外边输入作用下的状态和输出。状态转换的真值表如表4。

表3二进制形式的状态转换表

表4状态转换真值表

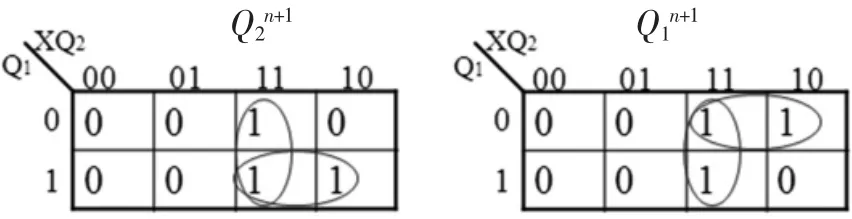

将输出Q2n+1、Q1n+1放到卡诺图中进行化简,简化过程如图3所示。输出Z不需要用卡诺图进行化简,因为输出Z逻辑值为1的最小项只有一个,即Z=XQ2Q1。

图3使用卡诺图进行化简

此处2个触发器选择边沿D触发器,D触发器的特征方程[3]为Qn+1=D,卡诺图化简的结果就是D触发器的输入激励表达式,即:

求出2个边沿D触发器的输入激励方程后,将2个触发器连接成同步时序逻辑电路即可。此处选用集成电路设计软件Tanner_Pro中的S-edit设计序列信号检测器的电路原理图并用T-spice进行仿真验证。

3 CMOS电路原理图设计

采用静态CMOS逻辑电路设计“1111”序列信号检测器,静态CMOS逻辑中NMOS逻辑块(下拉网络,PDN)和PMOS逻辑块(上拉网络,PUN)具有互补性能,输入为稳态时静态CMOS逻辑门电源和地之间没有直流通路,静态功耗几乎为0。静态CMOS逻辑门由于总是实现带“非”的逻辑,所以需要将触发器的激励表达式以及输出表达式变形为带“非”的形式[4],即:

逻辑表达式的变换方法很多,此处选择变换方式要考虑尽可能多地应用到公共项,上面三个输出的逻辑表达式中都存在这个公共项,可以节省硬件资源。从前面公式可以判断出“1111”序列信号检测器需要用到的逻辑门有三种:CMOS两输入或非门、CMOS两输入与非门和边沿D触发器。

3.1 CMOS两输入或非门设计

为避免体硅工艺中的闩锁效应,静态CMOS逻辑门中NMOS管和PMOS管的衬底要进行固定的连接。NMOS管的衬底必须接地,PMOS管的衬底必须接电源电压。静态CMOS逻辑门当输入是稳态时只有单逻辑块导通,没有直通电路,静态功耗几乎为0。CMOS或非门是一种无比电路,所以其输出逻辑摆幅最大可以达到最大VDD。CMOS两输入或非门电路图和仿真波形如图4。

图4 CMOS或非门电路图和仿真波形

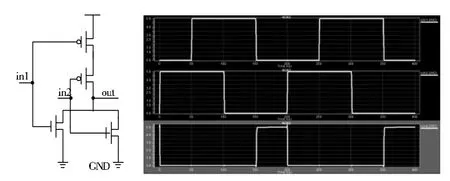

3.2 CMOS两输入与非门设计

CMOS两输入与非门中NMOS逻辑块由两个串联的NMOS构成,串联晶体管会使得输出下降时间变长,性能变差,因此串联晶体管的数目一般不能超过3个。PMOS逻辑块由两个并联的PMOS管构成,并联的晶体管会增加负载电容。在设计两输入与非门时应设计好尺寸使之达到对性能的要求[5]。两输入与非门电路原理图和仿真波形如图5。

图5两输入与非门电路原理图和仿真波形

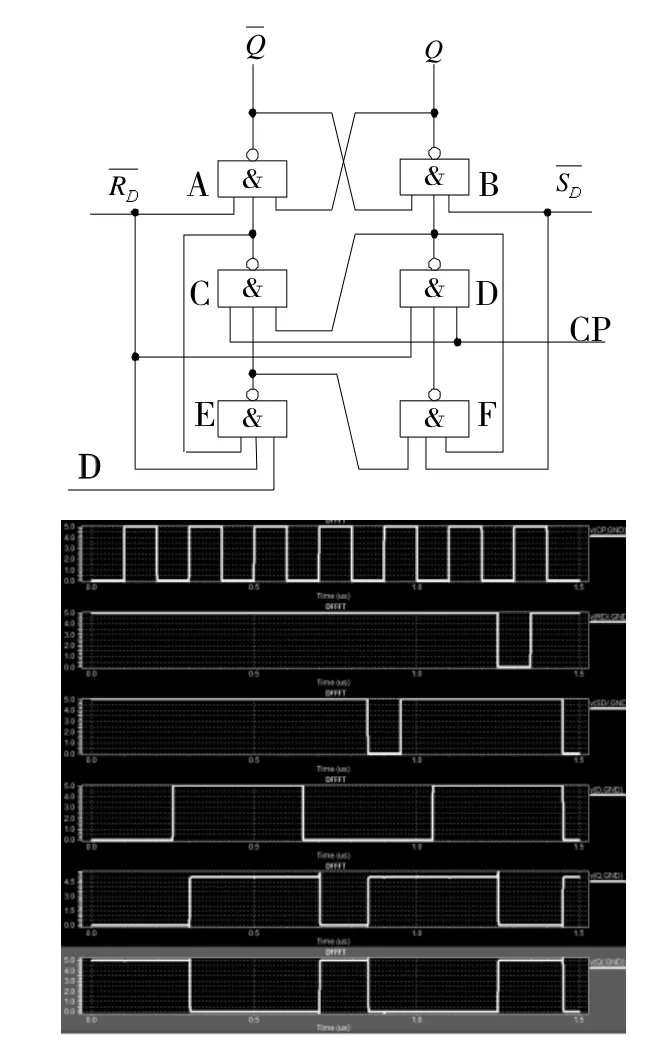

3.3 边沿D触发器设计

为提高抗干扰能力和电路工作可靠性,选用上升沿触发的边沿D触发器,此触发器也具有异步清零功能和异步置位功能。采用静态CMOS逻辑门实现边沿D触发器,由6个CMOS三输入与非门交叉耦合而成。电路原理图及仿真结果波形如图6所示。波形信号从上到下依次为时钟CP、异步清零端口RD、异步置1端口SD、输入D和输出Q和Q。从波形中可以看出,异步清零端口RD为低电平时触发器清零,异步置1端口SD为0时触发器置1,异步清零和异步置1端口都为高电平时,D触发器状态只在CP上升沿时刻才跟随输入D发生变化,其他时刻输入信号的变化不会引起触发器的状态变化。

图6边沿D触发器电路原理图和仿真波形

3.4 序列信号检测器设计

“1111”序列信号检测器由两个边沿D触发器、CMOS或非门和CMOS两输入与非门组成。采用层次化的设计思想,将设计出的边沿D触发器单元、或非门单元和两输入与非门单元进行级联,形成序列信号检测器的电路原理图[6],如图7所示,它是在Tanner_Pro集成电路设计软件中的S-edit电路编辑软件中设计出的电路原理图,然后用T-spice软件进行瞬时分析[7-8]。

图7“1111”序列信号检测器电路原理图

在T-spice中设置两个D触发器的初始状态为0,仿真波形如图8所示。可以看出,从第一个时钟上升沿开始触发器状态Q2Q1转换过程为00→01→10→11,也就是S0→S1→S2→S3。后面X继续输入1时,触发器状态保持Q2Q1=11也就是保持在S3状态。输入有连续4个1出现时输出Z为1,当输入X有0出现时触发器的状态返回S0,输出Z立刻置0。

图8“1111”序列信号检测器仿真波形图

4 结束语

所设计的此款“1111”序列信号检测器可直接应用在雷达、遥测、通信系统等领域。Tanner_Pro是一整套完善的集成电路设计软件,采用模块化、层次化的设计思想,利用该软件中的S-edit,设计出了“1111”序列信号检测器的电路原理图;电路结构选用静态CMOS逻辑结构,也提高了电路的性能。以T-spice进行仿真验证,所设计的序列信号检测器可以从串行的数字码流中识别出一个指定的序列,满足设计预期。