时频系统数字锁相技术研究

2019-12-05王鹏宇杨志刚郑丽丽

王鹏宇 杨志刚 郑丽丽

(中国电子科技集团公司第二十七研究所,河南郑州 450047)

1 引 言

随着航天测控系统的发展,测量设备对频率标准的精度(准确度)和稳定度要求越来越高。通常情况下基于单一铷钟频率源的频标基准,其准确度指标很高,但短期稳定度一般不高;而基于单一晶振频率源的频标基准,虽然能够达到很好的短期稳定度,但准确度又不高。为全面提高频标基准的长短期稳定度指标,目前一般采用基于GPS驯服、锁相技术的解决方案。

锁相环的设计主要考虑稳定性、带宽和噪声性能[1,2]。频标基准最早采用的是模拟锁相环,由本振跟踪外参考频率信号。模拟锁相环的特点是成熟、可靠性好、锁定速度快;但参数设置不灵活,分析困难,一致性较差,不能跟踪1PPS时间基准信号。

随着卫星导航系统的出现,上世纪90年代初提出了利用卫星导航系统提供的1PPS时间基准信号驯服本地频率源的方案,这样可以使本地时统设备的1PPS精度和10MHz信号的长期稳定度溯源到卫星导航系统的时间基准上。本文即讨论外部1PPS或10MHz频率信号驯服铷钟或晶振的数字二阶/三阶锁相环结构,建立了频标模块的仿真模型,给出了参数设置依据、仿真及硬件测试结果,验证了模型的正确性。

2 频标模块模型

时频系统中的频标模块结构如图1所示,其主要功能是对外提供具有高精度和高稳定度的10MHz频率信号和1PPS时间基准信号。当指标要求不是很高时,也可由GPS/BD(北斗)的1PPS信号直接驯服晶振,如图1中虚线所示。

图1 频标模块结构组成框图Fig.1 Frequency standard component structure

数字锁相环主要利用1PPS脉冲进行鉴相(10MHz信号可分频出1PPS脉冲),因此以1s时间间隔作为相位2π,环路中用待驯服铷钟/晶振等频率源倍频至f0后分出1PPS与参考输入1PPS之间的时间差进行采样,所以,相位差Δφ与采样计数N及f0之间的关系为

(1)

而相位差也可以用时间差来表示为

(2)

频标模块的仿真模型如图2所示。

图2 频标模块仿真模型组成框图Fig.2 Frequency standard component simulation model

2.1 待驯服频率源模型

待驯服频率源建模主要考虑的是自身噪声和老化率。以高稳晶振为例,若10MHz晶振秒稳优于5E-13,相当于频率稳定度标准差最大为5E-6Hz,即频率变为10 000 000.000 005Hz,换算成秒时间周期为0.999 999 999 999 5s,变化了5E-04ns,即可以将晶振建模为标准差为5E-04ns相位累加器。

晶振的老化率为[3]

(3)

式中:fx(t)——被测频率的瞬时值;fr(t)——参考频率的瞬时值;fx0——两者频率的标称值;τ——平均时间。

为了便于仿真,令

fr(t)=fx0

且

fx(t)>fr(t)

所以,若按晶振日老化率为1×10-10/d,则有

即

fx(t)-fx0=fx0×10-10/(3 600×24)Hz/s

若晶振标称频率为10MHz,则可得本振相位变化率为

107×10-10×2π/(3 600×24)=7.272 2E-8rad/s

2.2 GPS/BD 1PPS信号模型

假设GPS/BD接收机的授时精度优于20ns(1σ),则输入1PPS信号相位抖动的标准差为1.256 6E-7rad。设环路启动初始时间差500ns,即相位差3.141 6E-6rad。

2.3 锁相环结构

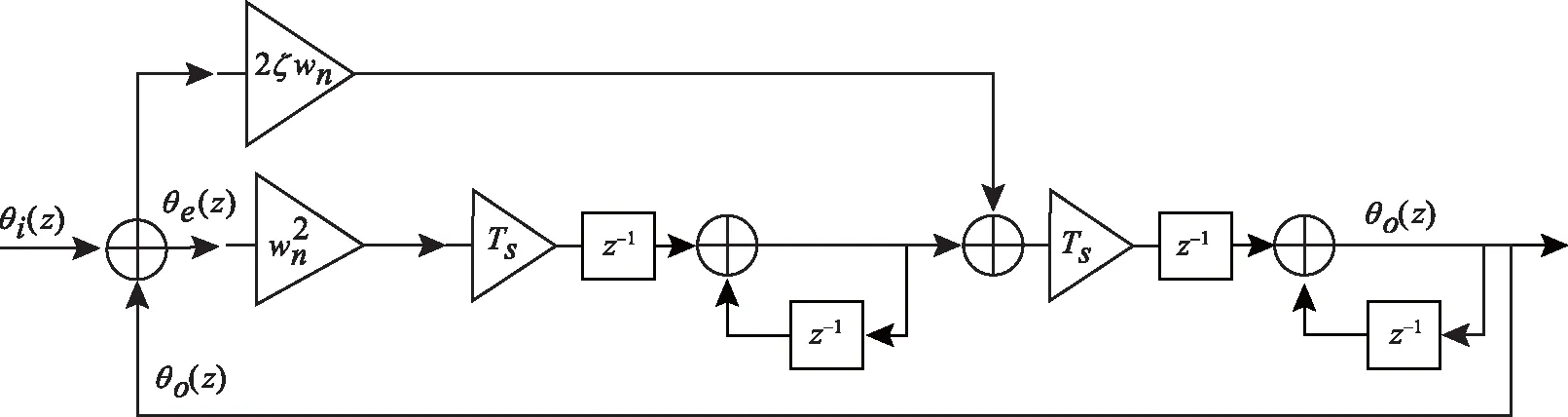

当系统采样率ws达到ws>10wc(wc为穿越频率)时,数字锁相环可以由一个模拟锁相环通过同步采样来获得[4]。经过推导,二阶锁相环的数字化结构如图3所示。

图3 二阶数字锁相环示意图Fig.3 2 order digital PLL

图3中,θi(z)为输入相位,θo(z)为本振输出相位,θe(z)为相位差,它们的单位均为弧度。ζ和wn是二阶控制系统的固有频率和阻尼,Ts为环路更新周期。二阶锁相环的等效噪声带宽BL可以表示为

(4)

式(4)中,wn的单位为rad/s,而BL的单位为Hz。综合考虑环路动态性和响应时间,一般ζ取0.707,因此二阶环路的可控参数只有环路带宽BL。又因为ws>10wc,可导出ws>30BL,即

(5)

式(5)给出了频标模块锁相环噪声带宽的上限。

频标模块的主要任务是对外提供高精度1PPS信号,通常要与GPS/BD接收机给出的1PPS信号一致。而当环路带宽较窄时,由于晶振老化率的影响,造成二阶环路锁定后的鉴相输出不为零,即本振输出1PPS信号与参考输入1PPS信号的相位不一致。此时可以采用三阶锁相环,如图4所示[5,6]。

图4 三阶数字锁相环Fig.4 3 order digital PLL

图4中,环路增益k′1,k′2,k′3由式(6)确定

k′1=(k+2)ζwn

(6)

考虑到环路稳定性,需满足k>0,ζ>0.25。而为了使环路动态性能可以由二阶系统近似,要求k>5。当k=6时,可以得到BL与ζ,wn之间的简单关系。此时,BL可以由式(7)近似估算

BL=(2.037ζ+0.1036)wn(ζ>0.2)

(7)

当ζ=0.707时,三阶环路性能也可以只通过环路带宽BL来控制。

开环、二阶环路、三阶环路时本振相位输出与外参考信号对比如图5所示。可见晶振的老化使得其输出相位与参考相比向一个方向不断偏移;二阶环路可以让本振输出相位跟随外参考,但存在固定相差;当采用三阶环路后,本振输出相位跟随外参考,且不存在固定相差。

图5 开环、二阶环路、三阶环路本振相位输出与外参考信号对比Fig.5 Local oscillator ouput compared with reference output when open loop,2order/3order pll loop

3 仿真分析

3.1 数字环路仿真分析

3.1.1鉴相器量化

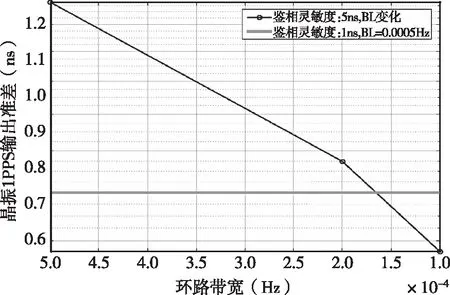

鉴相器量化采用环路中用待驯服频率源对其分频后1PPS与参考输入1PPS之间的时间差进行采样的方式。不同量化灵敏度对于环路性能的影响如图6所示。

图6 量化灵敏度对于环路性能的影响曲线图Fig.6 The effect on the pll performance by phase detector quantization

从图6可以看出,鉴相器量化程度越高对提高环路性能越有利,将10MHz待驯服信号倍频至1GHz对时间差进行采样的环路性能要远远好于利用倍频至50MHz信号进行采样。然而在FPGA内部实现1GHz的信号处理是不现实的,必须在FPGA可实现情况下尽量提高时间差采样率。同时,通过图7可以看出,减小环路噪声带宽BL可以抵消鉴相灵敏度对环路输出性能的影响。

图7 减小环路带宽BL可以抵消鉴相灵敏度对环路输出性能的影响Fig.7 The decrease of BL can compensate phase detector quantization decrease

3.1.2本振压控压DA器件量化

考虑晶振的数字控制对环路性能造成的影响。因为N位DA的量化误差的方差为

若N位DA控制晶振的最大调整范围为±5Hz,晶振标称f0=10MHz,有f0·Δ·2N-1=5,则频率控制步长为

DA的量化误差方差为

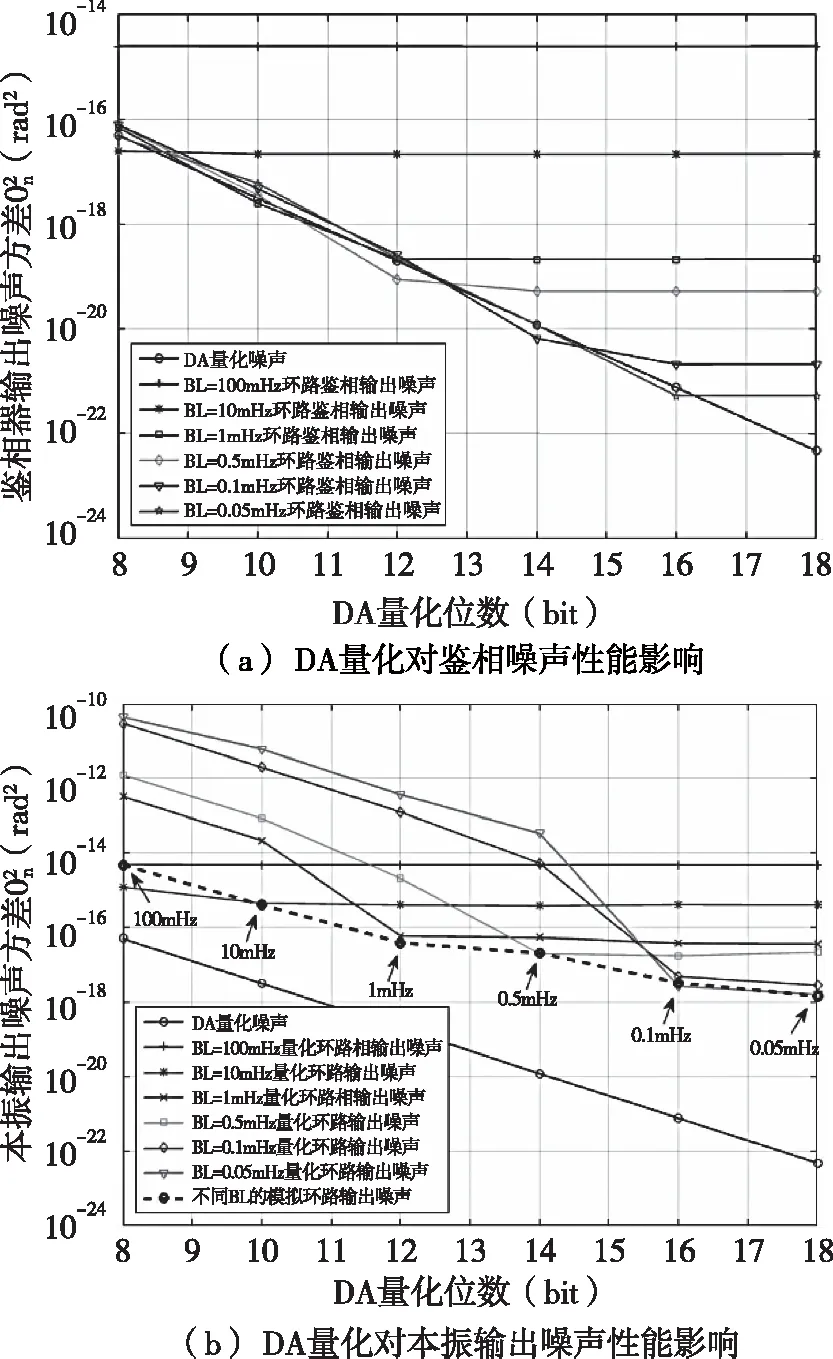

DA量化位数对环路噪声的影响如图8所示。

图8 DA量化位数对环路噪声的影响示意图Fig.8 The influence of pll noise by DA quantization

可见,DA的量化位数限制了环路噪声带宽所能获得的鉴相噪声性能,进而决定了环路最小可设的有效带宽BL。由于晶体老化的影响,在环路带宽过低时,DA量化会造成相位输出起伏,反而使环路噪声性能严重恶化。本振存在老化时,不同带宽下DA量化(16bit)与非DA时输出噪声方差(rad2)比值如图9所示。

图9 不同带宽下DA量化(16bit)与非DA时输出噪声方差(rad2)比值示意图Fig.9 The ratio of local oscillator noise variance between DA(16bit)and pure analog

从图9可以看出,噪声带宽不易过小,否则DA量化噪声会造成输出噪声性能恶化。

同时,DA位数也决定了输出频率的准确度[7]。若频率输出准确度要求优于1×10-11,按1×10-12设计,则对于控制电压为(0~5)V,频率变化范围±3Hz的10MHz晶振来说,通过压控压分辨率求DA位数N,有

(8)

由式(8)可知,DA至少为20位。

3.1.3环路的定点运算

Matlab模型中各模块内部运算与输出均为实数表示,尽管考虑了量化,但由于模型内部模块为浮点双精度数表示,具有足够精度,且积分器不设上限。因此,须考虑实际使用中FPGA内部的定点数表示对环路性能的影响[8]。

环路数据位宽64bit,积分器位宽96bit时,环路浮点运算与定点运算在环路输出噪声性能上的比较如图10所示。可见,采用适当位宽后环路定点运算近似于浮点运算。

图10 环路浮点运算与定点运算在环路输出噪声性能上的比较曲线图Fig.10 The comparison on local oscillator output performance between floating point and fixed point arithmetic

3.1.4DA输出对相位噪声性能的影响

若待驯服对象为高稳晶振,则需考虑DA输出更新频率对环路性能的影响。当数字锁相环路的更新周期与外参考1PPS时间基准信号一致时,锁相环输出相当于1Hz低频信号,若直接控制DA产生的压控压,则高稳晶振相位噪声将会出现1Hz低频信号的各次谐波,使得偏移(0.1~10)Hz的相噪恶化,如图11所示。

图11 1Hz DA输出频率对相噪的影响曲线图Fig.11 The influence on local oscillator output phase noise by 1Hz DA update frequency

因此,锁相环输出后必须接带宽<1Hz的数字低通滤波器。数字滤波器主要考虑截至频率fc、滤波器阶数和采样频率fs。截至频率越小越有利于抑制相位噪声,但由于滤波器带宽与产生的附加延迟成反比,过大的延迟反而可能使环路失锁,仿真结果表明,Fc=0.001Hz的1阶butterworth滤波器即可,而1,2,3阶Fc=0.000 1滤波器环路都会产生振荡,如图12所示。

图12 数字滤波器阶数、截至频率对相位噪声影响曲线图Fig.12 The influence on DPLL phase noise by digital filter order and cut frequency

数字滤波器的采样率越高,它所产生的混叠频率越高,越容易被简单模拟滤波器滤除,但高采样率意味着高计算量和高功耗,由图13给出的仿真结果可以看出,从相位噪声抑制角度看,100Hz的数字滤波器采样率已经足够。

图13 数字滤波器采样率对相位噪声影响曲线图Fig.13 The influence on DPLL phase noise by digital filter sample frequency

4 实测结果

频标模块组成框图如图14所示。

图14 频标模块组成框图Fig.14 The composition of frequency standard component

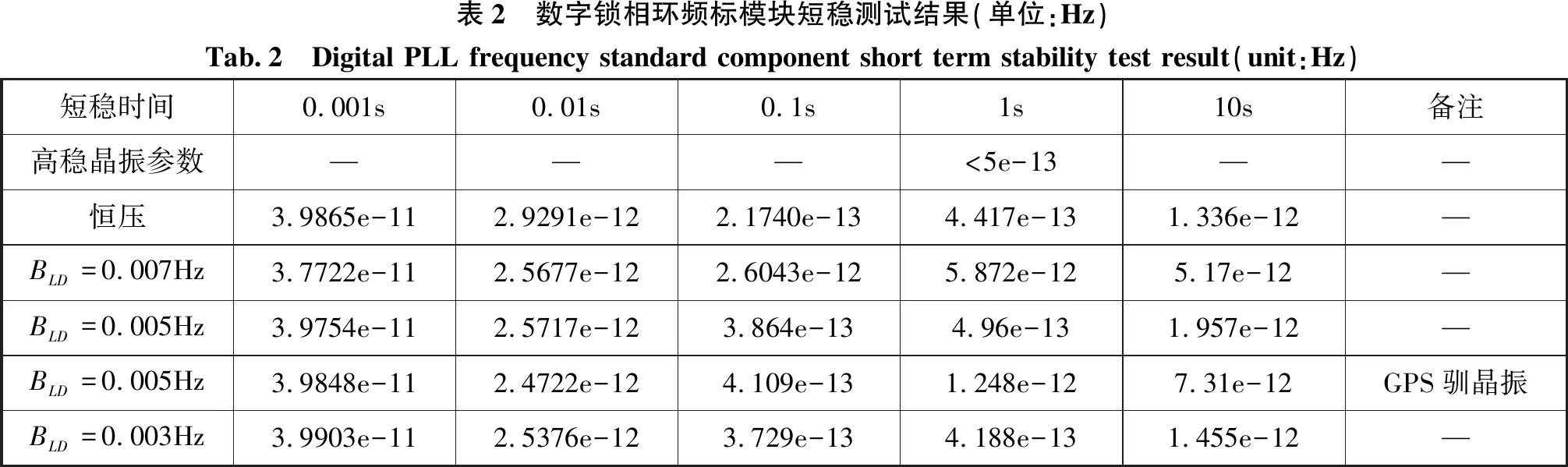

为了验证数字锁相环频标方案的可行性,以晶振8607作为参考源对频标模块进行测试,结果数据见表1和表2,曲线结果如图15所示。

由测试结果可知,环路带宽BL=0.005Hz的环路性能只是略低于BLD=0.003Hz,但BL=0.005Hz环路锁定时间在1h左右,而BL=0.003Hz环路则>3h,所以工程上取BL=0.005Hz即可满足要求。测试均采用了二阶环路结构,因为由仿真可知当BL<0.000 2Hz时,才会出现环路稳态相差Δφ≠0情况。设计中数字低通滤波器截至频率为fc=0.01Hz。

还可看出,在同样环路带宽BL下,GPS/BD驯铷钟,铷钟驯晶振的频标结构性能要明显优于GPS/BD直接驯晶振的性能。但在指标可接受情况下,采用GPS/BD直接驯晶振的结构可以大大降低频标模块的成本。

表1 数字锁相环频标模块相位噪声测试结果(单位:dBc/Hz)Tab.1 Digital PLL frequency standard component phase noise test result(unit:dBc/Hz)相噪频偏0.001Hz0.1Hz1Hz10Hz备注高稳晶振参数——<-113<-143—恒压-37.9-81.1-112.3-136.8—BLD=0.007Hz-33.4-57.3-92.8-129.9—BLD=0.005Hz-34.7-77.8-112.5-136.8—BLD=0.005Hz-25.9-71.5-112.7-136.8GPS驯晶振BLD=0.003Hz-37.0-80.4-112.8-136.9—

表2 数字锁相环频标模块短稳测试结果(单位:Hz)Tab.2 Digital PLL frequency standard component short term stability test result(unit:Hz)短稳时间0.001s0.01s0.1s1s10s备注高稳晶振参数———<5e-13——恒压3.9865e-112.9291e-122.1740e-134.417e-131.336e-12—BLD=0.007Hz3.7722e-112.5677e-122.6043e-125.872e-125.17e-12—BLD=0.005Hz3.9754e-112.5717e-123.864e-134.96e-131.957e-12—BLD=0.005Hz3.9848e-112.4722e-124.109e-131.248e-127.31e-12GPS驯晶振BLD=0.003Hz3.9903e-112.5376e-123.729e-134.188e-131.455e-12—

图15 数字锁相环频标模块实测结果示意图Fig.15 Digital PLL frequency standard component test result

5 结束语

本文利用数字锁相环技术完成了时频系统中的频标模块设计。锁相环鉴相为1PPS脉冲比相方式。环路设计包括本地频率源模型、外部参考1PPS信号模型、二阶/三阶环路滤波器设计等。在硬件实现时需要考虑环路噪声带宽及各组成部分量化,浮点数、定点数表示对环路噪声性能的影响。DA输出应当考虑数字环路所特有的低频信号谐波问题,而须外加带宽<1Hz的低通滤波器。