适用多种码速率的遥控副载波数字化解调设计

2019-05-27

(北京空间飞行器总体设计部,北京 100094)

0 引言

传统遥测遥控体质上行信号采用相位调制(PM)方式,主载波信号上调制了多种频率的测距音信号以及上行8 kHz的遥控副载波。其中测距音信号用来实现星地测距测速功能,遥控副载波采用PSK调制方式实现遥控指令与上行注入数据的发送。星上应答机滤除上行载波后将测距信号调制在下行载波上转发,对遥控副载波信号进行低通滤波后送后续遥控设备进行解调。传统遥控解调电路采用模拟锁相环路实现8K副载波的跟踪解调输出PCM数据。但是模拟解调电路有自身的缺点,由于副载波跟踪环路采用的是简单的锁相跟踪环,所以对前置滤波器的滤波性能要求较高,否则跟踪环路的环内信噪比低容易失锁,滤波器的带宽要根据信息码速率来调整,当遥控码速率较低情况下很难将滤波器的带宽调试的较窄,并且较窄的滤波器环路参数更容易受环境温度的影响而发生参数漂移。深空探测任务由于通信距离遥远,常采用低码速率通信,当码速率低于500 bps以下时滤波器调试将会变得十分困难。采用数字化解调方法可以解决上述问题。应答机输入给遥控设备的副载波信号特征如下:

1)调制方式:PSK调制;

2)输入信号功率(信号加噪声)的有效值:500~1100 mV;

3)输入信号Eb/N0:大于16 dB;

4)输入信号码速率:125 bps、250 bps、500 bps;

5)副载波频率准确度:8000 Hz±0.02%;

6)位同步时间:小于128位;

7)误码率:遥控解调器误码率小于5×10-6。

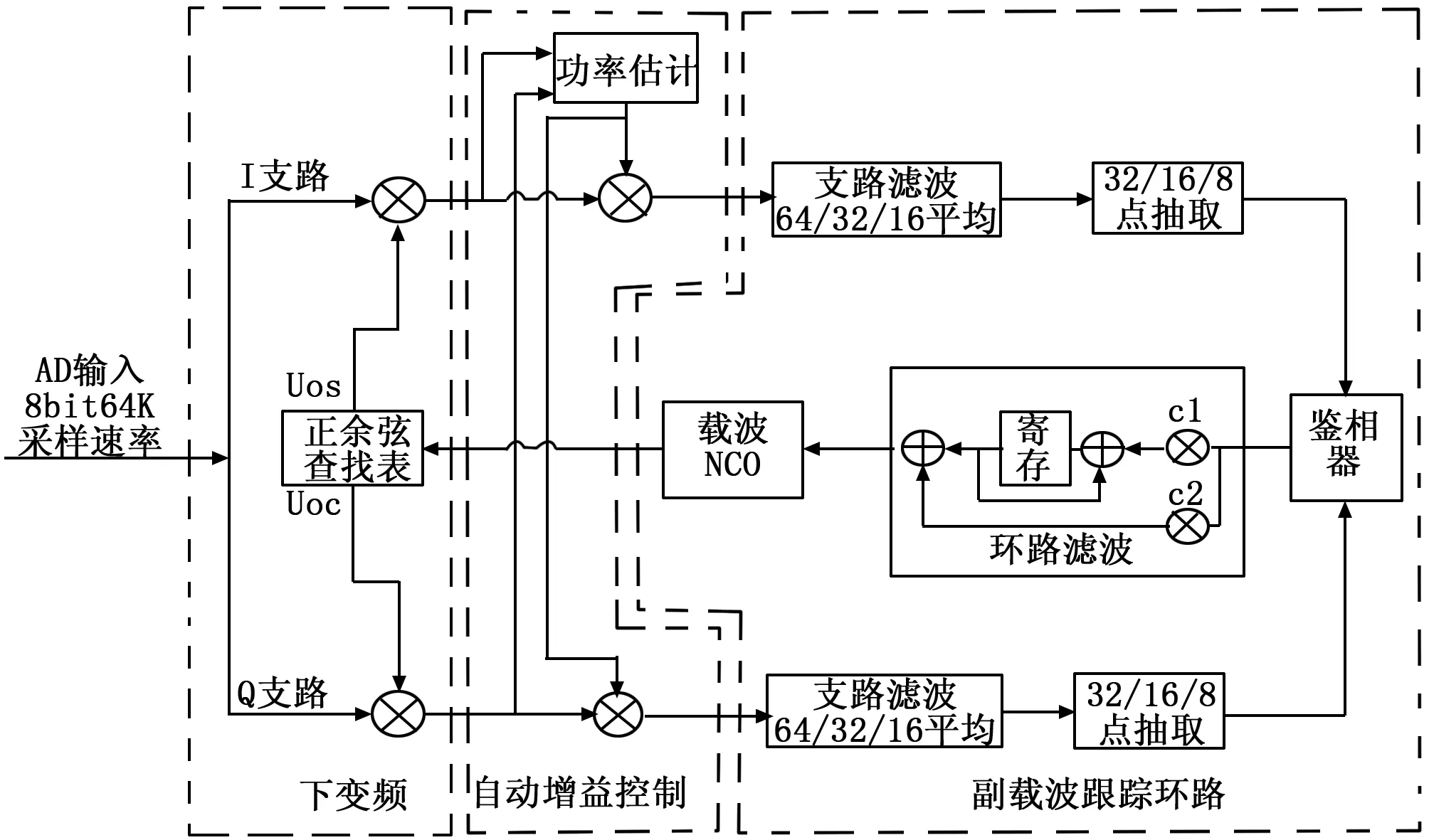

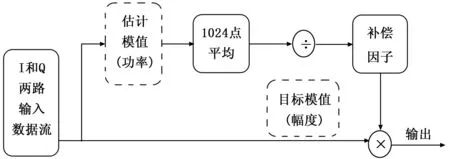

遥控解调器接收应答机输入的PSK调制信号首先经过模拟带通滤波器,滤除带外噪声信号,为了适应最高500 bps的码速率,模拟带通滤波器带宽统一设计为1.2 kHz。经过滤波后按照64 kHz的采样速率进行8位A/D量化,随后送FPGA进行解调处理。采用数字解调技术,以前模拟解调电路上的带通滤波器的主要功能转变为了抗混叠滤波,所以三种码速率可以采用一个滤波器来适应,更多的噪声滤除工作放在了FPGA内部实现。图1是FPGA内部副载波跟踪环路框图,输入信号分为同相、正交分量与本地NCO相乘实现下变频,随后进行自动增益控制保证输入给后续运算电路的信号功率稳定。支路滤波器采用滑动平均加抽取的方法对信号中的高频分量进行滤除。鉴相器输出鉴相误差经过环路滤波器后控制NCO调整本地频率及相位使之与输入8 kHz副载波同频同相实现跟踪。

图1 数字解调副载波跟踪环FPGA设计框图

1 副载波解调器及算法描述

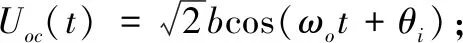

1.1 下变频及环路参数

令输入PSK信号为:

(1)

与本地输出的同相正交支路载波相乘后输出的信号为:

ip(t)=Ui(t)×Uoc(t)=-abD(t)[cos((ωi+ωo)t+

(θo+θi))-cos(ωet+θe)]+ni,p

其中:ωe=ωi-ωo;θe=θi-θo。

公式中,角速度和频项为高频分量,差频项为低频分量。对于输入信号Ui(t)功率为a2,噪声功率为σ2,输入信噪比为snr=a2/σ2,当输入信号在同相支路上与复制载波Uos(t)相乘后,可以计算出噪声项ni,p的功率仍旧维持在σ2。混频后再经过支路低通滤波后滤除了倍频分量与带外噪声得到了如下混频结果:

Ip(t)=abD(t)cos(ωet+θe)+ni

(2)

Qp(t)=abD(t)sin(ωet+θe)+nq

(3)

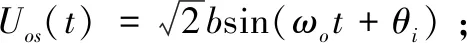

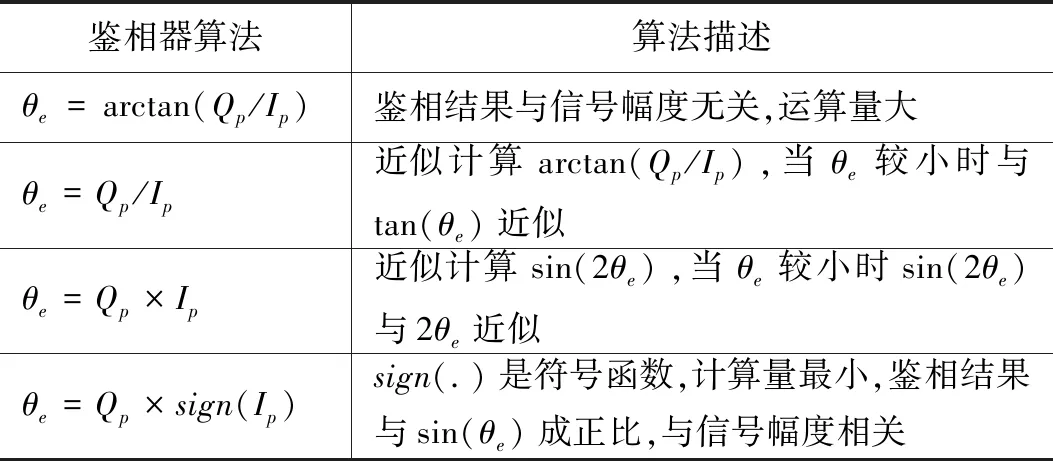

支路低通滤波器滤除下变频后其中的高频分量及噪声再进行鉴相。鉴相器的输出反映了输入副载波与本地NCO输出副载波的相位差,当相差为正时,表示本地NCO输出信号相位滞后输入信号则加快本地NCO频率,否则减慢本地NCO频率。鉴相器有多种形式,表1总结了四种鉴相器算法[1]。

其中第一种方法计算量大,需要采用CORDIC算法来实现,第二种方法需要设计除法运算电路,相比较来看只有第四种实现起来简单,适合资源较少的反熔丝型FPGA来实现,但缺点是鉴相结果受输入信号幅度影响。正是考虑到这一点所以在信号路径上需要增加自动增益控制环节。

表1 常用鉴相算法

1.2 支路滤波器设计

支路滤波器采用滑动累加求平均再抽取的方法实现。滑动平均相当于低通滤波器。当码速率为500 bps时采用16点滑动平均8点抽取,相当于经过截止频率为4 kHz的低通滤波器,抽取后鉴相器的更新频率是8 kHz; 当码速率为250 bps时采用32点平均16点抽取,相当于经过截止频率是2 kHz的低通滤波,抽取后鉴相器的更新频率是4 kHz;当码速率为125 bps时采用64平均32点抽取,相当于1 kHz的低通滤波,鉴相器的更新频率是2 kHz。

1.3 自动增益控制设

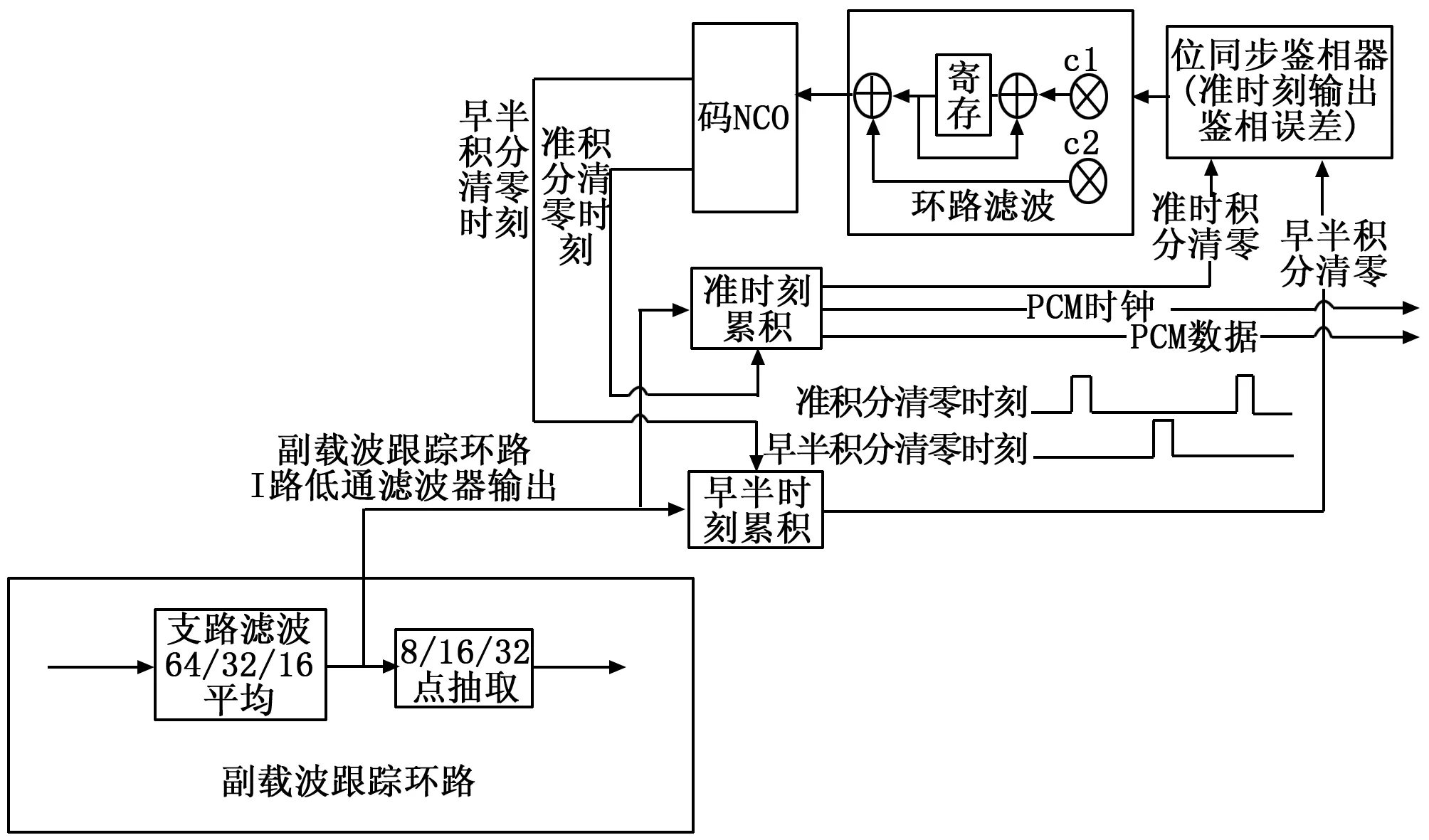

应答机输入给遥控设备信号的有效值在500~1100 mv RMS波动,通过自动增益动态调整输入信号的放大量可以使输入信号保持稳定的幅值,有利于基带处理避免过载并充分利用量化比特,减小量化误差。自动增益模块对下变频后信号进行功率估计,并与目标值比较,刷新补偿因子,实现对输入信号的动态放大。算法采用前向调整的方式,没有反馈路径,图2是该算法的实现框图[2]。

图2 自动增益控制模块实现方法

输入信号功率不会有太快的波动,采用1024个采样数据滑动求平均来估计出当前的功率,并计算出补偿因子,计算功率估计时可以采用如下近似计算方法实现[3]。

(3)

1.4 环路滤波器设计

副载波跟踪环的环路滤波器采用理想二阶环,可以对频率阶跃信号无误差的跟踪。环路滤波器的实现形式如图1所示,滤波器包括积分支路与直通支路,令:ts是环路鉴相误差更新频率;ε:是环路阻尼系数;bl:环路带宽,则环路无阻尼振荡频率:

ωn=(8×ε×bl)/(4×ε2+1)

(4)

令:K=Ka×Kb环路增益,Ka:鉴相增益,Kb:压控增益;P:自动增益控制设定的输出信号幅度。fs:数控振荡器(NCO)的工作频率,nco_len:NCO的累加位宽;则:Ka=2P/π,Kb=2×π×fs/2nco_len;则锁相环路积分支路[4]:

(5)

直通支路:

(6)

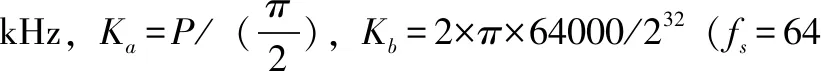

1.5 位同步环路设计

位同步环路的主要功能是提取调制数据的位同步信息,恢复出本地PCM码流时钟信号。采用早准支路的方法实现位同步时钟的恢复。位同步环路的输入是图1中同相支路的滤波器的输出,图3是位同步环路FPGA实现框图[5]。

图3 位同步环路FPGA设计框图

码NCO根据信息码速率,输出相应频率的准时刻积分清零脉冲以及相差π相位的早半积分清零脉冲。图3中,“准时刻累积”模块对输入信号进行积分累加,当准积分清零时刻到达时输出累加值,同时将自身累加值清零。“早半时刻累积”模块依据早半积分清零脉冲输出累加值以及对累加器清零。位同步鉴相器在准积分清零时刻依据两个积分清零值按照如下鉴相算法[6]计算出位同步的鉴相误差,并输出给环路滤波器。

令:Ip(n),Ip(n-1),Ie(n),phe分别是准时刻当前积分清零值、准时刻上一次积分清零值,早半时刻当前积分清零值以及相位误差,则鉴相器的计算规则是,如果:sign(Ip(n))=sign(Ip(n-1)); 则:phe=0;如果:Ip(n-1)>0并且Ip(n)<0;则:phe=-Ie(n);如果:Ip(n-1)<0并且Ip(n)>0;则:phe=Ie(n);

位同步环的环路滤波器与载波环的环路滤波器有相同的参数定义,所不同的是,位同步环路的鉴相增益和环路鉴相更新频率。令:fb是遥控信息码速率则:Ka=P/π,ts=1/fb。位同步环路中直通与积分支路的系数计算方法与副载波跟踪环计算方法一致。当位同步环路实现锁定时,此时的准积分清零时刻脉冲即是恢复出来的PCM时钟。当采用硬判决实现解调时,则当准时刻积分清零值为正数则解调输出1,否则输出0。由于副载波跟踪环的稳定平衡点为0°或180°所以导致解调输出的数据存在相位模糊度,即原始信息位如果是0则解调后全部输出1,原始信息为是1则解调输出全为0。信息位的相位解模糊由后续帧同步检测电路根据特定的数据帧内容进行识别。

2 工程参数设计

3 仿真验证与分析

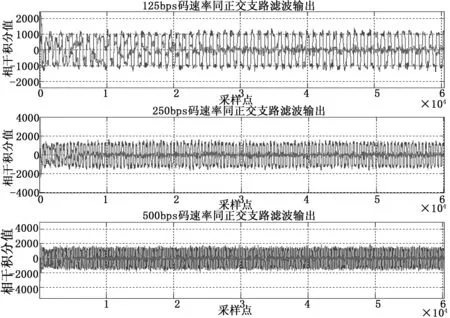

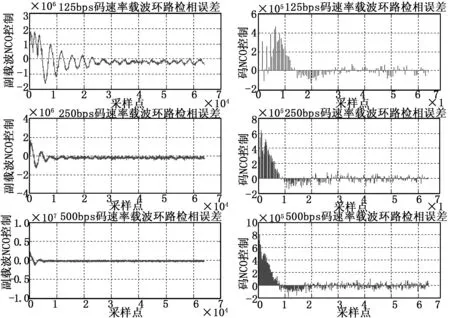

根据以上算法的描述以及工程实现参数,对三种码速率解调进行了仿真,仿真条件是Eb/N0:16 dB,多普勒:2 Hz,仿真时间1秒,图4显示了三种码速率下同相支路与正交支路经过支路滤波器后输出的信号,可以看出当副载波锁定后同相支路的积分值最大而正交支路的积分值最小,图5是副载波和位同步跟踪环路NCO控制曲线,从中可以看出三种码速率均实现了载波跟踪以及位同步,实现正常的数据解调。

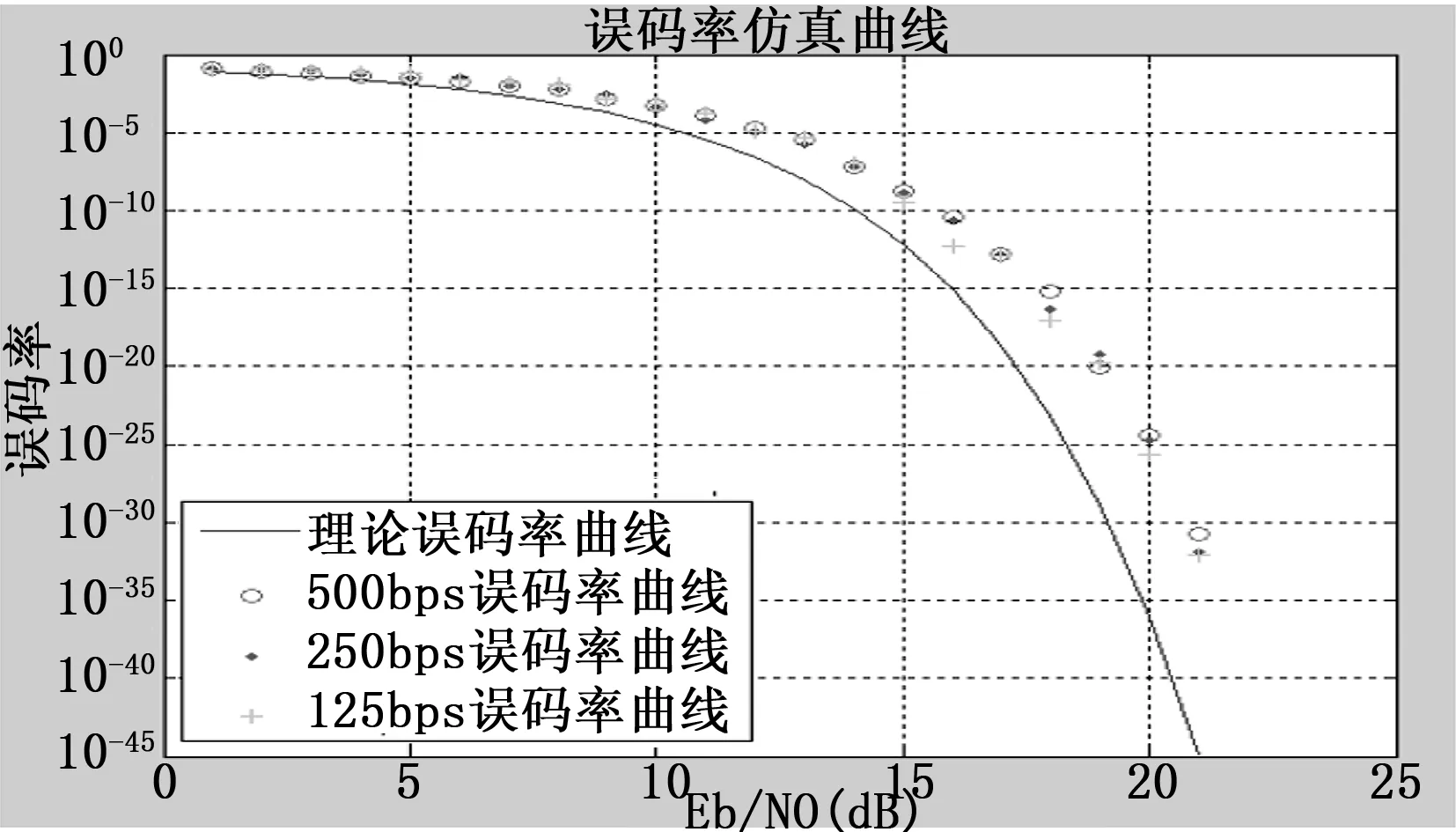

算法仿真是建立在浮点运算基础上的,最终采用FPGA实现时需要将上述运算定点化。FPGA在实现下变频、自动增益控制、鉴相及积分清零等计算过程中均存在数据位宽的截断,这无形中就会引入量化误差导致解调损失。在确定各个环路的数据位宽后采用定点仿真,计算出在三种码速率下当输入Eb/N0在0~20 dB变化过程中,解调器输出端的Eb/N0,并给出了误码率仿真曲线,仿真结果表明,该解调器在正常工作条件下(应答机输入的Eb/N0在16~20 dB)的解调损失在2~2.5 dB范围内,均满足5×10-6的误码率要求。图6是算法定点化后的误码率仿真曲线。

图4 三种码速率下同相、正交支路滤波器的输出

图5 三种码速率下载波NCO及码NCO的误差控制曲线

图6 三种码速率定点解调误码率仿真曲线

4 可靠性设计

在多数卫星中,遥控通道是地面上行控制卫星的唯一通道,所以遥控解调的稳定性与可靠性尤其重要,为此,需要增加对解调电路可靠性设计。遥控解调模块的副载波跟踪环路与码跟踪环路的环路滤波器均采用理想二阶环设计实现。由于遥控通道是采用突发通信工作模式,故大部分时间是没有副载波信号输入的,而是噪声。当输入的噪声不是理想白噪声时,环路滤波器中的积分支路,会逐渐偏离设计的中心值,长时间输入非白噪声信号会导致本地NCO的输出频率偏离中心频率8 000 Hz较远。

为了防止锁相环的中心频率在无信号输入时偏离中心频率较远,以至在正常遥控信号到来时无法在引导序列内实现副载波和位同步,可以采用如下两种方法。

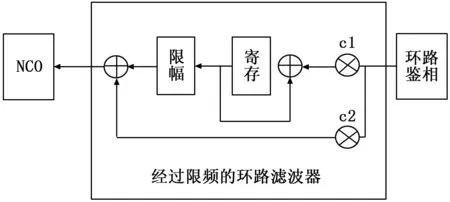

4.1 对环路滤波器输出频率进行限制的方法

仿真、分析副载波及码跟踪环路NCO控制字的震荡范围,合理控制频率区间对积分支路控制字输出幅度进行限制,以达到控制NCO最大输出频率的目的。将图1和图3中的环路滤波器改造如图7所示。该方法的缺点是如果频率范围限制小了会影响环路的自由震荡过程,导致锁定跟踪时间变长,如果限制过过大同样会存在在引导序列以内是否能实现副载波与码的同步问题。所以限制的幅度需要进行合理的仿真与设计。

图7 限频的环路滤波器

4.2 采用副载波锁定检测的方法

采用副载波锁定检测的方法,实时监测副载波锁定状态,如果锁定则不对环路滤波器积分支路中的寄存器进行清零否则进行清零,保证锁相环路每次都是从中心频率开始跟踪输入信号。文献[6-7]提出了一种M进制调制信号的自归一化锁定检测算法,该算法描述如下:

(7)

其中:I(k)、Q(k)表示滑动累加平均后,抽取前的同相与正交信号。针对遥控副载波调制,上述公式简化为:

(8)

确定采样点数N,当y2,N>τ则认为锁定,否则失锁。在一定的Eb/N0的条件下,N与τ的选取关系确定了锁定检测的检测概率及虚警概率。

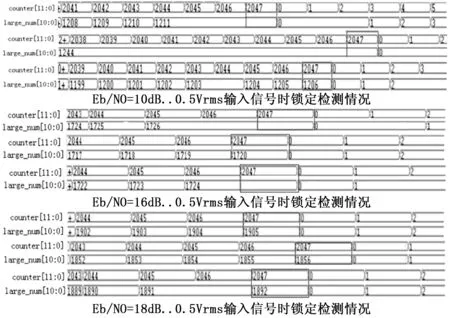

在FPGA实现时,选取采样点数为N=2 048,检测门限τ=0.5。如果这2048个采样点中有1024个采样点都满足τ>0.5则认为是锁定,否则认为失锁。图8是在125 bps码速率条件下不同Eb/N0时通过chipscope软件采集FPGA内部数据的测试结果。图中的counter是采样点计数,large_num是满足阈值条件的采样点数,从中可以看出当Eb/N0>10 dB时,当counte为2047时large_num已经显著大于1024。

由于锁定检查开始时刻与地面发遥控上行是异步关系,在极端情况下当统计了1024点后才收到地面发送的上行信号,导致检测到2048点时仍认为是失锁状态而给滤波器复位重新开始跟踪。为了避免上述情况发生,在系统应用时需要适当增加引导序列的长度来保证遥控信息的正常解调。

图8 不同输入条件下阈值检测情况

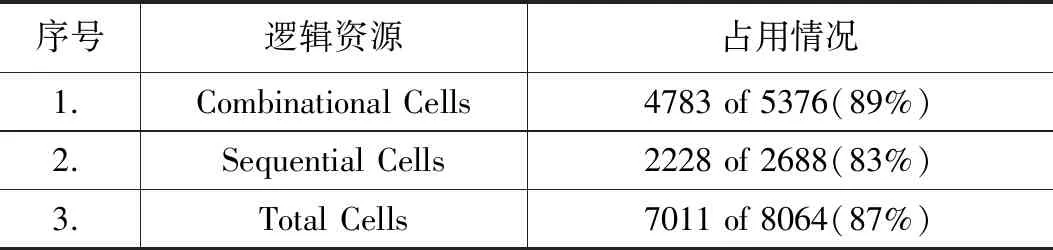

鉴于遥控通道对于整星安全性尤其关键,故尽量不要使用SEU敏感的SRAM型号,本项目选用Actel公司的反熔丝型FPGA (AX500-1CQFP208),最终实现资源占用情况见表2所示。

表2 FPGA资源使用统计

5 结论

本文介绍了一种适应多种码速率的遥控副载波数字化解调方法,算法在matlab环境下进行了浮点与定点的仿真,最终采用反熔丝FPGA芯片设计实现。单机通过了与测控应答机联试,各项测试表明,解调算法及工程实现满足了误码率、频率跟踪误差及位同步时间等多项指标要求,解调损失小,可以作为遥控设备轻小型化和提高产品可靠性设计的一种技术手段。