基于FPGA的多路采集与TCP/IP传输系统设计

2019-02-21余恒松邓皓文

余恒松,邓皓文,伍 春

(1.西南科技大学 国防科技学院,四川 绵阳 621000;2.西南科技大学 信息工程学院,四川 绵阳 621000)

0 引 言

在数据采集应用领域中,为了应对环境复杂多变的采集应用场景和满足人们对采集精度越来越高的要求,除了采用高精度AD外,采集系统的远程可控制和数据实时准确传输的能力也至关重要[1-3]。以太网是当今最通用的局域网通信协议标准,具有通信可靠、传输速度快、远距离传输和适配多种传输介质等优点[4]。而TCP/IP协议具有开放的协议标准,不依赖固定的硬件或软件系统,可以将TCP/IP协议集成于不同的网络标准中。韩国WIZnet公司推出的W5500是一款集成了TCP/IP协议栈的全硬件以太网芯片,可以有效解决基于硬件的TCP/IP协议开发难度大且周期长的问题[5]。因此,本文设计了一种基于FPGA+W5500的多路数据采集与以太网TCP/IP传输系统,不仅可以实现16路模拟信号的并行采集,还可以满足多路采集系统远程可控制和数据实时准确传输的能力。

1 系统整体结构设计

本系统主要由信号采集部分和TCP/IP传输部分组成,其中信号采集部分由信号调理模块和模数转换器(ADC)组成。TCP/IP传输部分的主体为W5500,FPGA作为主控,需对采集和传输部分进行控制。系统的总体结构如图1所示。

具体地,16路模拟信号并行进入采集系统的信号调理模块,经过调理后的信号分成两组(每组8路)输入ADC中进行转换,再由FPGA实现16路并行采集,最后由FPGA控制W5500将采集数据通过以太网发往PC机。

2 信号采集部分设计

信号采集部分由信号调理模块和ADC组成。信号调理模块包含低通滤波器和两级放大器,信号采集部分的结构如图2所示,信号采集部分则由FPGA进行控制。

模拟信号的输入电压幅值包含多个档位,频率范围为10 Hz~20 kHz。为保证采集精度,需要采取低通滤波器开关可选和分级放大的方式,且放大器的增益可调。系统采用的ADC芯片为AD7609,采集精度为18 bit,支持8通道同步采样。

图2 信号采集部分的结构

3 TCP/IP数据传输系统设计

W5500支持TCP、UDP、IPv4、ICMP、ARP、IGMP和PPPoE协议,支持10/100M以太网通信。FPGA基于SPI协议对W5500内部的寄存器区和内存进行读写访问。寄存器区由通用寄存器区和8个Socket_n(0≤n≤7)寄存器区组成。通用寄存器区用于配置网关、子网掩码、源IP和源MAC地址等。Socket_n寄存器区用于配置Socket端口号、模式、配置命令等,且提供了Socket的状态和中断信息。W5500的内存大小为32 kB,分为接收内存和发送内存,各占16 kB,分别用于缓存网络传输中已接收和待发送的用户数据。

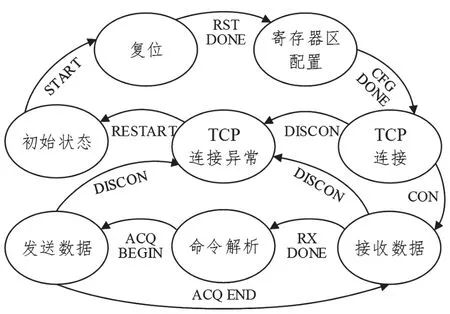

根据具体的采集应用场景,W5500(服务端)接收上位机(客户端)的采集配置命令,并回传采集数据。为简化设计,采用状态机控制W5500,状态转移图如图3所示。

图3 主状态机状态转移

经过复位、寄存器区配置、建立TCP连接后,用户可由上位机下发采集配置信息,如低通滤波开关、通道选择和放大器增益等。FPGA从W5500接收缓存读取用户配置信息,然后进行命令解析(将配置信息下发到信号采集部分),并启动采集。16路数字信号并行进入FPGA,由异步FIFO转换为串行数据流写入W5500的发送缓冲。待采集结束后,返回接收数据状态,继续等待一下组命令。若TCP连接发生中断、超时等异常情况,FPGA将重启W5500。

TCP连接建立、数据接收和数据发送,是整个W5500控制状态机的核心。选取Socket_0作为与上位机程序进行数据通信的端口。

(a)TCP连接建立的流程如图4(a)所示。FPGA向Socke_0的配置寄存器Sn_CR[7∶0]写入“OPEN”和“LISTEN”命令,分别将Socket_0端口初始化和配置为TCP服务器,通过检查状态寄存器Sn_SR[7∶0],判断命令是否生效。配置完成的TCP服务器将一直监听信道,等待客户端的连接请求。

(b)TCP数据接收的流程如图4(b)所示。中断寄存器Sn_IR[7∶0]提供了Socket_0的中断信息,当Sn_IR[2]为“1”时,表示W5500收到数据。Sn_RX_RD[15∶0]为接收读指针寄存器,Sn_RX_WR[15∶0]为接收写指针寄存器,分别提供了数据在接收内存中存储的首地址和末地址,两地址相减可得接收数据的长度。数据接收完成后,需将Sn_RX_RD[15∶0]的值更新为之前获取的末地址值。

(c)TCP数据发送的流程如图4(c)所示。发送写指针寄存器Sn_TX_WR[15∶0]提供了发送内存中的首地址,FPGA需从这个首地址开始将数据写入发送内存中,并将Sn_TX_WR[15∶0]更新为“首地址+数据长度”的值。发送“SEND”命令后,可轮询检查中断寄存器的Sn_IR[4],若为“1”,表示数据发送完毕。

4 模拟信号采集实验

4.1 TCP/IP传输实验

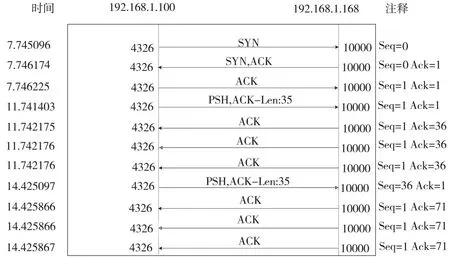

在进行TCP/IP协议通信测试时,将采集系统配置为服务器(IP:192.168.1.168,端口号:10000),上位机为客户端(IP地址192.168.1.100,端口号为4326),采集系统与上位机的TCP/IP通信流量统计的结果如图5所示。

图5给出了TCP建立连接的“三次握手”、数据发送与回复ACK确认的过程,说明TCP/IP通信传输正常。

4.2 信号采集实验

为了验证数据采集系统的功能,选择对一组小信号进行采集。使用FLUKE 5522A高精度校准仪产生一组正弦波模拟信号,信号幅度的有效值和频率为15.91 mV、1 kHz。系统以200 kHz的采样率进行采集,并经W5500上传到上位机进行解析和显示。

采集该信号时,FPGA需配置放大器的增益为200倍(第一级放大2倍,第二级放大100倍),放大后的峰值电压为±4.5 V,上位机显示采集信号的时域和频域的波形如图6所示,所采信号的增益精度满足±0.1%的需求。

图4 TCP建立和数据接收发送流程

图5 TCP流量统计结果

图6 采集信号的时域和频域结果

5 结 论

本文设计了一种基于FPGA的多路采集与TCP/IP传输系统,采用FPGA+W5500架构,可以实现基于硬件的TCP/IP协议通信,并详细介绍了系统的信号采集部分和TCP/IP数据传输部分的设计方法。经实验表明,系统可以实现多路模拟信号的采集和可靠传输,且系统稳定可靠,具有一定的实用价值。