基于ZYNQ组件化开发环境的设计与实现

2018-11-28赵智杰刘拥军

赵智杰,高 博,刘拥军

(信息工程大学 信息系统工程学院,河南 郑州 450000)

软件无线电是指在一个通用的硬件平台上,通过重构软件来实现通信功能切换的无线电系统。软件无线电硬件平台的特点是通用化、标准化、模块化,以及对信号波形的广泛适应性[1-2]。随着软件无线电平台所处理信号的带宽的提高,FPGA、DSP等专用处理器不可避免的被纳入到软件无线电平台中。为降低FPGA波形组件和具体硬件平台的耦合度,借鉴软件通信体系架构(Software Communication Architecture,SCA)中的MHAL(Modem Hardware Abstraction Layer)规范和CP289(Change Proposal 289)中容器的思想,在FPGA中设计标准的组件运行环境[3-4]。通过运行环境为上层波形软件提供标准接口,提高了FPGA波形组件的可移植、可重用和可互操作性[5]。但是环境中的驱动封装和协议解析功能都是通过FPGA内部逻辑资源实现的,导致FPGA中可编程逻辑资源的布局布线过于复杂,使得 FPGA时序容易出现亚稳态。该问题在一定程度上限制了FPGA波形组件所处理信号的带宽,同时也影响了整个系统的稳定性。

本文结合当前处理器的发展设计了一种基于ZYNQ处理器的组件化开发环境。环境的驱动封装模块和协议解析模块由ZYNQ的PS(Processing System)端实现。利用PS端的协同处理设计FPGA波形组件运行环境,可以提高系统灵活性和稳定性并实现FPGA波形组件的可移植与可重用。

1 ZYNQ组件化开发环境的设计

实现波形组件移植的关键在于抽象和分离,通过标准化波形组件与底层环境的通信接口,可以实现底层硬件的抽象。通过标准化平台间通信协议,可以实现波形组件和系统的分离。为了实现上述目标,SCA2.2.2规范中提出了硬件抽象层(Modem Hardware Abstraction Layer,MHAL)概念。MHAL为异构平台中不同处理器提供了互联互通的方式。随后CP289中提出了容器的概念,同时为了给波形组件提供标准的接口引入了OCP(Open Core Protocol)协议。容器和OCP接口实现了波形组件和底层硬件环境的分离。

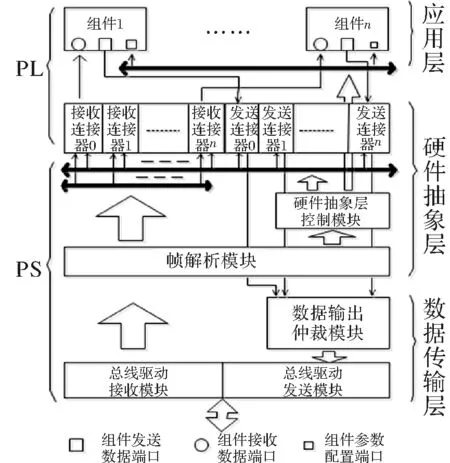

图1 组件运行环境

本文借鉴SCA中容器设计思想和MHAL规范,设计了一个基于ZYNQ的组件化开发环境。如图1所示,整个组件化开发环境由数据传输层、硬件抽象层以及应用层3部分组成[6-11]。数据传输层负责FPGA内部波形组件与外界的数据交互;硬件抽象层通过解析处理器间的通信协议为上层波形组件提供标准的信号接口;应用层负责承载特定的波形应用。

1.1 数据传输层

数据传输层由IO驱动、数据解析与封装和数据发送仲裁3个功能模块组成[12-13],数据传输层内部结构如图2所示。

图2 数据传输层

波形组件接收数据时,IO驱动将数据写入到数据解析模块。数据解析模块会判断数据报文中处理器的地址,如果正确,则数据进入硬件抽象层作进一步处理,同时将源处理器地址保存在数据封装模块中,作为发送数据的目的处理器地址;如果不正确,则不接收当前的数据报文。

波形组件发送数据时,首先发送传输请求信号到仲裁模块。仲裁模块根据组件优先级和数据的紧急程度有序的输出数据。通过数据传输层实现了FPGA内部波形组件和FPGA外界的通信。

1.2 硬件抽象层

硬件抽象层作为FPGA波形组件和数据传输层的中间模块,解析处理器间传输协议,同时也为波形组件提供标准的应用接口。如图1所示,硬件抽象层由帧解析、硬件抽象层控制以及连接器3个模块组成[14]。

硬件抽象层接收到数据帧时,帧解析模块会判断是参数配置帧还是通信数据。若是通信数据,则通过接收连接器发送到FPGA波形组件的接收端口;若是参数配置帧,则通过硬件抽象层控制模块完成相关模块的参数配置,如连接器的逻辑地址的设置。硬件抽象层传输波形组件数据时,考虑到不同波形组件的优先级不同,采用了请求应答的方式进行数据传输。

硬件抽象层通过连接器模块为上层波形组件提供标准应用接口,实现组件运行环境的底层抽象。通过设计标准的数据传输协议,平台中不同处理器上的波形组件实现了互连互通。

1.2.1 数据传输协议

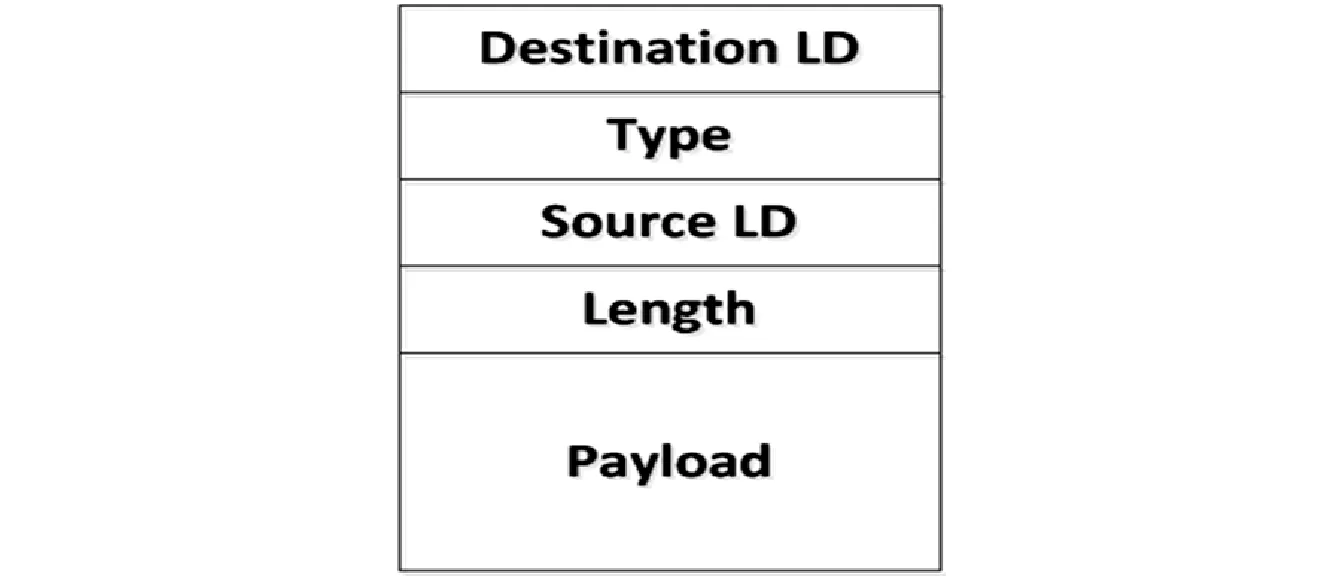

参考SCA中的MHAL规范,针对ATCA异构信号处理平台的特点,设计了如图3所示的硬件抽象层消息格式,实现了不同处理器中波形组件的通信。Destination LD表示目的组件端口的逻辑地址,Source LD表示源组件端口的逻辑地址,通过配置组件端口的逻辑地址可以实现波形组件的任意互连;Type表示所接收消息的类型,通过Type字段可以判断当前帧是控制消息还是通信数据;Payload字段的内容为通信数据或者是控制消息;Length表示当前消息的长度。

图3 硬件抽象层间消息格式

1.2.2 连接器模块的设计

连接器模块由接收连接器和发送连接器两部分组成,并且收发连接器和波形组件的收发数据端口一一对应。连接器模块为波形组件提供标准接口,使波形组件从底层硬件抽象出来。考虑到不同波形组件的处理数据位宽和工作时钟的不同,本文采用异步FIFO设计收发连接器,解决了不同波形组件之间数据位宽和工作时钟不同的问题。

如图4所示,波形组件和底层的通信由连接器实现。波形组件接收数据时,数据首先被写入接收连接器FIFO里面,当接收完一包数据之后,接收连接器的数据传输请求信号WDI_Rec_Req有效。波形组件根据实际的情况确定是否反馈应答信号WDI_Rec_Ack。收到应答信号后,波形组件以时钟信号WDI_Rec_Clk将数据WDI_Rec_Data写入到波形组件内部,作进一步的处理。波形组件发送数据流程和接收数据一样,采用请求应答的方式。

图4 组件与连接器互连图

1.3 应用层

应用层由一个或者多个波形组件构成,波形组件是一个功能独立且与平台底层硬件环境无关的单元模块,用户将不同功能的波形组件进行有目的的组合,即可实现特定的应用。为了提高FPGA波形组件的灵活性、通用性和可移植性,本文借鉴了CP289中OCP接口设计方法,结合当前ATCA信号处理平台的实际需求,为FPGA波形组件设计了3种类型的标准接口,如图5所示,分别是本地服务接口、参数配置接口以及通信接口[15]。

图5 FPGA波形组件结构图

1.3.1 本地服务接口

本地服务接口主要给FPGA波形组件提供时钟以及复位等控制信号。为了实现波形组件与系统结构相分离,波形组件本地接口信号必须由组件运行环境来提供。考虑到FPGA波形应用的可靠性,运行环境可以根据情况需求,对构成应用的波形组件进行复位控制。

1.3.2 参数配置接口

根据应用中不同的需求,系统可以通过波形组件的参数配置端口实现波形组件参数的动态配置。波形组件参数的动态配置提高了FPGA波形组件的灵活性。

图6 参数配置接口

由于参数配置消息的长度较短,为提高系统效率,参数配置消息的传输没有采用请求应答的方式。组件运行环境接收到参数配置消息会直接进行相关参数的配置。如图6所示,参数配置接口由多根信号线组成。WCI_MClk是参数配置接口的时钟信号,波形组件通过WCI_MClk时钟信号处理用于配置组件的消息WCI_MData。WCI_MCMd表示控制波形组件的命令类型,通过和线程信号WCI_MThreadID组合可以实现波形组件的控制和配置操作,如控制组件打开或者写组件的寄存器等。WCI_MAddr为波形组件内部寄存器的地址;WCI_MByteEn为字节使能信号,通过WCI_MByteEn信号可以确定WCI_Mdata的有效数据位宽。

1.3.3 通信接口

波形组件的通信接口由数据接收端口和数据发送端口两部分组成。对于不同波形组件而言,其通信端口的数量也会不一样。图7给出了波形组件接收数据端口及其相关信号的定义。波形组件的通信接口主要实现与外界的通信数据的交互。

图7 波形组件接收数据端口

接收连接器发送数据给波形组件时,首先会使能数据发送请求信号WDI_Rec_Req并等待波形组件的应答。当接收连接器收到应答信号WDI_Rec_Ack后,波形组件会以时钟信号WDI_Mclk读取接收连接器中的数据WDI_MData。为满足不同波形应用的需求,用户可以通过字节使能信号WDI_MByteEn改变波形组件数据WDI_MData的有效位宽。利用WDI_Mcmd与WDI_MAddr信号可以改变波形组件存储数据的位置等信息。数据发送端口的信号定义和功能与数据接收端口是相同的。

2 实现与应用

本文采用模块化设计思想,在ZYNQ处理器中实现了FPGA波形组件的标准运行环境。承载了标准运行环境的ZYNQ处理器通过标准的AMC板卡接入到ATCA平台中的承载板上面,通过ATCA平台中的背板实现了不同板卡上的不同处理器的连接。

图8 应用装配视图

ATCA异构信号处理平台实现应用的流程如下:首先用户根据自己的需求在平台中的可视化界面上进行应用的装配;完成应用的装配之后,通过加载运行,系统会根据内部的资源情况以及不同处理器的性能特点将组件部署到不同的处理器上;组件部署结束之后,系统根据用户的要求,发送配置消息给相关处理器进行参数初始化,随后即可在信号处理平台中完成用户装配的应用。

为了测试所设计的组件化开发环境的可行性与合理性,按照文中提出的标准波形组件接口设计了FFT波形组件,并在基于ATCA的异构信号处理平台进行了测试验证。如图8所示,FFT波形组件接收ATCA中CPU中的数据,并将处理后的结果通过CPU端的监视组件显示。图9为CPU中的监视组件显示的结果。

图9 FFT波形组件测试图

测试结果表明,按照文中所给的标准接口设计的波形组件,能够实现与ATCA平台中其他处理器中的组件互连,同时也实现了波形组件的设计与底层硬件环境的分离。

3 结束语

本文利用软硬件协同设计的方法,在ZYNQ处理器中设计了组件化开发环境。在ATCA异构信号处理平台中测试结果表明,FPGA波形组件的设计不需要关注底层的硬件环境。通过将波形组件与底层硬件环境的分离,实现了FPGA波形组件的可移植和可重用。对于系统开发而言,该方案缩短了开发周期,提高了开发效率。