一种高效的星载高速固态存储器坏块管理算法

2018-02-05,,,,

,,,,

(1.上海航天电子技术研究所,上海 201109; 2.上海卫星工程研究所,上海 200240)

0 引言

存储器是卫星上的核心单机之一,其承载着载荷数据的记录与回放功能。基于NAND Flash的固态存储器由于没有机械转动部件、存储密度高、体积小、重量轻,并且具有抗震动、抗冲击、温度适应范围宽等特性,已成为卫星等各类宇航设备的主要数据存储方式。商用固态存储器主要是通过硬盘管理技术和闪存转换层利用串行通信的方式实现对Flash的控制。由于管理复杂,接口速率存在瓶颈,不适合大容量高速率星载固态存储器的使用。星载固态存储器采用FPGA直接对Flash芯片进行控制,提高了存储器的读写速率,降低了管理的复杂度。

目前单片Flash存储芯片的写入速率为40 MB/s,远远满足不了高速载荷的存储速率要求,星载固态存储器都是以分组并行存储和多级流水的方式来提高存储速率。由于NAND Flash存在坏块,为了保证数据存储的可靠性、完整性,当前主要是通过跳过坏块的方式进行坏块屏蔽。该方法简单快捷,但是,并行存储与多级流水操作会带来坏块叠加效应,使固态存储器的初始容量损失较大,存储容量的利用率较低。

Flash芯片的坏块分为初始坏块和使用过程中产生的坏块。图1为3D PLUS公司提供的Flash芯片坏块率曲线,由图可知Flash芯片在使用寿命期限内较为稳定,产生坏块的概率较低,因此影响固态存储器容量损失的主要是Flash芯片的初始坏块[1]。

图1 Flash芯片坏块率曲线

正如前述,随着存储速率的提高,并行存储的芯片数增多,以及坏块的叠加效应使固态存储器的初始容量损失越来越严重。如何在存储器存储速率不断提高的情况下,有效的控制固态存储器的容量损失,提高初始存储容量的使用率成为星载数据存储的一个关键问题。

1 固态存储器并行存储方案

为了满足高速载荷的数据存储速率要求,并行存储方案在固态存储器中得到广泛应用。并行存储通过拓宽数据位宽的方式来提高固态存储器的吞吐率[2]。本文以某卫星型号为例,介绍了星载固态存储器的并行存储架构[3]。该固态存储器的原理框图如图2所示,A、B机的中速数据控制板均可对公共存储模块进行数据记录和回放控制,中速数据控制板主要由高速缓存模块、固态存储控制器、FAT表/FCB表存储器组成,cPCI存储板主要由Flash存储阵列组成。

图2 存储控制原理框图

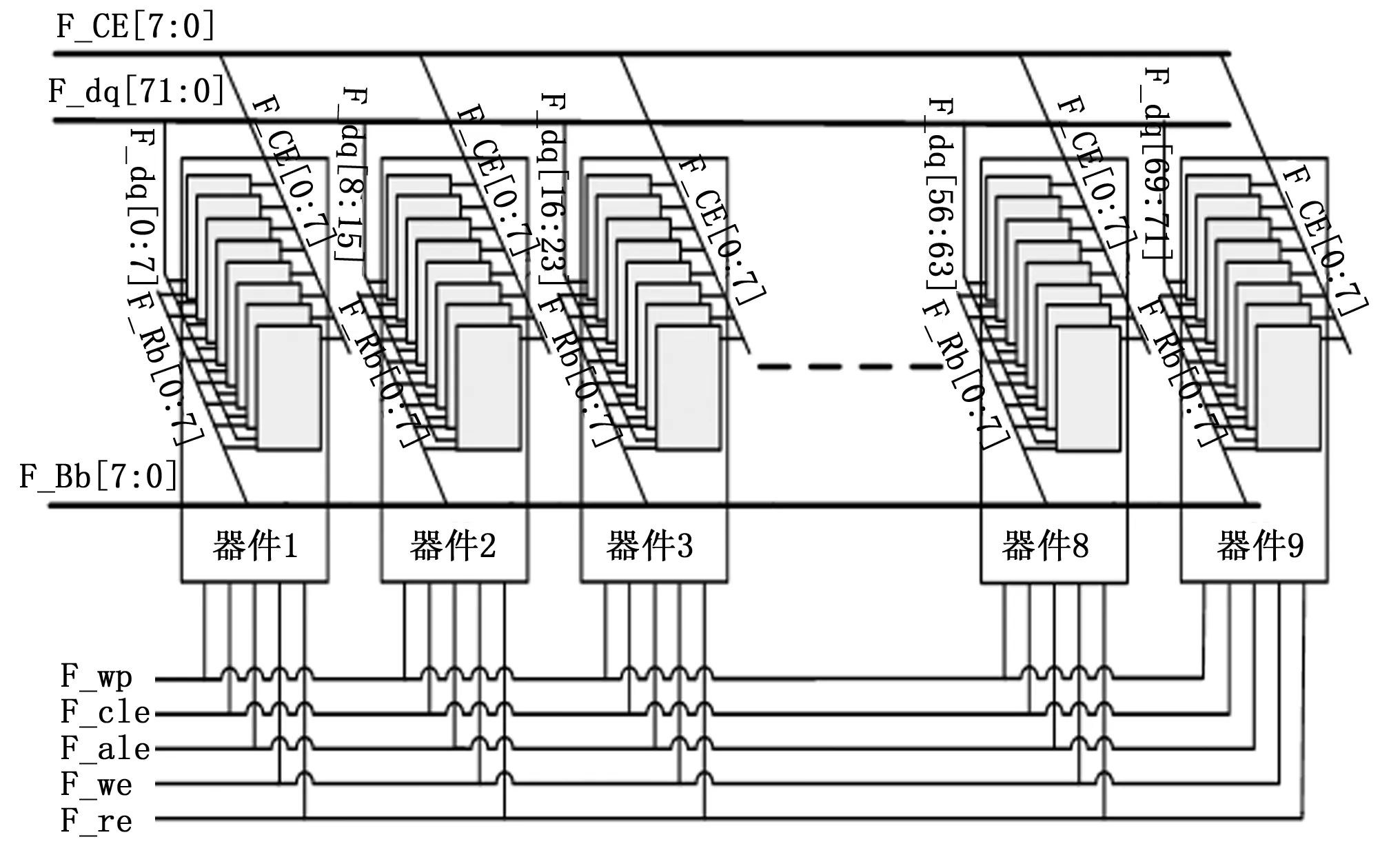

该卫星型号的固态存储器的Flash芯片组由9片64Gb的3Dplus公司三维封装的Flash芯片并行级联而成。组内的9片Flash芯片共用F_wp、F_cle、F_ale、F_we、F_re、F_CE[7:0]、F_Rb[7:0]信号,数据口进行并行扩展 F_dq[71:0]。因此Flash芯片组内的9片芯片的读写和地址控制完全相同,其内部结构如图3所示[4]。Flash芯片组之间相互独立,可以根据具体任务速率要求,选择1~4组Flash芯片组同时工作。

图3 存储阵列扩展结构图

而芯片组内的每一片Flash芯片是由8片三星公司的8Gbits的Flash基片K9F8G08U0M封装而成,其内部结构如图4所示。模块内部8片Flash基片共用I/O[7:0]口,其他信号各自独立。

图4 Flash芯片内部结构

因此,为了提高固态存储器的写入速率,在Flash芯片的8片基片之间进行流水操作。Flash基片的写过程主要分为一下几步:

1)发送写指令和写地址;

2)发送4 096个字节的数据;

3)发送写结束指令。

实际上每一个基片都有一个与单个Page一样大小的缓冲区,当Flash芯片收到写结束指令后,Flash会将当前缓冲区中的数据固化到对应写地址中。从3D plus公司提供的数据手册可以知,一个page的数据从缓冲区固化到Flash中所需要时间为[300 μs-700 μs]。固化时间较长,影响固态存储器的写速率。因此在设计中,充分利用Flash芯片8片基片叠装的特点,采取流水的方式进行编程操作。即通过对8片基片的片选信号ce[7:0]的控制来实现流水操作[5]。其实现过程如图5所示。

图5 Flash芯片流水操作示意图

通过流水操作,使Flash芯片的IO口得到充分的利用,提高了单个Flash芯片的存储速率。

2 传统坏块管理方法

由于NAND Flash的工艺原因,Flash芯片存在一定的坏块是不可避免的,并且当擦除次数达到一定数量之后也会产生新的坏块。为了保证星上载荷数据的完整性,需要通过软件对Flash芯片的坏块进行管理。首先通过读取Flash的每个Block的第一个page的信息建立初始坏块表,在记录、回放和擦除数据时通过对坏块表的访问,屏蔽掉对坏块的操作。并在写和擦除操作时通过读取Flash状态寄存器的信息对坏块表进行更新。

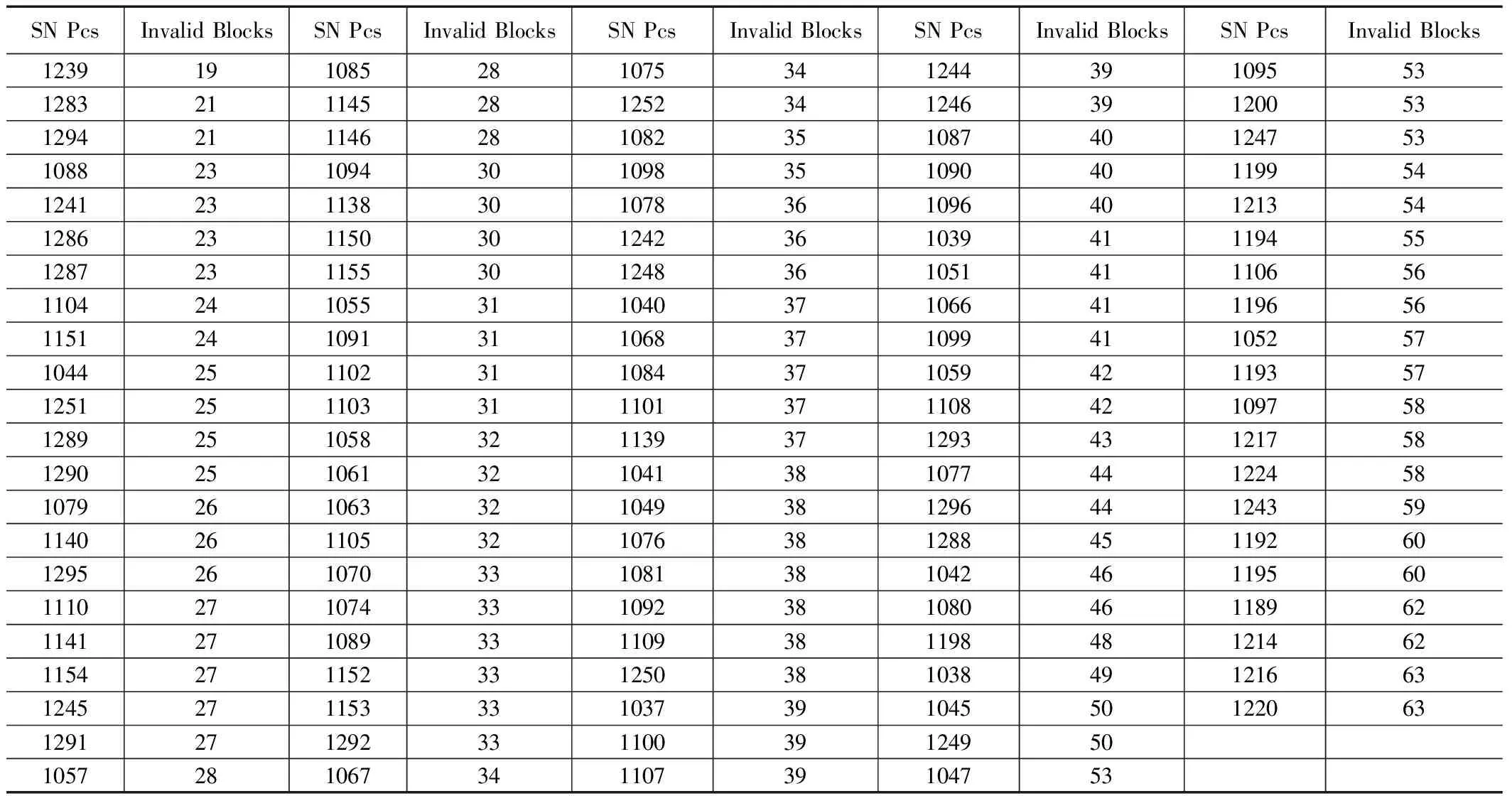

表1 待装机Flash存储芯片坏块数量统计表

当对固态存储器进行数据记录,遇到坏块时。传统的坏块管理方法直接对坏块地址进行跳过。但是,由上述并行存储架构可知,同芯片组,同芯片,同一级流水的基片地址与指令是统一的。即对同一工作内,同一级流水的块写、快读和块擦除仅需查询和更新一次坏块表。因此,当发现芯片组内任意一片基片有坏块需要跳过时,其余的71片基片相同地址的块都要进行舍弃,带来了大量的存储容量的损失[6]。

由图3的存储阵列扩展示意图可知,由于同一工作组的坏块表是统一的,那么工作组内的各芯片、各基片的坏块将被叠加映射。对于该型号的固态存储器,每9片Flash芯片组成一个芯片组,那么同一工作组的坏块数量经叠加映射后即为所有芯片的坏块数总和。

以3D-plus公司提供的坏块表为依据,可知Flash芯片的平均出厂坏块数约为50块。且坏块在Flash中是随机分布的。因此Flash芯片中任意一个block为坏块的概率为:Prandom=50/32768。对于该型号的固态存储器,每9片Flash芯片组成一个芯片组。则在相同块地址中多片Flash出现坏块的概率:

由上述公式可得相同地址出现多个坏块的概率约为0.0084%,因此工作组内各个Flash的坏块数量经叠加映射后即为整个工作组的坏块数总和。

当前,为了减少固态存储器的装机容量损失,从232块配料锁定的Flash中挑选出坏块数较少的108片的坏块个数如表1所示(表格中的数量已进行基片叠加)。按现有芯片的坏块情况进行坏块率预估,该固态存储器是A、B星两台单机,分别装机3T。3T×2的容量均从下表中的芯片中选择装配,共需9×12(工作组)=108片NAND Flash芯片。当每个工作组的坏块独立叠加映射时(即每个工作组都有一个独立的坏块表),根据表1,取坏块较少的108片进行计算。A、B星两台存储器的坏块率约为4159(108片坏块总和)/12(工作组)/4096=8.47%。而当前XX型号,两个工作组共用一个坏块表(即两个工作组的坏块相互叠加映射),A、B星两台存储器的坏块率约为4159(108片坏块总和)/6(工作组)/4096=16.9%。最后经装机实测后,A、B星两台存储器的坏块数为4051,坏块率为16.4%。即Flash坏块的分布离散性较大。

从以上数据可知,即使从232片Flash中选择坏块数较少的108片Flash进行装配。6T的容量,当两组共用一个坏块表时,仅出厂坏块就使固态存储器损失约6T×16.4%=1T的容量。即使每组都有独立的坏块表,存储器的容量损失仍然在6T×8.45%=0.5T左右。并且其余124片Flash芯片再进行装配时,由于坏块相对较多,容量损失将更为严重。

3 星载固态存储器高效坏块管理方法

基于前述,针对目前坏块剔除算法的弊端,本文提出了一种新的坏块剔除算法,采用替补芯片对坏块进行映射补充的办法,大幅降低目前并行存储与多级流水操作带来的坏块叠加效应。

本节首先介绍星载固态存储器高效坏块管理方法的架构设计和实现步骤,接着定义了固态存储器容量损失度的评价指标。该方法充分利用了Flash芯片坏块分布的离散性,对Flash芯片的Block进行一对多的映射备份,解决了一对一映射带来的成本较高的问题,且能够满足星载固态存储器并行存储架构同芯片组,同地址,同一级流水地址统一的需求。该方法通过逻辑地址与物理地址的映射与译码,将Flash芯片组的坏块进行地址映射和替换[7-8]。当备份芯片数量恰当时,能够显著的提高固态存储器Flash芯片的利用率,减少存储器的有效容量损失,降低了单位存储容量的成本。该算法实现的具体步骤如下:

3.1 初始坏块的建立

Flash芯片装机后,首先向存储器发送初始化指令,通过读取每个block第一个page的空闲区的第一个字节,然后经位拼接后,存储在MRAM中,建立整个固态存储器的坏块表[9]。本文以装机38片工作芯片为例进行介绍,其中工作芯片36片,备份芯片2片,该表格格式如图6所示。

图6 固态存储器初始坏块表

坏块表从左到右和Flash_1--Flash_38一一对应,为1表示好块,为0表示坏块。从上倒下分别对应Flash存储芯片的块地址。

3.2 根据分组方式对备份区进行分组映射

由上述(3.1)可知,38片芯片中,有2组为备份芯片。其余36片芯片分为4个工作组,每组有9片芯片。2片芯片无法实现对单个芯片或单个工作组的一对一映射。因此,本设计充分利用Flash芯片的坏块分布离散性较大的特点,即多个连续地址区间内有多个坏块的可能性较小。对备份芯片进行分区映射,如图7所示:将备份芯片分为4个区,分别对应一个工作组。其中地址1-n/4为组1备份区;地址n/4-2n/4为组2的备份区;地址2n/4-3n/4为组3的备份区;地址3n/4-n为组4的备份区。由备份区和工作组的地址长度可知,Flash芯片的备份关系为一对多。

图7 Flash芯片分组备份示意图

为了保持每个组之间的映射关系不相互影响,减少查找表的时间,将备份组也分为4个区间。每个备份组区间的地址深度变为工作组地址深度的1/4。因此其映射关系为4对1,如上图所示,工作组的4个地址区间对应备份组的1个地址区间。当这4个地址区间,即36个Block中有坏块时,将该坏块地址映射到其对应的地址空间中[10-11]。如上图所示,对应颜色的地址空间相互替换。当同一族的4个地址空间中存在3个或3个以上的坏块时,如图8族3所示,只对族3的第2个地址进行替换,其他地址仍有坏块时,直接剔除。

图8 Flash 芯片坏块剔除示意图

3.3 逻辑地址到物理地址的映射

为了屏蔽存储中坏块的地址映射和替换问题,满足并行存储架构的需求。(本文)建立了存储逻辑地址与物理地址的映射表,映射表格式如图9所示。

图9 固态存储器映射表

表中物理地址格式如下。

表1 物理地址格式

例如假设逻辑地址2对应的物理地址为:34’b01111011111001110111111011 00001100则表示其对应的Flash地址为第2组的1,2,3,5,6,7,8片芯片和备份组的第1片芯片。第2组的7片芯片的Block地址为16’0111011111101100;而备份组芯片的Block地址为:{组选信号:Block地址的高14位},即16’b01011101111 11011;Page地址都为001100。即能够通过对物理地址的译码得到Flash的读写地址[12]。

4 性能分析与实验结果

Flash芯片的装机容量损失情况直接反应了坏块管理的有效性。为了评价星载固态存储器高效坏块管理方法的性能,需要量化Flash芯片的利用率。

η=(N-M)÷N

M=8192×Pm×n×4

N=(n×4+m)×32768

式中,M为整个固态存储器因初始坏块需要剔除的坏块数;N为整个固态存储器装机的坏块数;n为每个工作组的Flash芯片数;m为固态存储器备份芯片数;L为每个族的block数,为n×4;Prandom为单个block是坏块的概率。

4.1 仿真结果

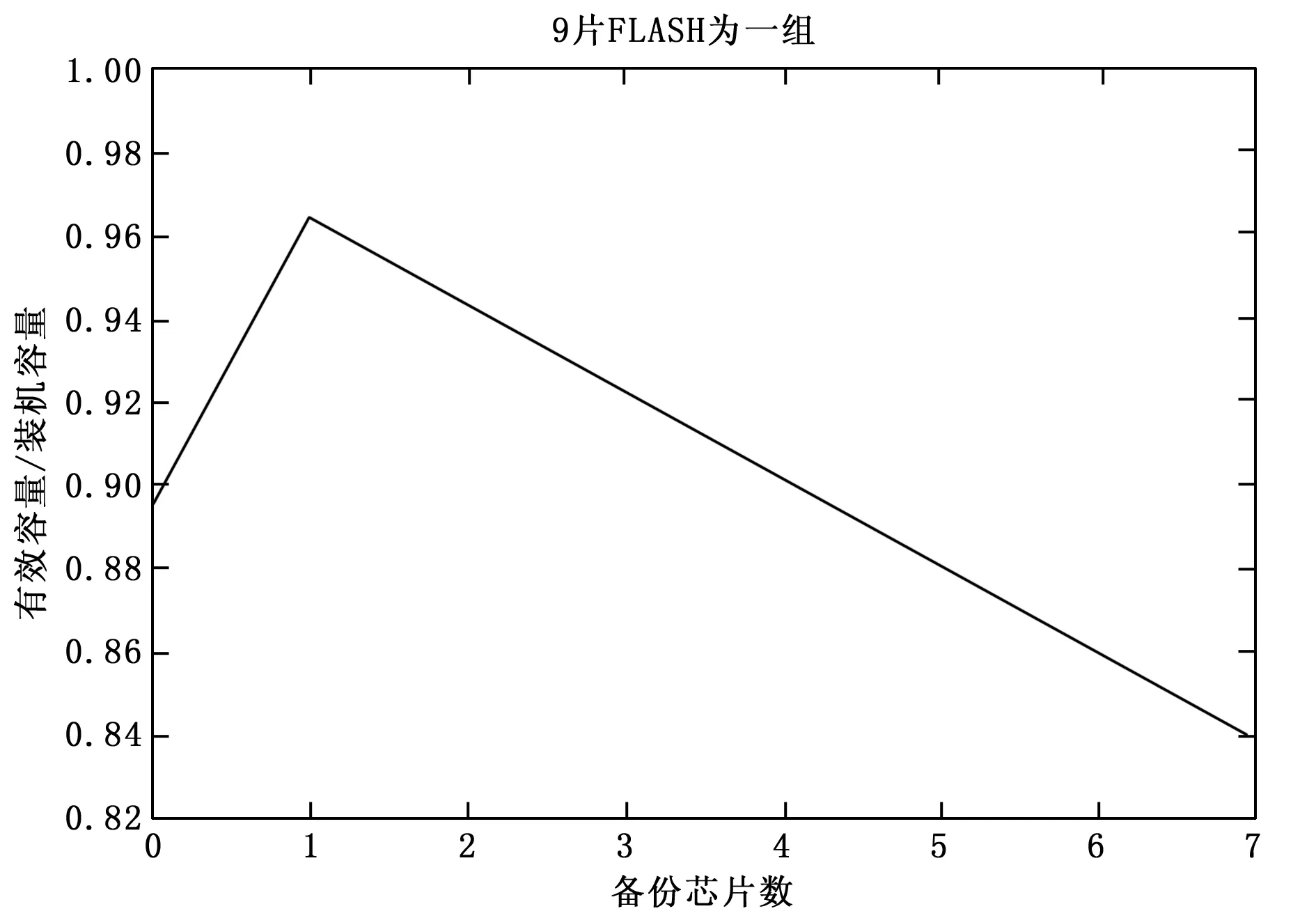

本文以MATLAB为平台建立模型,以表1中实际3D PLUS公司提供的坏块表为初始数据。以每个单板装4组Flash芯片为例,在不同的备份和每组Flash芯片数不同的情况下,对固态存储器的坏块率和容量损失情况进行分析。首先,为了与传统的存储架构进行对比,对每组装9片芯片的情况进行分析。实验结果如图10所示。

图10 备份芯片数和Flash芯片利用率的关系图

由图可知,当固态存储器单板不进行备份时(与传统的存储架构相同),Flash芯片的利用率η约为0.9。当备份1片Flash芯片时,Flash芯片的利用率η达到峰值,约为0.97。并随着备份数量的增多,Flash芯片的利用率逐渐降低。即通过本文提出的存储架构能够显著的提高Flash芯片的利用率,降低星载固态存储器的成本。

在本文所提出的架构下,对各种速率的固态盘的备份情况进行建模分析。实验结果如图11所示。

图11 不同分组情况下Flash芯片利用率

由图11可知,当固态盘速率较低时,由于每次并行工作的芯片数较少,其叠加映射效应不明显。通过备份不仅不能提高固态盘中Flash的使用效率,而且随着备份芯片数的增多,其效率反而变低。从中可得当并行工作的芯片数<5时,没有备份时效率较高;当5≤工作芯片数≤19时,备份1片Flash芯片工作效率较高;当19<工作芯片数≤40时,备份2片Flash芯片工作效率较高;随着并行工作芯片数的增加,备份芯片也需要逐渐递增才能保证Flash芯片具有较高的利用率。

4.2 实际性能验证结果

本文提出的高效坏块管理算法,相对于传统的星载固态存储器并行存储方案,在硬件设计上主要增加了2片MR4A16B来存储地址映射关系。且MR4A16B价格较低,并具有100万次以上的擦写次数,且掉电数据不丢失,具有较高的可靠性。因此该算法能够在不增加硬件成本的情况下,使固态存储器Flash芯片的利用率提高到97%左右。

表2 传统架构下各型号固态存储器Flash芯片的利用率统计表

5 结束语

综上所述,采用替补芯片对坏块地址进行映射补充的办法,可大幅降低目前并行存储与多级流水操作带来坏块叠加效应,能够有效的降低固态存储器装机容量损失,提高了(去掉)存储容量的利用率,降低固态存储器单位存储容量的成本,且维持了原有的硬件需求,对工程上有较高的参考价值,为后续星载超高速率固态存储器的设计奠定了基础。

[1] 王文思, 林宝军. 长寿命星载NAND Flas自适应坏块管理策略[J].计算机科学,2016,43(10):193-195.

[2] 焦亚涛,李娜娜,王雪松. 一种高速固态存储系统的设计与实现[J].电测与仪表,2011,48(551):76-79.

[3] Xiao Nong,Chen Zhiguang,Liu Fang,et al.P3Stor:A parallel,durable Flash-based SSD for enterprise-scale storage systems[J].Science China Information Sciences.2011,54(6):1129-1141.

[4] 贾源泉,肖 侬,赖明澈. 基于NAND Flash的多路并行存储系统中坏块策略的研究[J].计算机研究与发展,2012,49(增刊):68-72.

[5] 闫梦婷,安军社,江源源. 实现流水存储及坏块处理的Flash 控制器设计[J].电子设计工程,2016,24(16):50-53.

[6] 徐瑞瑞,刘 攀,赖晓敏. 宇航固态存储器可靠性设计[J]. 科学技术与工程,2015,15(13):144-148.

[7] Nguyen Q, Yuknis W, Pursley S,et al. A high performance command and data handling system for NASA’s Lunar Reconnaissance Orbiter[C]. AIAA Space 2008 Conference &Exposition.Washington: AIAA 2008.

[8] Takeuchi K. Novel co-design of NAND Flash memory and High-speed solid-state drives [J]. VLSI circuit,2009,44(4):1224-1227.

[9] 王 静,马婷婷,杜 科. 基于Flash阵列的高速存储系统设计[J].制导与引信,2014,35(2):28-33.

[10] Hua Yan, Qian Yao . An Efficient File-aware Garbage Collection Algorithm for NAND Flash-based Consumer Electronics[R]. IEEE Transactions on Consumer Electronics, 2014, 60(4) :623-627.

[11] Han Yong-hao, Wang Shao-yun . Design and implementation of a NAND Flash dynamic bad block management algorithm[J]. Informatization Research,2011,37(3):23-26.

[12] Gyorgy Dan, Heidecker Sandberg, Mathias Ekstedt, et al. challenges in power system information security[J].IEEE Security and Privacy,2011,24(12):62-70.