极化码多模串行抵消算法的FPGA实现研究

2017-09-15陈福钢李晴飞

陈福钢,蔡 青,李晴飞

(南京熊猫汉达科技有限公司,江苏 南京 210014)

极化码多模串行抵消算法的FPGA实现研究

陈福钢,蔡 青,李晴飞

(南京熊猫汉达科技有限公司,江苏 南京 210014)

文章根据极化码的编码结构,提出了一种递推的串行抵消译码策略。利用该策略可以将长极化码译码器改造为支持任意低于该码长的极化码译码,从而降低支持多种服务模式应用的硬件资源开销。

极化码;串行抵消;算法

极化码(Polar Code)是土耳其Arikan教授发现信道组合和拆分以后能够提高信道截止速率这一信道极化现象而提出来的,具有规则的无随机性的编译[1-2]。在采用串行抵消译码算法时,理论证明极化码能够达到Shannon极限且是目前唯一能够达到极限的信道编码方案,且编译码复杂度低,具有巨大的研究潜力和应用前景。正因其理论性能和复杂度的优势,在5G通信标准的短码方案讨论中,极化码击败了LDPC和Turbo码,成为5G控制信道eMBB场景的编码方案。目前已有大量文献针对极化码的SC算法实现展开研究[3-5],然而并没有文献给出一种支持多种模式的极化码串行抵消译码方案。

1 极化码及串行抵消译码算法原理

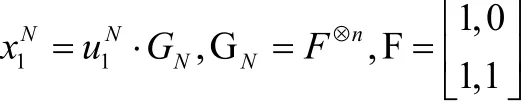

信道极化理论指出,N个独立相同的信道经过组合和拆分以后,部分信道容量趋近于1,部分信道容量趋近于0。利用容量较高的K个子信道传输用户信息比特即可实现有用信息的可靠保护。码长为N的极化码编码结构如图1所示,其中为待编码的信息,

为极化码的码字,W为信道,为信道接收信息。从的角度来看,每一个比特等效的传输信道是一致独立的。而从的角度来看,每一个比特等效的传输信道通过信道极化理论发现各信道容量不一致,选择其中的K个容量较高信道传输有用信息,其序号集合为,剩余的容量较低的信道,序号集合为Ac,传输收发双方已知的比特。如此,uA即为K个用户比特,为确知比特。极化码的编码过程用公式可以表示为:

图1 极化码的编码结构

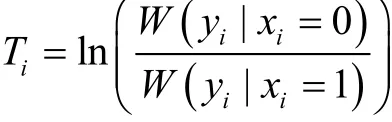

根据图1所示极化码的编码框图,极化码最简单直接的译码算法为串行抵消算法(Successive Cancellation,SC)。根据信道接收信息计算估计值的基本思路是从u1到逐比特进行其对数似然比(Like Lihood Rate,LLR)值的计算,而后硬判决并用于后续比特的LLR计算。定义的LLR值为LLR值为Ti,则:

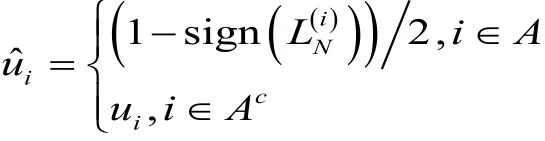

SC算法的目的是通过来计算的估计值,即:

其中SCN[]表示SC算法计算LLR值的过程。根据图1的编码原理,可以进一步推导为:

根据上式即可递推计算出,而后进行硬判决即可。

2 多模SC算法

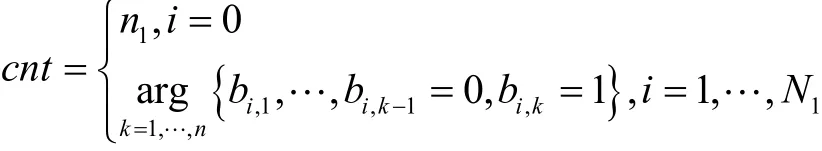

根据SC算法的基本原理,码长为N=2n的SC译码器可以实现任何码长小于N的极化码译码。例如N=32的SC译码器,其可支持码长为2,4,8,16,32的极化码的译码。根据上述的SC递推LLR的计算思路,计算时需要经过n次计算过程,即首先根据i值的大小,选择f或g函数计算N/2个临时LLR值;随后,利用这N/2个值,选择f或g计算N/4个临时LLR值,直到完成的计算。在FPGA实现的过程中,可以通过一个计数器cnt来控制该过程。假设待译码的极化码的码长为,则cnt的初始值为n1,每完成一次中间临时LLR值的计算,即可更新cnt=cnt-1。当cnt=1时即完成一个信息比特的LLR值计算,随后进行硬判决,并更新cnt的值为:

3 结语

其中bi,k为待译码比特ui的序号i的二进制展开的第k位,即:

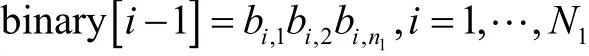

其中bi,n1为最高位。这样做主要是考虑到部分中间LLR值可以不用重复计算,直接用于后续的译码。当uN译码结束时,整个码长为的极化码即完成译码。支持多模的极化码SC译码的FPGA实现框如图2所示。

图2 支持多模的SC译码器FPGA实现框

根据该实现方案,该多模SC译码器实现方案需要的存储空间为(2N-1)Q,其中Q为LLR值的量化比特数。根据f和g的运算方式可知,整个SC译码算法所涉及的运算均为线性运算,不需要乘法器,整个运算过程十分简便。

通过研究分析极化码的SC译码算法,提出了一种递推的译码规则,这样即可将长码的译码过程逐步分解为短码进行进一步译码。采用该译码策略即可利用长码译码器实现任意小于该码长的短极化码的译码,使译码器更加功能化,同时可以节约大量硬件资源开销。

[1]ARIKAN E. Channel polarization:A method for constructing capacity-achieving codes[J].IEEE International Symposium on Information Theory,2008(7):1173-1177.

[2]ARIKAN E. Channel polarization:A method for constructing capacity-achieving codes for symmetric binary-input memoryless channels[J].IEEE International Symposium on Information Theory,2009(7): 3051-3073.

[3]LEROUX C,RAYMOND AJ,SARKIS G,et al. Hardware implementation of successive-cancellation decoders for polar codes[J]. Journal of Signal Processing Systems,2012(3):305-315.

[4]LEROUX C,RAYMOND A,SARKIS G,et al. A semi-parallel successive-cancellation decoder for polar codes[J].IEEE Transactions on Signal Processing,2013(2):289-299.

[5]FAN Y,TSUI CY. An efficient partial-sum network architecture for semi-parallel polar codes decoder implementation[J].IEEE Transactions on Signal Processing,2014(12):3165-3179.

Study on implementation of multi-mode successive cancellation algorithm for polar decoder in FPGA

Chen Fugang, Cai Qing, Li Qingfei

(Nanjing Panda Handa Science and Technology Co., Ltd., Nanjing 210014, China)

A recursive successive cancellation decoding strategy for polar codes based on its implicit structure is proposed in this paper. Using this strategy, the long-length polar decoder can be transformed to support any polarization code decoding below the code length, thereby reducing the hardware resource overhead that supports multiple service mode applications.

polar codes; successive cancellation decoding; algorithm

陈福钢(1982— ),男,安徽滁州人,工程师,硕士;研究方向:卫星通信。