基于软、硬件协同的FPGA软件交联仿真验证技术

2017-09-03刘海山丁怀龙

刘海山,乔 森,丁怀龙

基于软、硬件协同的FPGA软件交联仿真验证技术

刘海山,乔 森,丁怀龙

(北京精密机电控制设备研究所,北京,100076)

针对型号伺服控制系统硬件架构特点,提出一种基于软、硬件协同的现场可编程门阵列(Field Programmable Gate Array,FPGA)软件交联仿真验证技术,利用黑白盒测试相结合的思想,分别建立软件仿真验证环境和硬件仿真验证环境;应用器件建模技术,在软件仿真验证环境中构建一个近似于真实的、虚拟的硬件运行环境;简化传统的FPGA设计验证流程,将验证的重点只放在功能和时序上,在保证验证全面性的前提下提高验证效率;利用故障仿真分析技术,充分检验FPGA软件的可靠性、抵御故障的能力及抗干扰能力。

软、硬件协同;FPGA软件;交联仿真;器件建模

0 引 言

在新型战略武器及运载型号伺服系统的研制中,传统伺服控制系统的单核心处理器硬件架构已无法满足型号的控制要求,越来越多的伺服控制系统引入现场可编程门阵列(Field Programmable Gate Array,FPGA)参与控制,采用数字信号处理(Digital Signal Processing,DSP)高速数字信号处理器+FPGA协同处理器的硬件架构,利用FPGA对数字系统进行逻辑规划,实现对大量A/D、D/A转换通道的控制和总线时序的控制。另外,随着小型化、集成化、轻质化的发展[1],设计者也逐步加大了可编程逻辑器件的引入,通过编写硬件描述语言的方式自主配置硬件资源、设计硬件功能电路模块,取代目前繁多的电路芯片及其外围电路。这使得FPGA软件的重要性不断提高,一旦FPGA软件存在缺陷,将导致FPGA无法实现预期功能。因此,对FPGA软件进行全面、精确、高效的验证技术研究显得尤为重要。

本文根据硬件架构的特点,提出一种基于软、硬件协同的FPGA软件交联仿真验证技术,利用黑白盒测试相结合的思想,分别建立软件仿真验证环境和硬件仿真验证环境,应用器件建模技术在不同的验证级别和验证环境上对FPGA软件的功能、时序进行了全面、精确的验证,并通过对2种仿真验证环境下验证结果的比较分析,不断修正设计模型,逐步逼近整个控制电路的实际参数,使验证结果最终达到收敛状态,实现了设计参数最优化,提高了验证的精度和可信度,并利用故障仿真分析技术[2],充分检验FPGA软件的可靠性、抵御故障的能力及抗干扰能力。

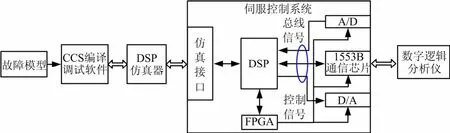

1 控制系统硬件架构

被测伺服控制系统采用DSP高速数字信号处理器+FPGA协处理器的硬件架构,如图1所示。其中,DSP高速数字信号处理器中运行伺服控制软件,主要实现伺服控制系统自检、自诊断、时钟同步、闭环控制及性能补偿功能,并通过1553B总线实现与控制、遥测系统的信息通讯,同时还进行伺服控制系统内部时钟管理及故障诊断。FPGA作为伺服控制系统中逻辑接口器件,主要完成复位逻辑、上电时序控制、外部中断逻辑、外部D/A与A/D转换器片选逻辑、数据总线双向连接、1553B总线控制逻辑等工作,是负责CPU主控板上各数字器件之间的逻辑规划的重要元件。该设计包含6片共24通道A/D转换器、4片共8通道D/A转换器,通过FPGA将1553B总线控制器的地址空间与DSP芯片的zone0区0x2000~0x3fff空间映射,将24通道A/D信号和8通道D/A信号与DSP芯片的zone2区0xc0000~0xdbfff空间映射,使DSP芯片能够以操作内存空间的方式对1553B总线控制器、A/D转换器、D/A转换器进行读写。

DSP芯片的读、写信号相与作为1553B总线控制器的数据锁存信号;握手信号通过逻辑取反使DSP芯片与1553B总线控制器匹配;当产生总线中断或A/D转换完成信号时,向DSP芯片产生中断信号;当需要读写外部器件时,选通总线驱动器,控制方向信号,实现数据的双向流通。

根据控制电路结构和功能要求,FPGA设计中包含复位逻辑模块、上电时序控制模块、A/D片选模块、A/D中断逻辑模块、D/A片选模块、1553B总线控制逻辑模块、数据总线读写控制逻辑模块,各功能模块由顶层模块实例化引用。

图1 被测伺服控制系统硬件架构

2 验证的流程与方法

2.1 器件建模

本文取代传统的利用行为描述语言为被测设计模型提供测试激励的做法,利用器件建模技术对与FPGA接口的DSP高速数字信号处理器、1553B总线接口芯片、电源复位芯片、A/D转换器、D/A转换器等外围电路和器件进行建模,组成仿真模型库,如图2所示。

为被测设计模型提供测试激励,以此在软件仿真验证环境中构建一个近似于真实的、虚拟的硬件运行环境,实现对FPGA软件功能和时序充分全面的验证。

图2 仿真模型库结构

依据器件的工作原理对器件进行功能建模[3],对与FPGA接口的外围器件进行功能分析,结合硬件电路设计提炼出需要建模的引脚(例如:总线信号、使能信号、片选信号等引脚),通过Verilog HDL语言对建模信号按照控制要求进行逻辑描述,包括:信号电平的建立和保持时间、信号电平的幅值等,实现规定的电路动作,从而模拟被测设计模型与外围芯片之间的信号交互。再根据器件的电学特性和延时特性进行时序建模,按照器件设计手册典型时序图中规定的时序要求,在逻辑描述中加入延时信息,以此对器件的延时特性进行模拟。之后将器件模型在ModelSim编译仿真器中进行编译仿真,验证通过后预编译到仿真模型库中,在对被测设计模型仿真验证时直接从仿真模型库中提取,并作为测试激励嵌入到被测设计模型,实现对被测设计模型的仿真验证,同时仿真模型库中的器件模型可在后续类似软件的验证中直接提取调用。

2.2 验证环境的原理与建模

基于软、硬件协同的FPGA软件交联仿真验证环境由软件仿真验证环境和硬件仿真验证环境组成,如图3所示。

图3 软、硬件协同的FPGA软件交联仿真验证环境

软件仿真验证环境是由仿真验证计算机、仿真模型库、Matlab激励数据、Matlab仿真模型、被测设计模型、ModelSim编译仿真器构成的离线闭环验证系统。在仿真验证计算机中,采用白盒测试的思想,利用Verilog HDL语言对与被测设计模型接口的器件进行建模,按照设计要求描述与被测设计模型接口时的规定电路动作,并通过调用顶层模块编写的测试平台(Testbench),与Matlab中预先设计的激励数据一起构成被测设计模型的软激励。在测试平台中,通过不同的任务调度(Task)描述实现特定功能的过程,自动将输入激励施加到被测设计模型中,从而实现功能验证环境的建模。在ModelSim编译仿真器中对被测设计模型进行功能仿真,生成波形文件和覆盖率信息,检验被测设计是否满足设计需求中规定的功能。同时在ModelSim编译仿真器中添加网表文件、标准时序延迟文件、设计约束、测试向量库文件对被测设计模型进行时序仿真,生成性能分析文件,检验被测设计是否满足设计需求中规定的性能指标。仿真结束后,将ModelSim编译仿真器中生成的功能、时序信息以数据文件的形式导出,供测试结果比较分析时使用。利用Matlab对被测设计模型进行建模并仿真,生成的仿真结果与ModelSim编译仿真器生成的数据文件进行比较分析,进一步检验被测设计是否满足设计需求中规定的功能和时序指标要求,同时隔离编译仿真器对被测设计模型带来的不可预见的影响,精确定位设计缺陷,实现软件仿真验证环境下的离线闭环验证。

硬件仿真验证环境是借助于伺服控制系统内部集成的DSP高速数字信号处理器、FPGA、外围电路配合仿真验证计算机、数字逻辑分析仪和各电路控制时序模型所构成的硬件在线动态验证平台。采用黑盒测试的思想,将经过软件仿真验证、环境验证通过后的被测设计的熔丝图文件下载到FPGA中,通过CCS编译调试软件对DSP高速数字信号处理器编程,使DSP高速数字信号处理器输出正常或异常的控制逻辑信号,达到向FPGA施加硬激励的目的,从而真实模拟实际运行环境中的控制逻辑,这种激励方式易于实现,且配置灵活,能够方便地实现对各种控制逻辑的遍历测试。利用数字逻辑分析仪观测并记录FPGA及外围电路物理响应信号的特征及波形,通过与各电路控制时序模型的比较分析,完成FPGA软件在硬件实物上的功能、时序仿真验证,检验在硬件实物上FPGA软件能否满足设计需求中规定的功能和时序指标要求,实现在硬件仿真验证环境下的在线闭环验证。通过对2种仿真验证环境下的验证结果进行分析比较,不断修正设计模型,逐步逼近整个控制电路的实际参数,使验证结果最终达到收敛状态,实现电路参数设计的最优化,完成FPGA软件在不同的验证级别和验证环境上的交联仿真验证。

2.3 验证流程优化

传统的FPGA设计验证流程如图4所示。首先,根据设计说明文档利用硬件描述语言描述系统的行为,并根据行为描述进行寄存器传输级的编译器中间语言描述(Register Transer Language,RTL)级描述,利用专业的编码规则检查工具对RTL描述代码进行规则检查,检验代码的可综合性、可仿真性、可测试性和可重用性;其次,对程序进行功能性仿真,检验描述是否正确;而后进行综合,对综合得到的门级电路进行综合后仿真,查看功能与要求是否一致;最后,将布局布线的时延信息反标注到设计网表中,进行布局布线后仿真,检查设计时序与FPGA实际运行情况是否一致后通过专业自动测试设备进行板级仿真[4]。

图4 传统的FPGA设计验证流程

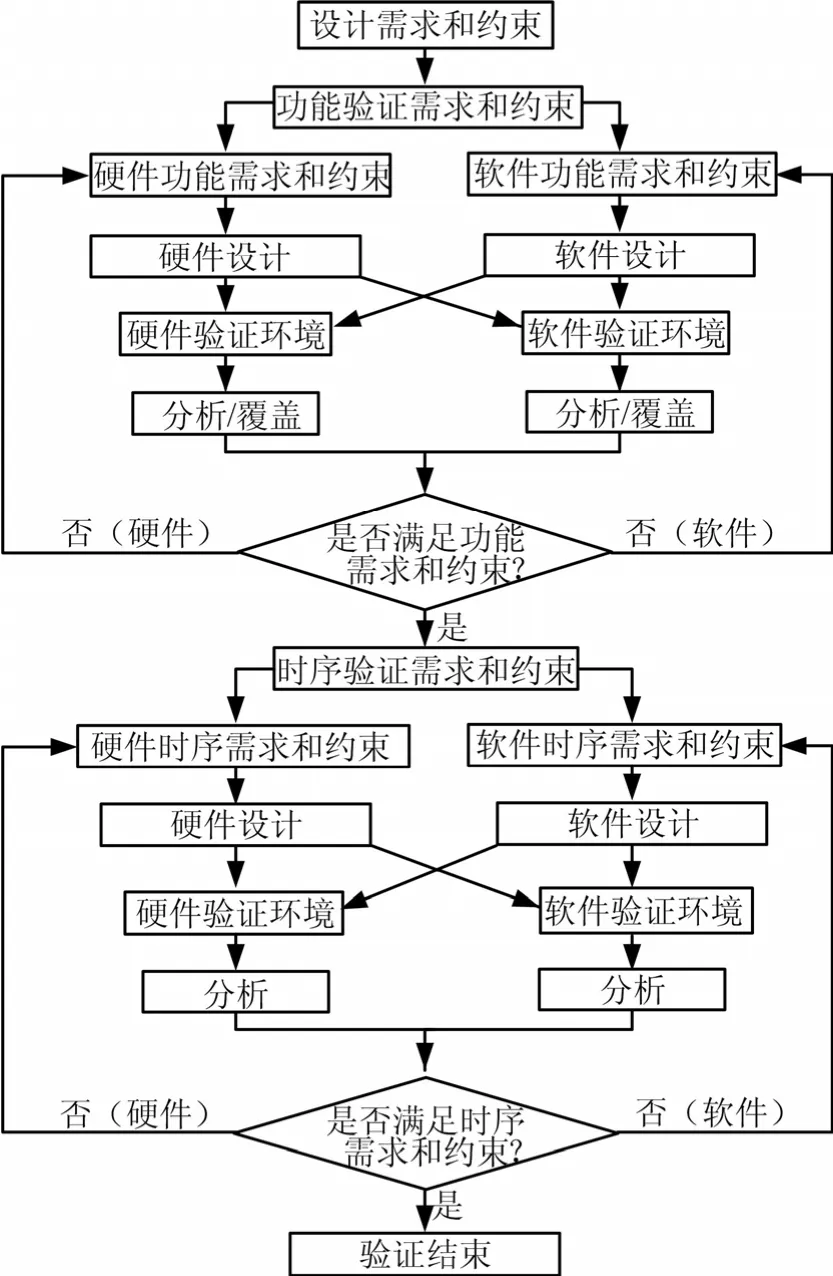

传统的设计验证流程不仅步骤繁琐、流程复杂,且在验证过程中需要大量的专业工具的支持,验证的周期长,测试投入和成本较高,不利于型号的快速研制。本文针对型号伺服控制系统硬件架构的特点和控制要求,减少验证步骤,简化测试流程,提出一种基于软、硬件协同的FPGA软件验证流程,如图5所示。

图5 基于软、硬件协同的FPGA软件验证流程

由于FPGA在整个控制电路中主要完成特定时序下的特定功能,因此将验证的重点放在功能和时序上,而不考虑其他中间过程。根据设计需求和约束分解出功能验证需求和约束,分别在软件验证环境和硬件验证环境中对硬件设计和软件设计进行功能验证,通过波形分析、覆盖率统计检验被测设计模型(包括:软件设计和硬件设计)是否满足功能需求。如果不满足功能需求或约束条件,则检验功能需求和约束是否合理正确,并修正被测设计模型,重复功能验证步骤,直至问题闭合,状态收敛;如果验证通过,则根据设计需求和约束分解出时序验证需求和约束,然后分别在软件验证环境和硬件验证环境中对被测设计模型进行时序验证,通过波形分析、时序分析检验被测设计模型是否满足各电路的时序需求。如果不满足时序需求或约束条件,则检验时序需求和约束是否合理正确,并修正被测设计模型,重复时序验证步骤,直至问题闭合,状态收敛,电路参数稳定可靠;如果全部验证通过则结束验证流程,完成整个验证过程。应用该流程不仅减少了验证步骤,简化了测试流程,提高了测试的效率,同时确保了FPGA软件功能、时序测试验证的全面性[5]。

2.4 故障仿真分析

本文中所提出的故障仿真分析技术首先根据控制电路的结构特性和功能特性建立相应的故障模型,再根据故障模型对被测设计模型施加定向或随机激励,然后将仿真输出结果与理论输出结果进行比较,以此检查被测设计模型的可靠性和容错能力。

软件仿真验证环境和硬件仿真验证环境中,一方面利用软件手段,通过Matlab仿真工具对被测设计模型施加随机序列实现对FPGA软件的故障仿真和分析;另一方面利用硬件手段,通过DSP高速数字信号处理器向FPGA软件输入非法逻辑实现对FPGA软件的故障仿真和分析。如图6所示,在软件仿真验证环境下,利用Verilog HDL语言对故障模型进行描述,然后利用Matlab仿真工具中的接口扩展模块Link for ModelSim与ModelSim编译仿真器连接[6,7],将随机序列和故障模型嵌入被测设计模型,由ModelSim编译仿真器完成对被测设计模型的硬件模拟,再利用Matlab仿真模型对ModelSim中的模拟硬件进行仿真,并输出仿真结果,实现对被测设计模型故障的协同仿真[7]。

图6 基于Matlab的软件故障仿真分析

基于DSP的硬件故障仿真分析如图7所示。在硬件仿真验证环境下,利用CCS编译调试软件按照故障模型对DSP高速数字信号处理器进行编程,添加时序信息,使DSP高速数字信号处理器输出异常控制逻辑,或使输出控制信号的特性(保持时间和变化频率)发生变化或达到临界状态,利用数字逻辑分析仪观测并记录可编程逻辑器件及外围电路物理响应信号的特征及波形,根据响应情况判断FPGA软件各功能模块实现是否正确,检查各功能电路是否由于异常控制逻辑而产生误动作,在真实的硬件环境下检验FPGA软件的可靠性、抵御故障的能力及抗干扰能力[8,9]。

图7 基于DSP的硬件故障仿真分析

3 仿真验证结果与分析

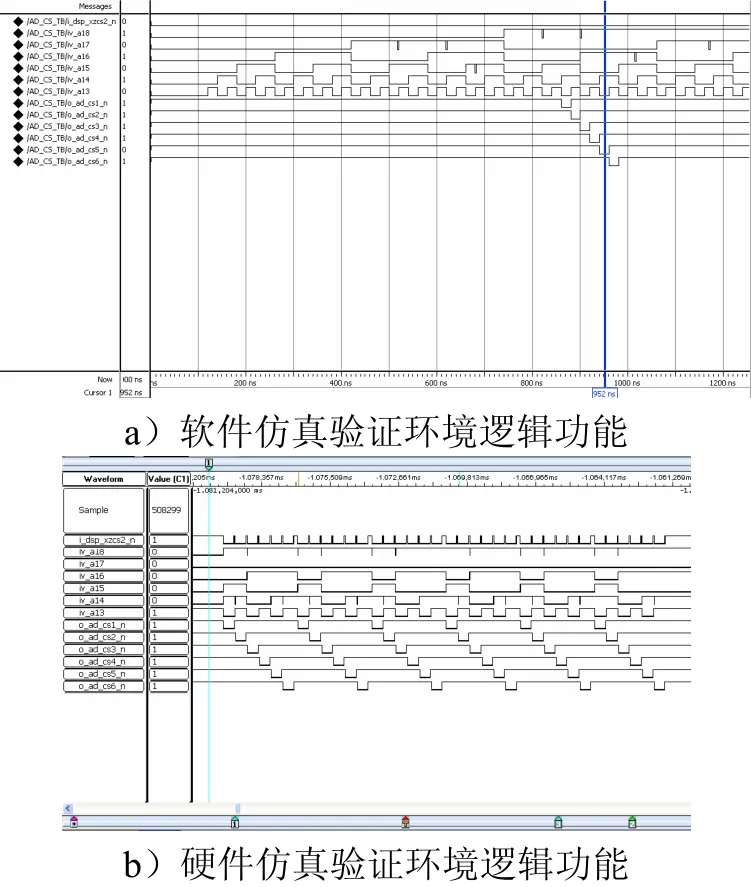

以A/D片选逻辑为例,输入信号分别为DSP芯片内存空间地址区片选信号i_dsp_xzcs2_n、地址总线信号iv_a18~iv_a13,输出信号为A/D片选信号o_ad_cs1_n~o_ad_cs6_n,信号均为低电平有效。DSP芯片依次访问6片A/D转换器,在一个中断周期内,共执行6次该操作,分别对24个通道进行采样,A/D片选逻辑模块功能仿真波形如图8所示。图8a中的毛刺为通过Matlab软件向被测功能模块输入信号中添加的随机干扰脉冲,被测输出信号在软件仿真验证环境中并未由于随机干扰脉冲的引入而出现误动作的情况。图8b中的毛刺为地址总线中加入的随机干扰信号,被测输出信号在硬件仿真验证环境中并未由于随机干扰脉冲的引入而出现误动作的情况。由图8可知,在2种仿真验证环境中的波形相同。因此,被测设计功能正确,且具有较好的抗干扰性。

图8 A/D片选逻辑模块功能仿真波形

图9为A/D片选逻辑模块时序仿真波形。图9a为软件仿真验证环境中的时序仿真波形,光标之间为输入信号有效到输出信号输出的时间,约为24.623 ns;图9b为硬件仿真验证环境中的时序波形,光标之间为输入信号有效到输出信号输出的时间,约为10 ns,优于软件仿真验证环境下的24.623 ns,而设计中的时序约束为30 ns,因此,被测功能模块满足时序约束,且实现了硬件设计的最优化。

图9 A/D片选逻辑模块时序仿真波形

4 结 论

本文利用基于软、硬件协同的FPGA软件交联仿真验证技术实现了对某型号伺服控制系统FPGA软件功能和时序的精确验证,试验结果表明:在软件仿真验证环境中,应用器件建模技术构造一个虚拟的硬件运行环境,为被测设计施加软激励,验证了整个控制系统硬件设计功能的正确性和时序的合理性,同时在硬件仿真验证环境中,利用DSP及外围电路对被测设计施加硬激励,验证了FPGA软件的逻辑功能的正确性和时序的合理性,并通过对2种仿真验证环境验证结果的比较分析,不断修正设计模型,实现了电路设计的最优化。通过验证流程的优化,提高了验证的效率,并利用故障仿真分析技术,充分检验FPGA软件的可靠性、抵御故障的能力及抗干扰能力。

[1] 宋春霞, 胡波, 闫大庆. 2013年各国固体火箭技术进展[J]. 中国航天, 2014(7): 40-45.

[2] 周新蕾, 卿寿松. 软件可靠性保证及相关技术[J]. 质量与可靠性, 2005(6): 25-28.

[3] 孙英侠, 王东, 朱颖. 基于LASAR软件仿真的板级自动测试研究[J].仪表技术, 2014(4): 28-31.

[4] 于斌, 米秀杰. ModelSim电子系统分析及仿真[M]. 北京: 电子工业出版社, 2011.

[5] Mathworks, Ιnc. The link for modelsim documentation[DB/OL]. [2011-08-13]. http://www.mathworks.com.

[6] 门范静, 陈文艺. 基于Modelsim与Matlab/Simulink联合仿真技术的接口与应用研究[J]. 西安邮电学院学报, 2010, 15(3): 72-75.

[7] 文全刚, 孙志刚. 基于黑盒的FPGA功能测试[J]. 微计算机信息, 2004(12): 96-97.

[8] 戚新字. 基于FPGA设计的功能仿真和时序仿真[J]. 航空电子技术, 2005, 36(3): 5l-54.

[9] 李伟, 张刚. 基于FPGA的数字系统设计方法[J]. 太原理工大学学报2008(39): 183-185.

Field Programmable Gate Array Hardware-Software Co-Simulation Verification

Liu Hai-shan, Qiao Sen, Ding Huai-long

(Beijing Research Ιnstitute of Precise Mechatronic and Controls, Beijing, 100076)

A FPGA hardware-software co-simulation technology is presented in this paper based on servo control system hardware architecture and white box and black box software testing method. A software simulation experiment system, approximately equivalent to electric arc furnace system is established based on component modeling technology. The software simulation experiment system just brings forward key technology in the circuit function and timing to ensure the comprehensiveness and high efficiency. The FPGA software can achieve high reliability and good anti-interference ability by the software simulation experiment system and modeling and fault simulating technology.

Hardware-software; Field programmable gate array; Co-Simulation; Component modeling

TP391.9

A

1004-7182(2017)04-0072-06

DOΙ:10.7654/j.issn.1004-7182.20170417

2016-11-26;

2017-04-15

刘海山(1982-),男,工程师,主要研究方向为电力电子与电力传动及嵌入式软件