DSP与FPGA异步数据传输方法

2017-02-03邵晓刚宋茂忠

邵晓刚,宋茂忠

(南京航空航天大学江苏南京211100)

导航卫星信号模拟器能够模拟动态卫星运动过程中接收机接收的卫星信号,为接收机特别是高动态高精度接收机的研制、测试提供模拟环境,同时也可以用于系统级仿真试验[1]。在研制导航卫星信号模拟器时候,需要大量的浮点计算以及基带信号生成,现在多采用基于“DSP+FPGA”的架构来进行导航信号模拟器的研制[2]。DSP作为参数计算部分用来实时产生卫星信号的状态参数、控制参数和导航电文,FPGA主要进行基带信号处理与中频生成,DSP与FPGA数据通信时易产生数据丢失,系统不稳定,需要进行参数传输设计[3]。

1 DSP与FPGA参数传输方案

基于“DSP+FPGA”的架构设计GPS卫星信号模拟器,DSP芯片采用TI公司的高速浮点型处理器TMS320C6713B,具有强大的通用信号处理能力[4]。FPGA采用ALTERA CycloneII系列芯片,门数资源非常丰富,可满足目前绝大多数的信号处理硬件编程和控制[5]。DSP与FPGA之间传输的参数表现为载波控制字、码控制字、复位与启动控制信号、导航电文等。基于上述平台DSP通过32位EMIF总线往FPGA发送上述数据,由于EMIF总线输入的时钟速率和基带读取的时钟速率不同,这就会产生异步数据跨时钟域的传输问题,易造成亚稳态[6],这里通过异步FIFO来缓存DSP端发送过来的大量导航数据[7]。

2 FPGA中异步数据处理

2.1 DSP与FPGA接口设计

DSP与FPGA在硬件上通过EMIF连接,外部存储器接口是TI DSP器件上的一种接口,EMIF可实现DSP与不同类型存EMIF可实现DSP与不同类型存储器的连接[8]。FPGA挂接在DSP EMIF CE2空间,该空间配置为32位异步存储器,如图1所需接口信号。

图1 EMIF接口原理图

TED作为32位数据信号,TEA作为地址信号,TSDWEn作为写使能信号,EXINT为中断反馈信号。其中FPGA地址分配为0x01XY0,其中X作为卫星通道选择,Y作为参数类型选择[9]。

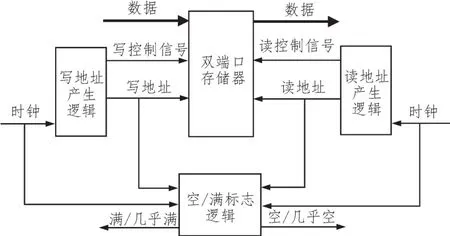

2.2 导航电文的异步传输

在导航模拟源中,为增加数据传输率、处理大量数据流、匹配具有不同传输率的系统为目的而广泛使用异步FIFO缓存器,从而提高了系统性能。异步FIFO缓存器是一个先入先出的双口缓冲器,对连续的数据流进行缓存,防止在进机制和存储操作时丢失数据,为避免频繁的总线操作,数据需集中起来进行存储与读取[10],如图2所示。

图2 异步FIFO原理图

由于导航电文作为最重要的传输参数,而且传输的数据量比较大且只有’1’和’0’两种状态,可作为异步信号处理。异步信号跨时钟域传输时,不满足建立时间(setup time)和保持时间(hold time)[11],会造成采样的不准确,所以我们这里采用了异步FIFO来对导航电文进行缓存。ALTERA的FPGA开发环境中提供异步FIFO内核,我们只需要基于该内核做接口开发,这样可以降低编程难度,提高系统的稳定性。这里主要需要完成的是接口的信号设计,DSP往FPGA中写接口信号包括写时钟以及写使能其中写使能信号表 达 为=20'h01210)&&(TSDWEn==0)。

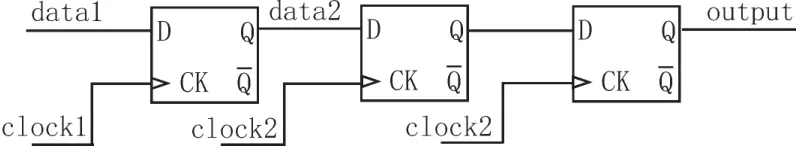

2.3 控制字的异步传输

控制字的计算是基于FPGA中断而进行的,在FPGA基带处理模块中进行时序控制,每隔100 ms产生一个EXINT中断,DSP通过IO口检测到中断后,进行一次载波以及码控制字的计算[12],控制字取32位,每次传输过来由于需要跨时钟域,未免出现在基带中控制字采样时出现亚稳态,所以这里做了一个简单的电平同步器[13]。电平同步器原理图如图3所示。

图3 同步器原理图

简单的同步器,是由两个触发器级联产生的,中间没有其他组合逻辑。这种方法是通过保证后面的触发器在接收前面触发器的输出的时候,前面的触发器已经不再处于亚稳态,实现输出稳定。基带处理之前通过Verilog HDL编程做两级触发器级联[14],控制字数据经过时钟沿同步后,延迟时间为基带时钟域的1~2个时钟周期,这样输出的数据就被同步到基带的时钟域中,避免出现亚稳态,数据丢失[15]。

3 实验结果与分析

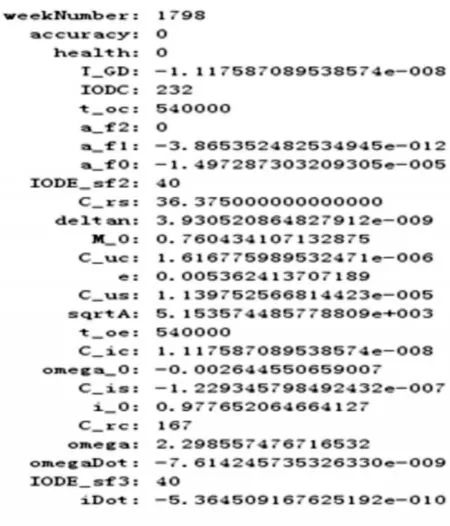

本实验模拟产生13号GPS卫星信号,在Quartus开发环境下根据FIFO内核设计了信号接口,先将DSP计算出的导航电文通过根据时序要求选择地址总线和数据总线通过EMIF发送给FPGA中的异步FIFO,然后再发送启动模拟信号,这样FPGA自己产生时序读取异步FIFO中的导航电文数据,输出NAV_OUT_13,再和生成的伪码CA_CODE13异或输出code13,运用Quartus中的Signal Tap工具抓取了FIFO输出的导航电文以及生成伪码信号,如图4所示。FPGA基带处理生成了13号星的中频信号,在经过DA生成中频模拟信号,最后生成射频信号发射出去。运用GP2015采集射频出去的13号卫星,成功捕获并且解调出导航电文,结果如图5所示。

图4 导航电文与码信号输出

图5 解调出导航电文中的星历参数

4 结论

在设计导航卫星信号模拟源时候,基于“DSP+FPGA”的架构研制,能很好的满足实时性,可靠性要求。但是在DSP[16-17]与FPGA通过总线交互数据时往往会产生跨时钟域的异步数据传输的问题,通过异步FIFO和电平同步器的设计能很好地解决这个问题,减少亚稳态的,提高系统的稳定性。

[1]贾超广,肖海霞.基于卫星信号模拟器的北斗接收机性能测试与分析[J].导航定位学报,2013,1(3):14-16.

[2]任风华,符强,纪元法.GPS模拟器的FPGA实现及其杂散研究[J].计算机测量与控制2013,21(8):2224-2226.

[3]刘志国.卫星导航信号模拟器研究与实现[D].太原:中北大学,2014.

[4]贺玺,杨述斌,曹珩.基于DSP和FIFO信号采集系统硬件设计及实现[J].武汉工程大学学报,2011,33(1):79-83.

[5]冀臻.GNSS卫星信号模拟器研究与实现[D].太原:中北大学,2011.

[6]黄隶凡,郑学仁.FPGA设计中的亚稳态研究[J].微电子学,2011,41(2):255-273.

[7]胡波,李鹏.异步FIFO在FPGA与DSP通信中的运用[J].电子科技,2011,24(3):53-55.

[8]杨龙,李范鸣,刘士建.DSP EMIF与FPGA双口RAM高速通信实现[J].现代电子技术,2014,37(13):10-13.

[9]王普.GPS卫星信号模拟源控制字计算和DSP数据接口[J].电子技术与软件工程,2016:44-45.

[10]司岚山.一种高速大容量异步FIFO存储器设计[D].无锡:江南大学,2013.

[11]唐辉艳,李绍胜.FPGA设计中跨时钟域同步方法的研究[J].铁路计算机应用,2011,20(5):43-47.

[12]肖晶晶.实时多通道GPS信号模拟器的设计与实现[D].北京:清华大学,2011.

[13]赵晓海.跨时钟域信号的几种同步方法研究[J].电子设计应用,2012,20(7):139-144.

[14]张智明.基于FPGA的位同步电路设计[J].现代电子技术,2016,39(4):132-134.

[15]王晓婷.跨时钟域设计方法研究[D].西安:西安电子科技大学,2012.

[16]倪原,刘琦,秦东旭,等.基于双DSP的某飞行器飞行姿态控制系统的软件设计[J].西安工业大学学报,2015(1):52-56.

[17]李忠楠,杨冰,王强,等.一种用于电力线通信的次优交织算法与DSP实现[J].电力信息与通信技术,2014(7):12-16.