采用Mult-tap标准单元PGV以获取精准的Power EM违例

2016-12-01施建安

蔡 琰,季 昊,施建安

(英伟达半导体科技(上海)有限公司,上海 201210)

采用Mult-tap标准单元PGV以获取精准的Power EM违例

蔡琰,季昊,施建安

(英伟达半导体科技(上海)有限公司,上海 201210)

电源电子迁移(Power Electromigration,Power EM)检查在高性能芯片设计中起重要作用。在Voltus进行电源网格分析时,由于在每个标准单元的电源网格视图(Power Grid View,PGV)生成过程中通常只抽取一个电流接入点(tap),从而流入每个标准单元的电流都聚集到一点。但对于大尺寸标准单元,电流实际上是分布到各个接触孔而非集中到一点,因此Power EM结果比实际情况悲观很多。本文描述了一种新的方法,即只对在关键路径上使用并具有高翻转率的大型时钟单元抽取多电流接入点(multi-tap)PGV。通过这种方法,几乎不增加运行时间和内存消耗而使得Power EM准确性得到提高。

电源电迁移;电源格点视图;Voltus

0 引言

电源电子迁移(Power Electromigration,Power EM)检查在高速芯片设计中起着重要的作用。Voltus在进行电源网格分析时会对电源电子迁移进行检查。在先进工艺制程下,由于较高的时钟频率,M1电源网格上会出现一些Power EM违例。这些违例是假的,并且无法用像增强电源网格,把其他标准单元从违例区域移走之类的常规方法修掉。这些假的违例出现的根本原因是单个电流接入点(tap)过于简单,无法正确引导电流分布。因而,在下文中,我们会描述针对大型时钟单元抽取多电流接入点(multi-tap)PGV以获得更精确Power EM违例的方法。

1 常规标准单元PGV生成方法

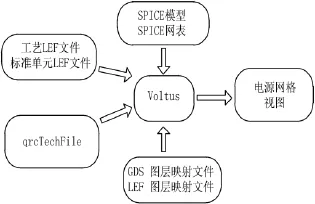

标准单元 PGV生成流程如图1所示,Voltus会读取以下文件以产生标准单元PGV[1]。

(1)工艺LEF文件

图1 标准单元PGV生成流程

(2)标准单元LEF文件

(3)QRC提取工艺文件(qrcTechFile)

(4)GDS图层映射文件

(5)LEF图层映射文件

(6)SPICE模型

(7)SPICE网表

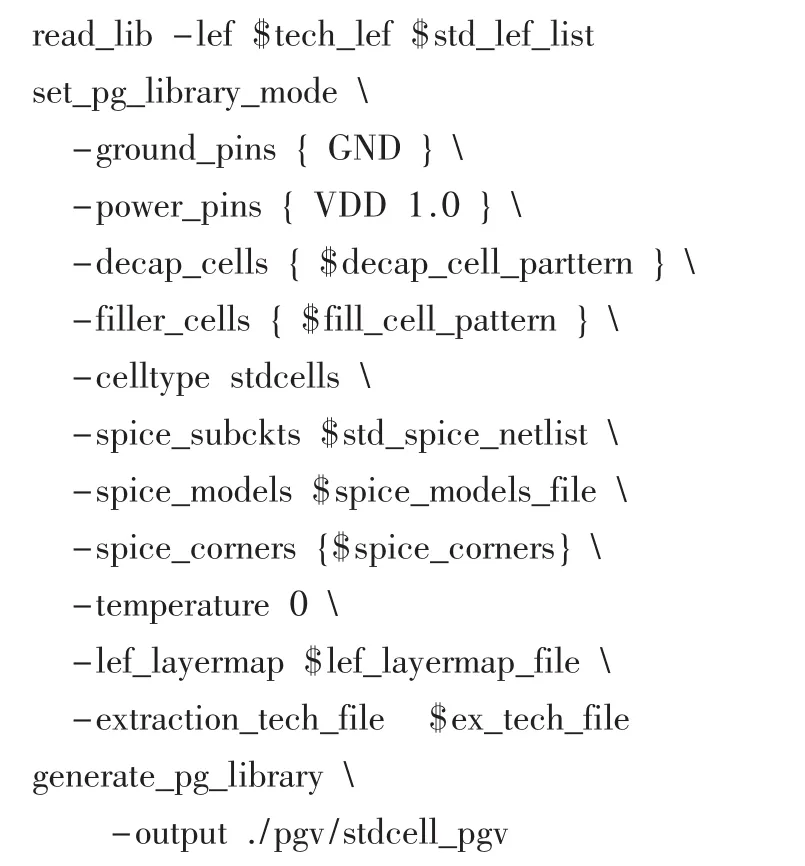

此外生成标准单元PGV,还需要脚本命令辅助。以下是一个范例。

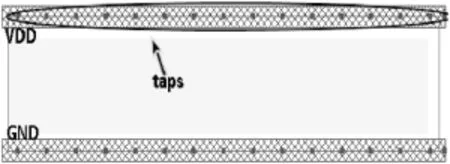

通常PGV会有EARLY,IR和EM三种视图。对于标准单元来说,这三种视图是完全一致的,仅在电源端口包含电流分布参数和SPICE仿出来的电容信息。Tap通常产生在电源端口的中心位置。如图2中的BIGBUFFERD1 PGV所示,VDD和 GND各自只有一个 tap。因此,在 Voltus网格分析中,流入每个标准单元的电流都聚集在一点。这也是为什么假的 Power EM违例发生在tap位置的原因。

图2 BIGBqUFFERD1 PGV图形

2 Multi-tap标准单元生成方法

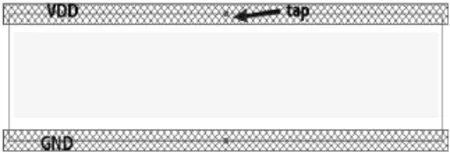

在现实世界中,电流是通过多个V0流入标准单元的。如图3所示,大型标准单元的VDD和GND端口各自有很多V0。所以每个端口只抽取一个tap并不符合实际情况,无法真实反应电流分布。

图3 BIGBUFFETRD1 GDS图形

所以若产生 multi-tap标准单元 PGV,电流是可以均匀分布到所有tap上,结果会更加准确。基于这个方案,我们还需要解决以下三个问题。

(1)哪些标准单需要产生multi-ap PGV?

(2)怎么产生multi-tap标准单元 PGV?

(3)如何在电源网格分析中应用 multi-tap标准单元PGV?

2.1哪些标准单元需要产生multi-tap PGV?

考虑到运行时间,内存消耗等因素,对所有的标准单元进行multi-tap PGV抽取是不明智的。而且在我们的设计中,除了关键路径上的时钟单元,绝大多数标准单元的翻转率很低。所以对大多数标准单元来说,它们的电流不会太高,一个tap已经能够反映电流分布。然而,对关键路径上的时钟单元来说,它们分布的地方有很大几率出现M1电源网格的Power EM违例。因此,我们仅需对大型时钟单元抽取multi-tap PGV。

2.2怎么产生multi-tap标准单元PGV?

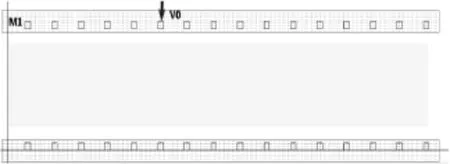

基于标准的PGV生成的流程,我们还可以加一些特殊指令去调节节点之间的距离以控制tap的数量(Voltus默认节点距离是50)。以下是节点距离为 0.15脚本示例。

如图4所示,VDD和GND端口各抽取了16个tap。

图4 Multi-tap BIGBUFFERD1图形

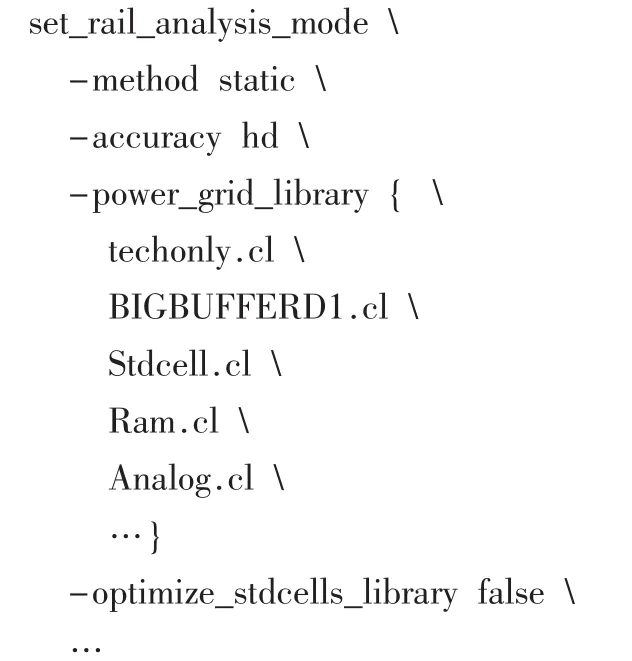

2.3如何应用multi-tap标准单元PGV

当 multi-tap PGV应用于电源网格分析中时,我们必须把这些特殊的PGV放到其他常规PGV的前面。对于有多个PGV的标准单元,Voltus仅会采用第一个非工艺的 PGV。此外,为了能在电源网格分析中保留所有的tap,我们必须关掉“-optimize_stdcells_library”这个选项。以下有个例子。其中BIGBUFFERD1.cl是multi-tap PGV。

3 结果分析

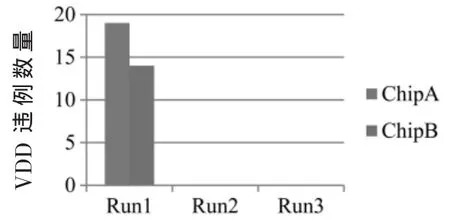

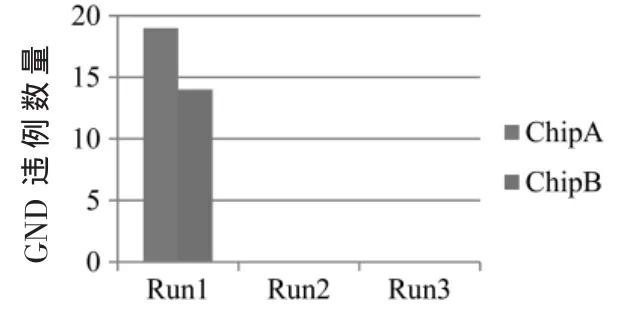

在Power EM分析中,我们的目标是当前流过的电流与可承受的最大电流的比率小于1。在图5~图11中,Run1是标准流程,Run2是对所有标准单元做 multi-tap PGV抽取,而Run3只对大的时钟单元做这样的特殊处理;ChipA和ChipB是两块不同的芯片。

图5 VDD EM违例数量对比图

图6 GND EM违例数量对比图

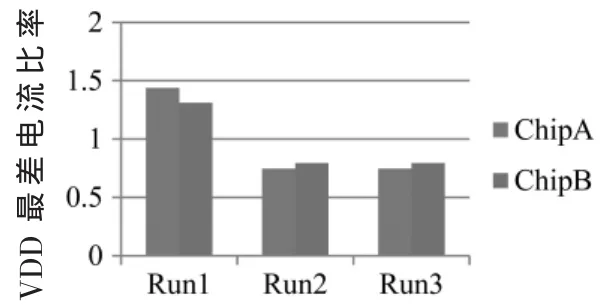

图7 VDD最差电流比率对比图

图8 GND最差电流比率对比图

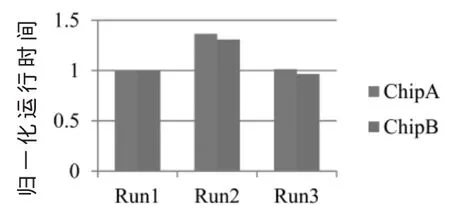

图9 归一化运行时间对比图

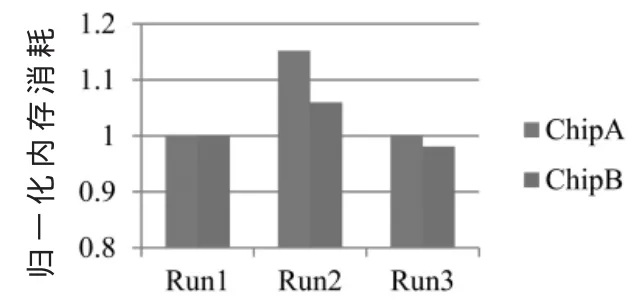

图10 归一化内存消耗对比图

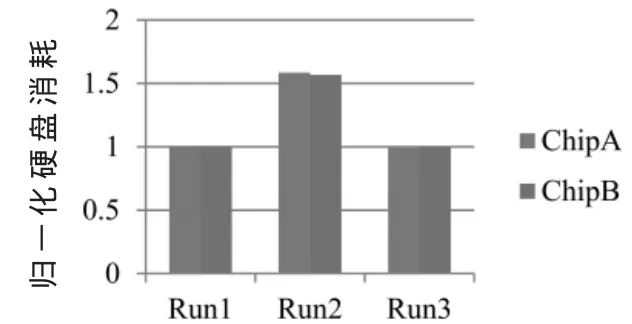

图11 归一化硬盘消耗对比图

从图5和图6中可以看出,对于 ChipA,Run1中产生19个 VDD违例和19个GND违例,Run2和Run3没有违例。同样,对于ChipB,Run1中产生14个 VDD违例和14个GND违例,Run2和Run3没有违例。因此,采用multi-tap标准单元PGV能有效减少违例数量。

图7和图8是最差电流比率的对比图。对于ChipA和ChipB,与Run1相比,Run2和Run3的最差电流比率下降了37%~40%。因此,采用multi-tap标准单元PGV能有效降低最差电流比率,从而减少违例数量。

图9是归一化运行时间的对比图。和Run1相比,Run2运行时间增长了30%~37%,而Run3增长了-0.4% ~0.1%。因此,对所有标准单元进行multi-tap PGV抽取会大量增加运行时间,而仅对大型时钟单元进行 multitap PGV抽取基本不影响运行时间。

图10是归一化内存消耗的对比图。和Run1相比,Run2内存消耗增长了5%~15%,而Run3增长了-0.2% ~0.1%。因此,对所有标准单元进行multi-tap PGV抽取会大量增加部分内存消耗,而仅对大型时钟单元进行multi-tap PGV抽取基本不影响内存消耗。

图11是归一化硬盘消耗的对比图。和Run1相比,Run2硬盘消耗增长了56%~59%,而Run3增长了-0.1% ~0.1%。因此,对所有标准单元进行multi-tap PGV抽取会大量增加硬盘消耗,而仅对大型时钟单元进行 multitap PGV抽取基本不影响硬盘消耗。

综上所述,仅对大型时钟单元做 multi-tap PGV抽取可以在几乎不增加运行成本的前提下去除假的 Power EM违例。

4 结论

通过只对大型时钟单元做 multi-tap PGV抽取可以得到精确的 Power EM违例结果,并且运行时间和内存消耗增加不到2%。在高性能的芯片设计中,这是一种分析Power EM违例的有效方法。

[1]Voltus IC Power Integrity solution User Guide Version 14.21,November 2014.

Application of multi-tap standard cell PGV to capture accurate power EM violations

Cai Yan,Ji Hao,Shi Jian′an

(NVIDIA,Shanghai 201210,China)

Power Electromigration(EM)check plays an important role in high performance chip design.In Voltus rail analysis,the current of each standard cell clusters to one point since there is only one tap extracted by default during standard cell Power Grid View(PGV)generation.But in the real world,for large standard cells,the current distributes to all contacts instead of clustering to one.Therefore,the Voltus power EM result is much more pessimistic than reality.This paper describes a method to only generate multi-tap PGV for large clock cells which are generally used in critical paths with high switching activity.With this method,better accuracy is achieved and runtime and memory are barely increased.

power Electromigration;Power Grid View;Voltus

TN402

A

10.16157/j.issn.0258-7998.2016.08.004

2016-06-16)

蔡琰(1988-),通信作者,女,硕士,工程师,主要研究方向:芯片功耗,压降和电源电子迁移分析,E-mail:docai@nvidia.com。

季昊(1987-),男,硕士,高级工程师,主要研究方向:芯片功耗,压降和电源电子迁移设计流程。

施建安(1981-),男,硕士,主要研究方向:后端设计流程。

中文引用格式:蔡琰,季昊,施建安.采用 Mult-tap标准单元 PGV以获取精准的 Power EM违例[J].电子技术应用,2016,42 (8):25-27.

英文引用格式:Cai Yan,Ji Hao,Shi Jian′an.Application of multi-tap standard cell PGV to capture accurate power EM violations[J]. Application of Electronic Technique,2016,42(8):25-27.