基于Innovus的低功耗物理设计

2016-12-01王志鸿厉媛玥

戈 喆,王志鸿,厉媛玥

(恩智浦半导体,江苏 苏州 215000)

基于Innovus的低功耗物理设计

戈喆,王志鸿,厉媛玥

(恩智浦半导体,江苏 苏州 215000)

为了减少芯片功耗,可靠的低功耗物理设计必不可少。基于新一代布局布线工具Innovus,分四个部分阐述了新的低功耗物理设计流程。这些内容包括:基于低功耗的物理库设计;低功耗布局和优化、基于输入向量的功耗优化;低功耗时钟树协同设计CCOPT(clock concurrent optimization);时钟树后低功耗优化。Innovus作为Cadence全新的布局布线工具,提供基于GigaOpt引擎的功耗驱动优化和高级时钟树协同优化(CCOPT)等方法,有效帮助设计者实现低功耗芯片设计。全新的低功耗物理设计可改善芯片数字逻辑15%功耗。

低功耗;物理设计;功耗驱动;时钟树协同设计

0 引言

高性能与低功耗是当今芯片设计的两个主要方向。对于便携式设备大力发展的今天、物联网应用呼之欲出的明天,低功耗芯片的需求空前高涨,同时也对低功耗芯片的设计提出了更高要求。为了达到更低的功耗,越来越多的低功耗技术被应用到芯片中,比如电源关断技术(Power Shut Off,PSO)[1]、多电压域供电(Multi Supply Power,MSV)、多电压与时钟模式、动态电压频率调节技术(Dynamic Voltage Frequency Scale,DVFS)、存储器分割(Memory Split)、门控时钟(Clock Gating)[2]、门控数据线[3]、多阈值电压设计(Multi-Vt)[4]、衬底偏压调制技术(Back Bias)等。这些方法从芯片设计的各个层面实现低功耗,芯片物理设计是其中的重要一环。本文基于新一代布局布线工具 Innovus,在传统低功耗物理设计流程的基础上,研究了新的低功耗物理设计方法。

1 低功耗物理设计

芯片物理设计是指将芯片电路和代码转变为芯片版图的过程,布局布线是芯片物理设计的核心,本文主要讨论低功耗布局布线技术。

低功耗物理设计内容可以分为两类,一类是对前端各种低功耗设计进行物理实现,比如在物理上对多电压域进行划分和布局;片上电源管理模块和电源开关的放置和连线;通过CPF(Common Power File)控制电平转换逻辑(Level Shifter)和隔离逻辑(Isolation Cell)的加入、电源连接、摆放和优化;时钟门控逻辑的摆放与优化;掉电状态保持寄存器(State Retention Power Gate,SRPG)电源线和单元行的布置等。另一类是在芯片物理层面(如版图、标准单元甚至是器件级别)实现的低功耗设计,这类方法只能在芯片后端设计时实现,比如多阈值电压标准单元库选用,衬底偏压调制技术,低功耗时钟树技术等。

低功耗物理设计的核心是与前端设计相配合,减少芯片内一切不必要的翻转和电容充放电,减少乃至关断芯片内不工作模块的漏电,减少一切时序路径上的性能冗余,以及提供多样化的工作模式以避免在不同应用场合的功耗浪费。精巧的低功耗物理设计能够在保证芯片性能的基础上,有效改善芯片功耗。

2 基于Innovus的改进低功耗物理设计

Innovus是 Cadence公司的新一代布局布线工具,不仅加强了先进工艺和高性能芯片的设计能力,也为低功耗芯片设计提供了强大的功能。本文基于 Innovus,为90 nm低功耗 ARM核微控制器设计了新的低功耗布局布线流程,最终功耗改善超过15%。

2.1低功耗标准单元库设计

好的芯片物理设计离不开一套与需求相匹配的标准单元库,所以低功耗物理设计也需要一套低功耗标准单元库。

2.1.1多阈值电压单元

这是最普遍、也是最有效的方法,通过不同阈值电压单元的搭配,达到芯片性能与功耗的平衡[4]。

2.1.2加长沟道单元与选择性加长沟道单元

加长沟道单元(Gate Length Bias,GLB),又称低漏电单元[5-6]。在数字标准单元电路设计中,通常晶体管的沟长都会选择最小特征尺寸,以获得最好的性能。但是在加长沟道单元中,所有晶体管的沟长都被加长,比如增加20%最小沟长,这是因为随着半导体工艺越来越先进,晶体管漏电流所带来的功耗比例越来越大,通过提高器件沟长,可以有效抑制器件短沟效应和漏致感应势垒降低效应(DIBL),从而减小器件漏电。加长沟道单元通常应用在非关键时序路径上,通过去除芯片中的冗余性能降低芯片功耗,这和多阈值电压单元是一样的道理。

但是,加长沟道单元有一个问题,它会提高芯片动态功耗。因为沟道加长以后,栅面积就会增加,相应的栅电容充放电就会增加,从而增加动态功耗。为了应对这个问题,新的标准单元库引入选择性加长沟道单元(Selective GLB)。选择性加长沟道单元通过有选择地对单元内关键漏电晶体管进行沟道加长,在有效减少漏电的同时将单元动态功耗和性能的损失降到最低。例如,在选择性加长沟道寄存器中,所有与时钟相关的晶体管都不能加长沟道以避免动态功耗大量增加,而所有在寄存器掉电状态下进行状态保持的晶体管都建议增加沟长,以减小芯片低漏电模式下的漏电功耗。

2.1.3多位寄存器

通过将多个(2、4个居多)关联性高的寄存器合并成一个多位寄存器(Multi-bit Flip Flop),可以有效共享每个寄存器内的类同逻辑器件,减少寄存器时钟端口相关联电容,同时更少的寄存器数量也有助于实现更优的时钟树设计[7]。

2.1.4多尺寸梯度单元和极小尺寸单元

引入更多尺寸的标准单元能够为工具提供更多选择,有利于减少芯片在修复时序和转换时间违例时的过量优化。而极小尺寸单元也提供了在某些场合进一步减少功耗的可能。

2.1.5延时单元和保持时序改善寄存器

延时单元(Delay Cell)可以提供大延时,专用于修复保持时序违例。但原有库中某些延时单元提供大延时的效率并不理想,新库对此进行了改进设计。

新库通过设计特别的扫描路径保持时序改善寄存器,减少系统保持时序违例,同时不影响系统功能路径时序,改善芯片功耗[8]。

2.2低功耗布局与优化

一个好的布局和优化不仅需要考虑系统时序和布线拥挤程度,也需要考虑整个系统的功耗水平。在布局和优化阶段,标准单元的选取、物理摆放、等价逻辑转换、非关键路径功耗优化以及系统的总加权绕线长度等因素都与系统的功耗息息相关,如何在保证系统性能和绕线的基础上降低功耗是低功耗设计的关键。在这方面,Innovus的 GigaPlace和 GigaOpt引擎为设计者提供了强有力的支持。通过Innovus的功耗驱动(power-driven)布局和功耗驱动优化,可以有效开展三维驱动设计。

2.2.1布局与优化方法分析

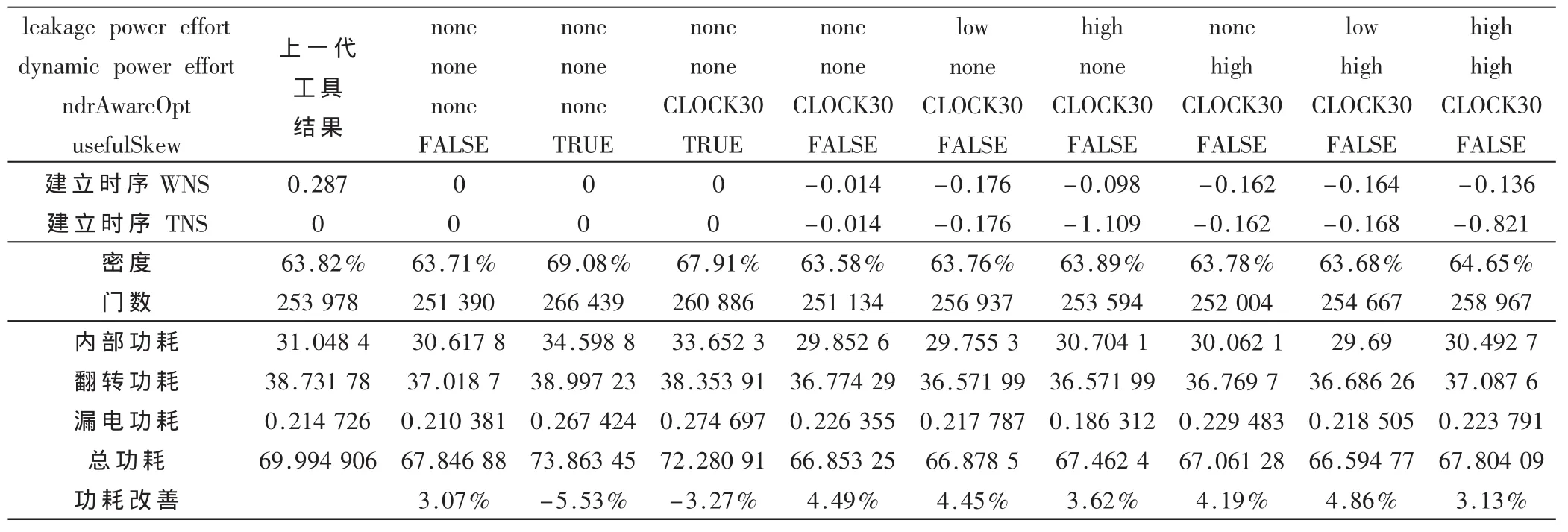

为了达到最优效果,本文对Innovus进行了多项测试,结果如表1。

从表 1中可以看到,Innovus通过新的功耗驱动引擎,在没有任何功耗优化的设置下,可改善总功耗3%。当引入更多的功耗优化选项后,功耗最大可改善近5%。设计者可以根据芯片的应用需要,对动态功耗和静态功耗的优化比例进行选择,工具可以根据选择做出优化策略的改变。另外,Innovus可以在布局阶段考虑时钟树特殊布线的需求(ndrAwareOpt),从而与时钟树之后的设计更加匹配。本文也注意到,Innovus提供的 “有用偏时”选项(usefulSkew)结果并不理想(本文也追踪比较了时钟树之后的结果),需要进一步调试。

表 1显示,当静态优化程度(leakage power effort)很高时,功耗整体优化结果并不好。这其中的一个原因是90 nm工艺静态功耗所占比例太低,另一个原因就是我们采用了加长沟道单元。加长沟道单元在大大降低器件漏电的同时,也会显著提高器件的动态功耗。工具如果不能很好地从全局进行分辨取舍,就会影响功耗优化效率。所以本文给出的建议是,禁止在布局和优化阶段使用加长沟道单元,引导工具更多地通过高阈值电压单元和小尺寸单元优化静态功耗。加长沟道单元可以在时钟树后有选择的进行使用。

2.2.2输入向量驱动功耗优化

动态功耗的产生与芯片的运行状态息息相关,默认情况下,工具使用默认的翻转率来进行动态功耗的估算,这会与实际情况有很大偏差,在这种情况下进行动态功耗优化,势必影响功耗优化效率。Innovus支持输入向量驱动(VCD driven)优化,本文测试结果如表2。

表2显示,工具在有特定输入向量驱动的情况下,可针对此输入模式进行精准动态功耗优化(vector basedoptimization),从而有效改善(9.3%)此工作模式下的动态功耗优化效果。所以本文建议在进行芯片物理设计时,可以加入典型芯片工作模式输入向量,帮助工具更好地优化芯片功耗。

表1 布局与优化测试结果

表2 输入向量驱动功耗对比 (mW)

2.3低功耗时钟树设计

时钟树综合是低功耗物理设计的重要内容,因为即使广泛采用门控时钟,芯片时钟系统还是占据了整个芯片数字逻辑约40%的功耗比重。通常低功耗时钟树的设计方法有:

(1)分析时钟树结构,设计合理时钟树综合方案。

(2)设置合理的时钟偏斜(clock skew)和转换时间(transition)要求。

(3)尝试不同缓冲器或倒相器时钟树方案,一般避免使用大尺寸(功耗大)和小尺寸(片上偏差 OCV大)单元。使用低阈值单元进行时钟树综合。

(4)在片上偏差可接受范围内,推荐多使用小尺寸门控时钟单元。门控时钟单元尽量靠近其驱动单元放置。

(5)使用电阻电容小的金属层进行时钟树布线,使用多孔(multi-cut)布线。

(6)尽可能多地使用时钟树特殊布线,可有效减小时钟树电阻和耦合电容。

(7)使用多位寄存器。

现在低功耗时钟树的主流趋势是时钟树综合并不需要以“零时钟偏斜”为目标。因为为了减小时钟偏斜,时钟树上往往需要引入大量逻辑进行平衡,但很多时候这是没有必要的,特别对于性能要求并不高的微控制器来说。允许时钟偏差,对数据路径和时钟路径协同优化,避免引入不必要时钟树逻辑,在满足时序要求的同时减少功耗,这就是时钟树协同优化(CCOPT)的低功耗时钟树设计方法。

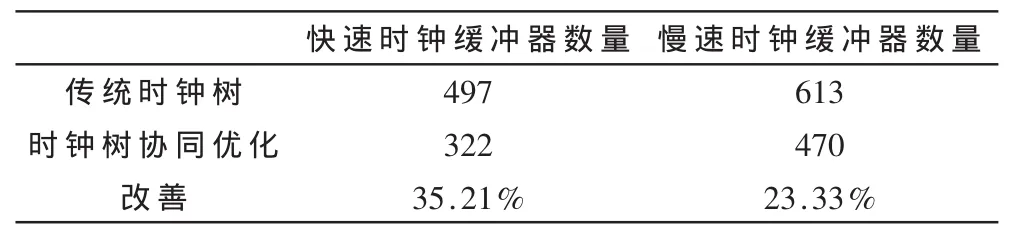

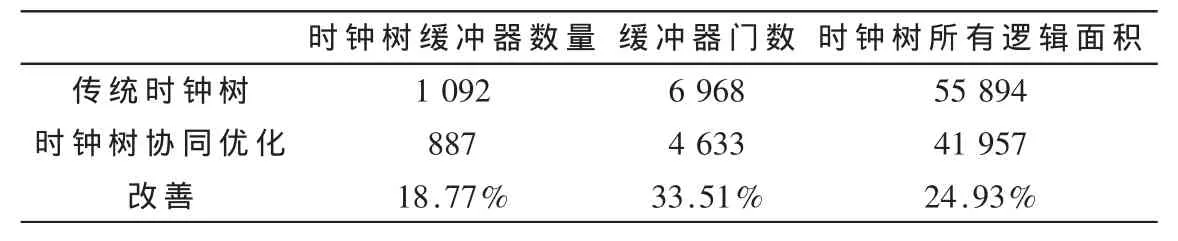

Innovus使用新一代CCOPT引擎,帮助设计者进行良好的时钟树协同优化设计。本文对两块芯片分别进行测试,结果分别如表3和表4。

由表3和表4可知,通过时钟树协同优化,可大大减少时钟树上的逻辑数量,从而有效减小时钟功耗。虽然在后续时序优化中,数据路径上引入的逻辑数量会有所增加,但由于数据路径的翻转频率大大低于时钟路径,所以并不会对整体功耗产生太大影响。

表3CCOPT优化结果比较(芯片1)

表4CCOPT优化结果比较(芯片2)

2.4时钟树后低功耗设计

时钟树综合后,芯片设计主要通过逻辑单元替换减少功耗。由于时钟树后芯片的时序计算越来越准确,这时可以通过减小逻辑单元尺寸、替换高阈值单元、替换加长沟道单元等方法进一步将非关键路径上的冗余性能转换为功耗节省。

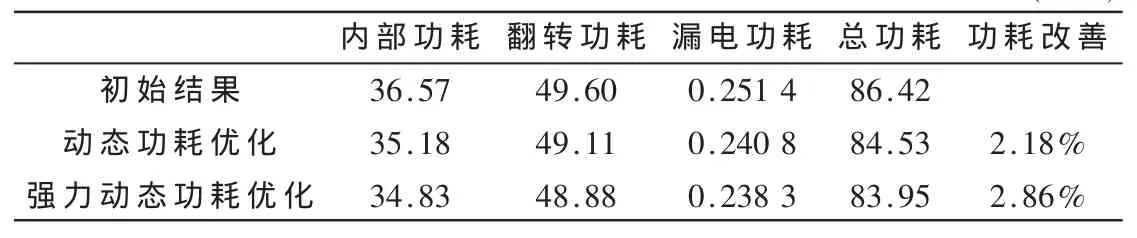

设计者可以通过Innovus的动态功耗优化命令(opt-DynamicPower)进行单元替换,在满足时序的前提下优化功耗,通过测试(表 5)可以看到这能够带来 2~3%的功耗改善。这一过程同样支持输入向量驱动,并能达到更优效果。

在绕线与绕线后优化阶段,Innovus的功耗优化能力同样得到改善,经测试与上一代工具相比,功耗减少1.4%。如果在绕线后进一步打开“面积优化”(area reclaim)选项,功耗能够进一步改善4.6%。

在这个阶段,设计者可以考虑替换更多加长沟道单元进入芯片以有针对性地改善芯片静态漏电。通常而言,静态节点和准静态节点可以放心使用加长沟道单元,低翻转率节点也可以考虑使用加长沟道单元,高翻转率节点不能引入加长沟道单元,低漏电模式下不掉电的单元应考虑加长沟道(典型的如SRPG中的常开锁存器)。

对于芯片中数量巨大的保持时序违例,设计者可以通过优化延时单元与缓冲器使用组合的方法来减少使用数量,降低功耗。

最后在时序违例基本干净以后,能够通过PBA(Path Based Analysis)方法进一步去除时序路径上的性能冗余,减少不必要的功耗。这个步骤通常在静态时序分析(STA)工具中进行,比如Cadence的Tempus。

表5 动态功耗优化结果比较 (mW)

3 结论

本文借助于 Cadence新一代布局布线工具 Innovus,对传统低功耗物理设计流程进行了全面优化。内容包含低功耗标准单元库设计,低功耗布局和优化设计,低功耗时钟树设计和时钟树后低功耗设计。通过新的工具和方法,芯片数字部分功耗可改善15%,效果显著。

[1]HUANG P,XING Z C,WANG T R,et al.A brief survey on power gating design[C].Solid-State and Integrated Circuit Technology(ICSICT),2010:788-790.

[2]ZHANG Y L,TONG Q,LI L,et al.Automatic register transfer level CAD tool design for advanced clock gating and low power schemes[C].SoC Design Conference (ISOCC),2012 International:21-24.

[3]GE Z,ZHANG J L,TAN M L.Module-based bus gating methodology in low power SoC design[C].27thIEEE International SOCC,Design Track Digest,2014:4-5.

[4]RAO S M,BHATNAGAR H.Power reduction technique using multi-vt libraries[C].System-on-Chip for Real-Time Applications,Proceedings.Fifth International Workshop,2005:363-367.

[5]GUPTA P,KAHNG A B,SHARRMA P,et al.Gate-length biasing for runtime-leakage control[J].IEEE Trans.Computer-aided design of integrated circuits and sysntems,2006,25(8):1475-1485.

[6]HU J P,WANG J.Standard cell design of a low-leakage flip-flop with gate-length biasing[C].ASIC(ASICON),2011 IEEE 9th International Conference,:361-364.

[7]SANTOS C,REIS R,GODOI G,et al.Multi-bit flip-flop usage impact on physical synthesis[C].Integrated Circuits and Systems Design(SBCCI),2012 25th Symposium,pp.1-6.

[8]GE Z,TAN M L.Scan-hold-timing-friendly flip-flop to improve chip routing and power[C].IEEE International SOCC 2015,Design Track Digest,Sep 2015:78-79.

Low power physical design in Innovus

Ge Zhe,Wang Zhihong,Li Yuanyue

(NXP Semiconductor,Suzhou 215000,China)

To reduce chip power,a reliable low power physical design is necessary.This paper introduces a improved low power physical design flow based on new PR(Place and Route)tool Innovus,from low power physical library design,to power-driven,vcddriven placement and optimization,to low power CCOPT(Clock Concurrent Optimization)design,and to more low power optimization after CTS.Innovus is Cadence next generation PR tool,which brings a lot of low power features to help designer implement low power design,such as GigaOpt power-driven optimization and advanced CCOPT.Improved low power physical design helps reduce 15%digital power of chip.

low power;physical design;power driven;clock concurrent optimization

TN402

A

10.16157/j.issn.0258-7998.2016.08.003

2016-06-16)

戈喆(1982-),男,硕士,主要研究方向:数字电路后端物理设计。

王志鸿(1980-),女,硕士,主要研究方向:数字电路后端物理设计。

厉媛玥(1977-),女,硕士,主要研究方向:数字电路后端物理设计和时序分析。

中文引用格式:戈喆,王志鸿,厉媛玥.基于Innovus的低功耗物理设计[J].电子技术应用,2016,42(8):21-24.

英文引用格式:Ge Zhe,Wang Zhihong,Li Yuanyue.Low power physical design in Innovus[J].Application of Electronic Technique,2016,42(8):21-24.