倍增组值算法抑制PAPR的FPGA实现*

2016-11-30何维武谭淇文曾康娟

何维武,谭淇文,曾康娟

(重庆金美通信有限责任公司,重庆 400030)

倍增组值算法抑制PAPR的FPGA实现*

何维武,谭淇文,曾康娟

(重庆金美通信有限责任公司,重庆 400030)

在以前的OFDM系统PAPR研究中,提出了倍增组值算法,并做了较多理论分析,同时采用MATLAB仿真软件验证了倍增组值算法的可行性。基于此,进一步深入研究如何利用FPGA实现倍增组值算法抑制OFDM系统的峰均比,提出了在FPGA中实现峰均比抑制模块设计方案并对其加以验证。验证结果证明,提出的在FPGA中实现峰均比抑制模块设计方案简单,硬件资源占用较少,而且抑制峰均比效果较好。

正交频分复用;倍增组值算法;门限;均值模块;降峰均比模块

0 引 言

正交频分复用(OFDM)技术是一种应用广泛、前景明朗的调制解调、复用技术。针对峰均比存在的缺点,很多研究者提出了许多不同的解决办法。笔者也在之前的研究中提出了基于PTS技术[1]的倍增组值算法[2]。本文基于Xilinx公司的软、硬平台,主要研究倍增组值算法抑制PAPR的FPGA实现。所选用的芯片为Spartan3E,型号为xc3s500e-5fg320。

1 倍增组值算法的FPGA实现

1.1 模块的组成

图1所示为倍增组值算法的实现图,基本可以分为如下几大模块:倍增模块;IFFT模块;优化因子处理模块;降峰均比模块;与门值比较模块;ROM模块[3]。

1.2 倍增模块

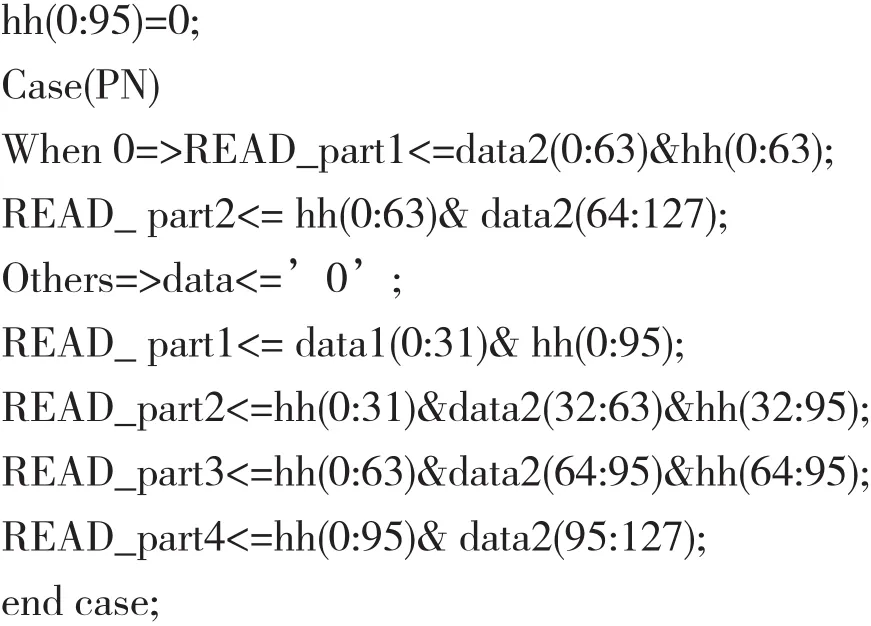

倍增模块是对64个序列做2倍过采样后,再对这128个序列[4]进行分组。倍增组值算法的实现过程为:当激励信号[5]PN=1时,首先让64个映射数据进入倍增模块,并保存在ROM模块里,同时把64个数据中间插入64个0,使其长度变为128。然后,分成2组数据,分别为part1和part2,如图2所示。在长度为64的part1后面加上64个0,使其得到长度为128的READ_part1;在长度为64的part2前面加入64个0,使其得到长度为128的READ_part2。这样通过倍增模块得到的复数输出为:{READ_part1_re,READ_part1_im}和{READ_ part2_re,READ_part2_im}。当激励信号PN=others时,关门映射数据进入此模块,并且将此时ROM内的数据分成4组。

图1 倍增组值算法的模块组成

图2 倍增模块原理

倍增模块的主要程序为:

1.3 IFFT模块

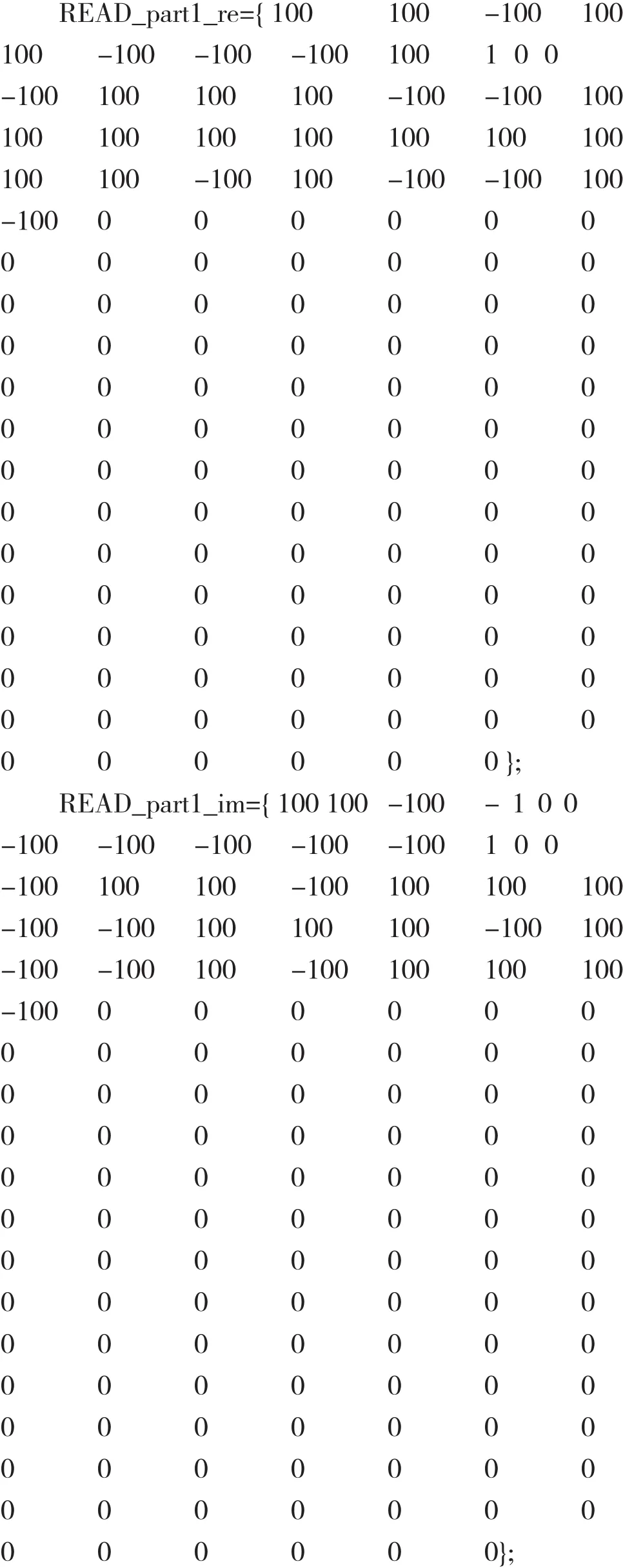

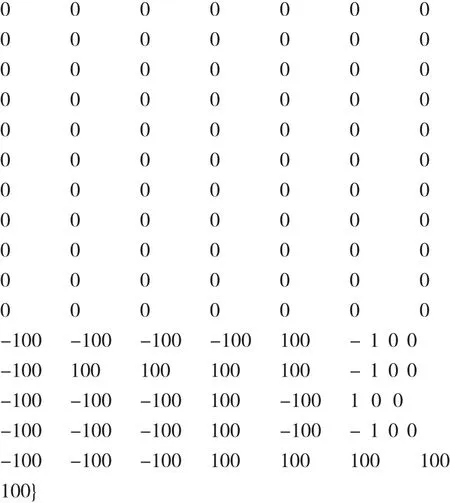

IFFT模块采用IPCORE中的流水结构来实现IFFT功能。点数为128(经过过采样所得的),位宽为16。一帧数据通过倍增模块后,再把这些数据都扩大100倍。这是因为要把浮点数转化为定点数来实现。于是,有:

其他参数初始值为:fwd_inv_tb:std_logic:='0';fwd_inv_we_tb:std_logic:='1';start_tb:std_logic:='1';

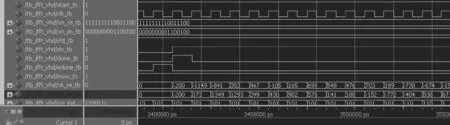

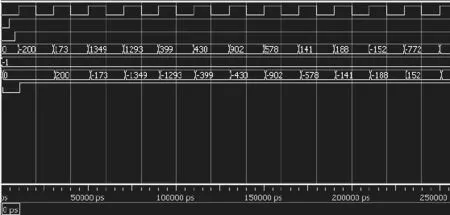

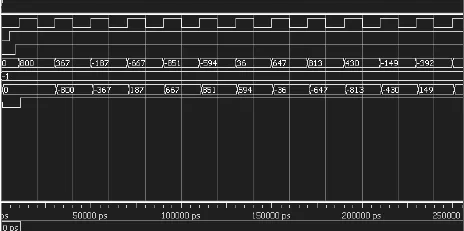

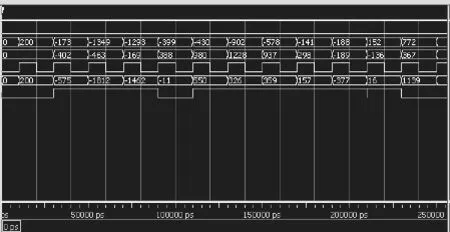

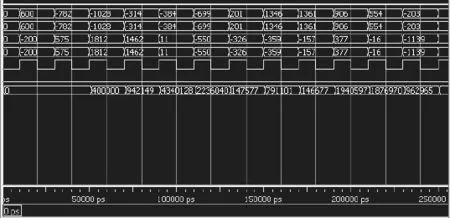

通过IFFT模块后的实现结果分别如图3、图4所示。

图3 IPCORE1处理后的第一组时域数据

图4 IPCORE2处理后的第二组时域数据

由图3、图4可知,只有在edone信号变高,且在下一个周期信号done变高时,才输入结果。此时,dv一直为高,表明输出有效,所得结果为24位的数据。

1.4 优化因子处理模块

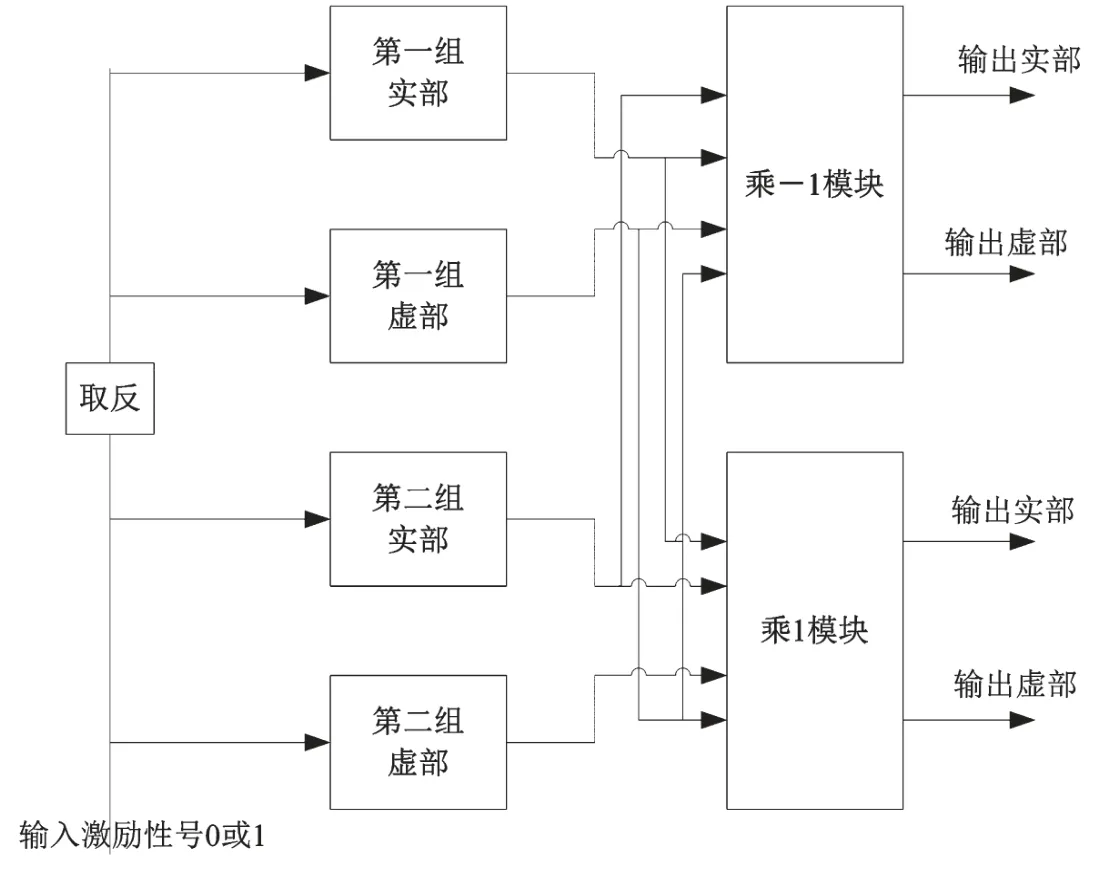

优化因子处理模块原理图,如图5所示。

图5 优化因子处理模块原理

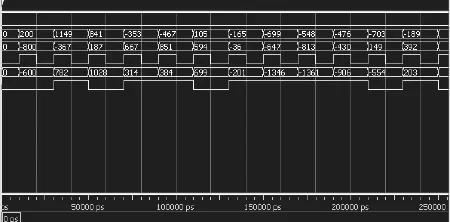

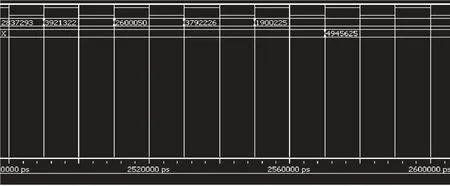

优化因子处理模块由ROM存储器和乘法器组成[6]。把IFFT模块输入进来的数据作为已知条件,时钟周期设为20 ns,于是可得优化因子处理模块的实现图,如图6、图7、图8和图9所示。

从图6、图7、图8和图9可以看出,优化因子处理模块的实现结果为有效数据,但存在一定的延时。由于它们所占用的器件资源相当少,因此没有列出。

图6 第一组的实部乘-1后的数据

图7 第一组的虚部乘-1后的数据

图8 第二组的实部乘-1后的数据

图9 第二组的虚部乘-1后的数据

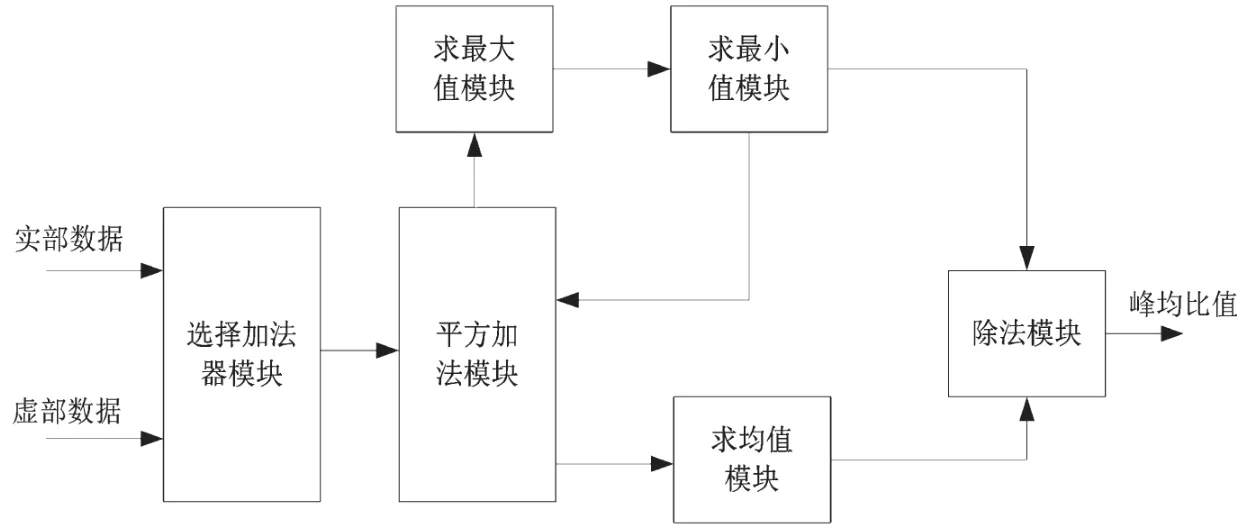

1.5 降峰均比模块

降峰均比模块是一个较大的模块,主要包括选择相加模块、平方相加模块、最大值模块、最小值模块、均值模块、除法模块,如图10所示。

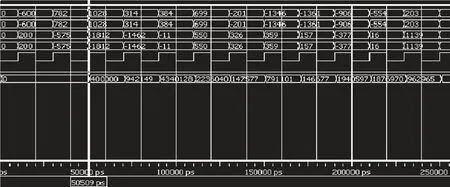

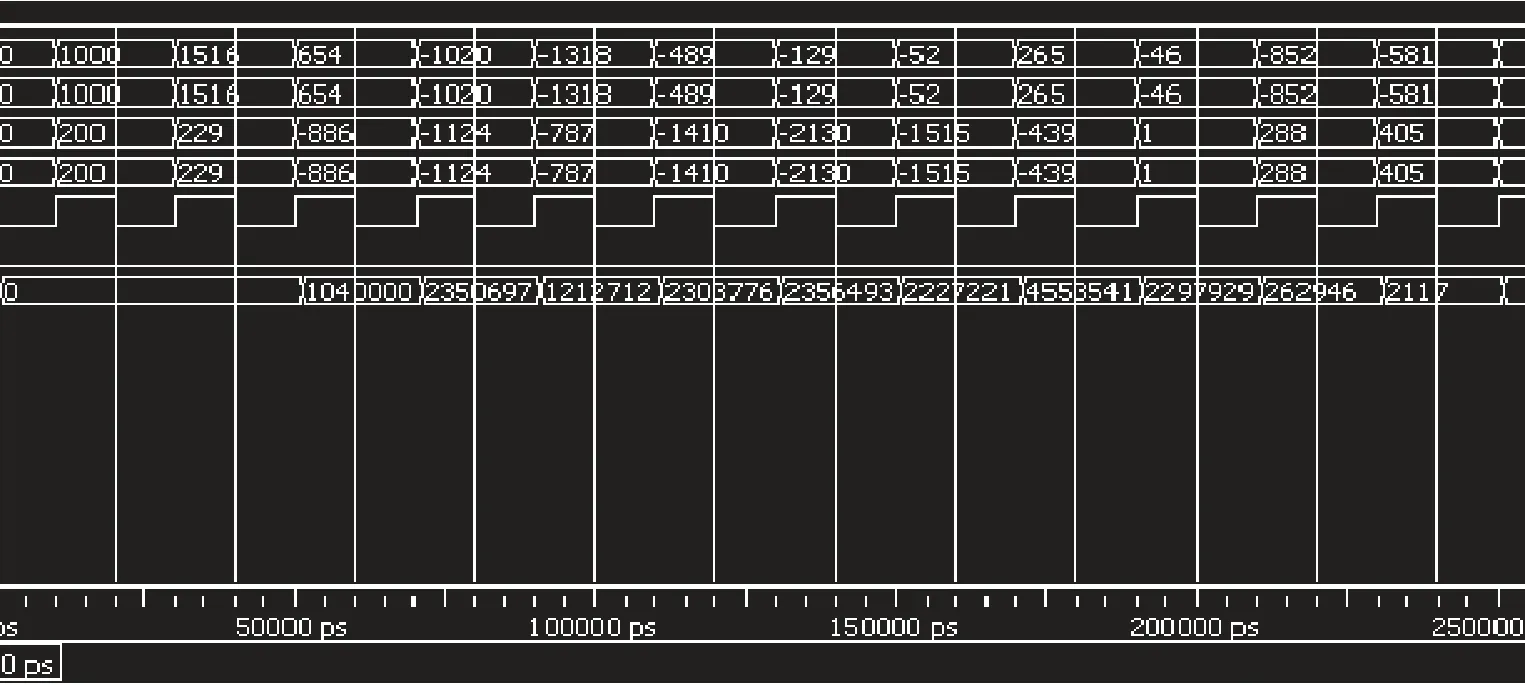

图11到图19表示经过优化因子处理模块的数据进入降峰均比模块处理的整个过程。

图10 降峰均比模块中的主要子模块

图11 第一组虚部乘-1和第二组虚部乘-1后的32位加法模块

图12 第一组实部乘-1和第二组实部乘-1后的32位加法模块

图13 第一组乘-1和第二组乘-1后的平方加和模块

图14 第一组乘-1和第二组乘1后的平方加和模块

图15 第一组乘1和第二组乘-1后的平方加和模块

图16 第一组乘1和第二组乘1后的平方加和模块

图17 第一组乘1和第二组乘-1后的平方加和处理后的最大值模块

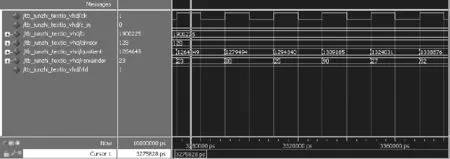

图18 第一组乘1和第二组乘-1后的均值模块

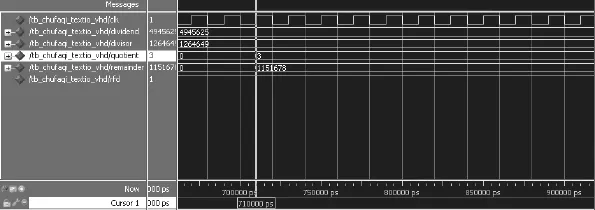

图19 除法模块

图11到图16是加法模块和平方加和模块处理结果。从图中得出,第一组和第二组的最优化因子分别为1和-1。图17、图18和图19分别表示最大值模块、均值模块、除法模块的结果。从图19可以得出:OFDM符号的峰均比值为3 dB。

通过门限值比较模块(其中门限值设为8 dB)可知,此符号的峰均比值(3 dB)小于门限值,故其可通过进入前导模块,同时返回一个信号值0,让门限值比较模块下一个符号进入倍增模块,进行另一个OFDM符号的倍增组值算法。

2 结 语

本文是在ISE9.2平台下实现倍增组值算法。整个硬件共分成5个模块,其中最重要的是降峰均比模块,IFFT点数为64点,硬件采用Xilinx公司的ISE系列FPGA芯片。

综上所述,该算法降峰均比效果较好,而且硬件实现简单,资源占用较少,是一种较为实用的算法,具有一定的实际应用价值。

[1] 王文博,郑侃.宽带无线通信OFDM技术[M].2版.北京:人民邮电出版社,2007. WANG Wen-bo,ZHENG Kan.OFDM Broadband Wireless Communication Technology[M].Second Edition. Beijing:People's Posts and Telecommunications Press, 2007.

[2] 何维武,冯辉,谭淇文等.基于部分传输序列技术降OFDM系统PAPR的改进算法[J].广东通信技术,2016,36(02):34-36,70. HE Wei-wu,FENG Hui,TAN Qi-wen,et al.Improved Algorithm of PAPR based on Partial Transmission Sequence Technique for OFDM System[J].Guangdong Communication Technology,2016,36(02):34-36,70.

[3] Heung-Gyoon Ryu,Kyoung-Jae Youn.A New PAPR Reduction Scheme:SPW(Subblock phase weighting) [J]. IEEE Transactions on Consumer Electronics, 2002,48(01):81-89.

[4] 赵成龙.OFDM系统中选择性映射降低峰均比的研究[D].南京:南京邮电大学,2012. ZHAO Cheng-long.Research on Selected Mapping System to Reduce PAPR in OFDM System[D].Nanjing: Nanjing University of Posts and Telecommunications,2012.

[5] 袁建党.预留载波法降低OFDM峰均比的研究和FPGA实现[D].西安:西安电子科技大学,2011. YUAN Jian-dang.Reserved Carrier Method to Reduce PAPR in OFDM Research and Implementation of FPGA [D].Xi'an: Xi'an Electronic and Science University,2011.

[6] 崔献文.OFDM系统同步及解调的FPGA实现[D].成都:电子科技大学,2009. CUI Xian-wen.OFDM System Synchronization and Demodulation FPGA Implementation[D].Chengdu: University of Electronic Science and Technology,2009.

何维武(1976—),男,硕士,工程师,主要研究方向为宽带无线通信技术;

谭淇文(1979—),男,学士,工程师,主要研究方向为通信技术;

曾康娟(1983—),女,硕士,工程师,主要研究方向为软件系统工程设计与应用。

FPGA Realization of Multiplication Group Value Algorithm for PAPR Reduction

HE Wei-wu, TAN Qi-wen, ZENG Kang-juan

(Chongqing Jinmei Communication Co.,Ltd., Chongqing 400030,China)

In the previous PAPR system OFDM research, the multiplication group value algorithm is presented, and a lot of theoretical analysis is done. Meanwhile, the MATLAB simulation software is used to verify the feasibility of the algorithm. Based on this, further research on how to use FPGA to achieve the multiplication group value algorithm to suppress the peak to average ratio of OFDM system is done, and the idea of realizing the peak to average ratio suppression module design and its verification in FPGA is proposed . The verification results indicated that the proposed realization PAPR suppression module in FPGA design is simple, with less hardware resource and fairly good suppressing PAPR.

OFDM;Multiplication group value algorithm;Threshold;Mean module;PAPR reduction module

TN929.53

A

1002-0802(2016)-07-0929-08

10.3969/j.issn.1002-0802.2016.07.025

2016-03-15;

2016-06-09 Received date:2016-03-15;Revised date:2016-06-09