基于FPGA的PROFIBUS-DP从站实现

2016-09-13宋连庆梁鹏飞王纪臣

宋连庆,梁鹏飞,王纪臣

(西安工程大学 陕西 西安 710048)

基于FPGA的PROFIBUS-DP从站实现

宋连庆,梁鹏飞,王纪臣

(西安工程大学 陕西 西安710048)

以FPGA为主控芯片,采用Verilog硬件描述语言实现协议内容,从而代替SPC3协议芯片,实现从站各个通信模块控制器的逻辑功能,构成一个完整的PROFIBUS-DP从站,并且给出了物理层(PHY)的详细设计过程。该技术的使用将不再受外国供货商的限制,并且降低PROFIBUS-DP总线系统的成本,具有一定的实际应用价值。

PROFIBUS-DP;FPGA;从站;物理层

PROFIBUS是面向工厂自动化、流程自动化的一种国际性现场总线标准。在2000年成为IEC61158中的现场总线国际标准之一,于2001年正式成为我国机械行业工业控制系统的现场总线国家标准。由于PROFIBUS协议比较复杂,而国内的专用芯片基本上都是由国外厂商提供,致使我国自动化行业难以掌握该科技核心技术[1]。目前实现PROFIBUS-DP从站的方法有基本有3种,分别为使用单片机、使用专用的ASIC通信芯片和使用接口模板实现3种,但主流设计方案还是依靠专用的ASIC专用通信芯片。与此同时,由于电子行业的飞速发展,各种微处理器的广泛使用,使得现场可编程门阵列(FPGA)得到有力的发展,其TOP_DOWN的设计理念,可以将系统功能逐层分割,通过各个模块的实现设计思想,最终组合成一个完整的系统,成功避开对具体器件结构的考虑,这也是本此设计用FPGA的重要原因之一[2-4]。

图1 PROFIBUS-DP协议结构Fig.1 Agreement structure of PROFIBUS-DP

1 PROFIBUS-DP协议分析

PROFIBUS的协议参考了ISO/OSI模型,并对其进行了简化。PROFIBUS-DP只采用第一层(物理层)、第二层(数据链路层)和用户接口层,第3到7层未使用,这种精简的结构确保了高速数据传输。其协议的机构如图1所示。

PROFIBUS的FDL层报文帧传输结构仅有4种,分别为:

SD1:无数据,只用作查询总线上的激活站点;

SD2:数据域长度可变,参数域的配置多且功能强大,常

用于SRD服务;

SD3:带有固定长度(8字节)的数据域;

SD4:Token令牌帧;

SC:短应答帧。

以上的帧字符均采用UART传输格式,每个字符由一位起始位,八位数据位,一位奇偶校验位和一位停止位组成。

总线协议规定PROFIBUS FDL层负责向上层用户提供数据传输服务,这种传输服务构成FDL层的基本功能,分别为:发送数据不需要确认(SDN),发送数据需要确认(SDA),发送数据且要求回复数据(SRD),周期性发送且要求回复数据 (周期性交换数据)(CSRD)。在PROFIBUS-DP总线设计中,只使用了SDN和SRD为基本的两种数据传输模式。同时,FMA1/2还要负责对参数的管理和设定,提供一系列的功能,如事件、设定值、复位、读值等。为了保证帧的正确传输,FDL对帧的相应时序做了严格地规定[5]。

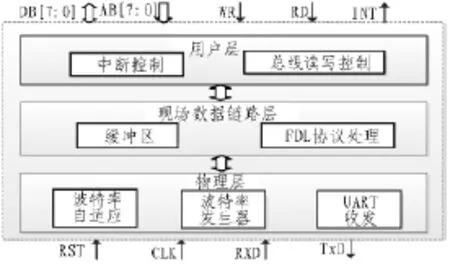

2 从站通信控制芯片的设计

基于FPGA的PROFIBUS-DP从站通信控制器,是为了在加入总线后,能够作为一个从站节点进行正常的总线通信。通过整体分析,确定如下功能:完成物理层的数据传输,将接收或发送的数据通过缓冲区打包,与FDL协议进行报文格式检查,然后像上层传输服务。采用FPGA自上而下(TOPDOWN)的设计思路,先确定总体设计框架,然后分别实现各个模块,其芯片结构图2所示。

图2 从站通信芯片模块图Fig.2 Communication chip of slave

2.1物理层模块

物理层模块包括波特率自适应模块,波特率产生模块,UART收发模块。主要功能是能正确接收来自PROFIBUS-DP总线的发来的比特数流,完成与FDL数据帧之间的转换,然后将生成的报文以串行方式发送到总线上去。此外,在接收总线上的串行数据时通过波特率自适应模块来确定波特率,使得与总线波特率一致,进行正确的数据交换[6]。

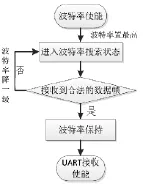

2.1.1波特率自适应模块

PROFIBUS-DP支持9.6 Kpbs~1.2 Mbps之间的10种通信波特率[7]。由于在同一网络上所选的传输波特率必须一致,为了避免认为设置波特率错误而导致通信故障,接口设置波特率自动搜索模块,将芯片的波特率自动调整到与总线数据通信的波特率一致[8]。在具体设计过程中,将波特率发生模块和波特率自适应模块设计在一起。波特率自适应流程图如3所示。

图3 波特率自适应流程图Fig.3 Auto-turn of baud

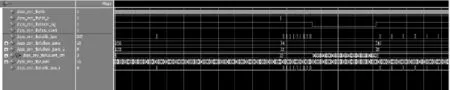

根据UART数据传输格式,当检测到有大于33bit的空闲位由高电平变为低电平时[9],接收模块产生波特率发生使能信号(bps-start),同时波特率发生模块将波特率置为最高12M。如果接收到的数据帧最后一位字符为0x16,则认为接收到合法的数据帧,产生done-sig信号,波特率保持 (clkbps),UART接收模块则以此波特率接收主站信号;若不是,则波特率降一级,直至接收到合法的数据帧。如果主站波特率发生改变,则复位从站,从站重新搜索波特率。在实际设计过程中将最高波特率 12 Mbps设置成4’d0,最低波特率9600bps设置成4’d9,总共十级,符合总线要求。仿真时序图给出了第5级,第0级以及第2级的波特率自适应过程,其仿真图如4所示。

图4 波特率自适应仿真图Fig.4 Simulation of auto-turn baud

2.1.2UART接收模块

UART收发模块包括UART接收模块和UART发送模块两部分。

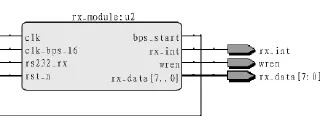

本次设计数据传输采用RS-232串口通信,主要功能是时刻监测总线上的电平情况,当有数据发送来时,按照波特率产生模块发送的波特率时钟接收总线上的串行数据,通过接收缓冲区,实现数据的串并转换[10],其接收模块接口图如图5所示。

图5 RS-232接收模块接口图Fig.5 RS-232 receive

根据PROFIBUS总线要求,为确保数据接收的正确性,采用波特率时钟的 16倍进行数据采集(clk_bps_16),即9600*16bps。rs232_rx为数据输入接口,用来接收总线上的串行数据,rx-inT为数据中断信号,接收到数据期间始终为高电平,wren为ram写信号,当wren置高,进入写状态。在数据采集过程,为得到精确的采集信号,采集点选为每个采集时钟的第8位为接收数据。接收模块部分程序为:

2.1.3UART发送模块

UART发送过程与接收过程基本相似:从站接收到的数据根据数据链路层的分析,产生相应的报文,以当前的波特率发送给主站,完成一个报文发送。在发送时,不需要像接收时大于33 bit的空闲位

2.2现场数据链路层模块

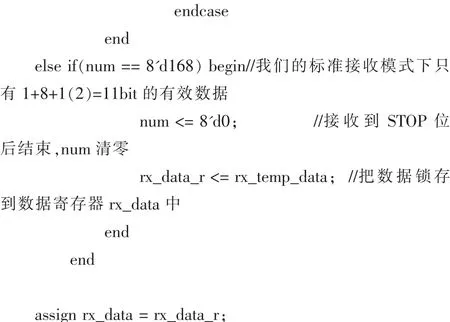

现场数据链路层的主要功能是将FDL层的数据映射到DDLM服务,并将用户设置或输入数据进行打包发送到FDL层准备发送。协议处理是从站通信芯片的核心,流程图如6所示。

图6 FDL协议处理流程图Fig.6 Flow chart of FDL

FDL协议处理模块是对物理层接收到的报文进行帧格式检查。首先,实时监测UART收发器状态,当接收到帧数据字节,对接收到的数据进行帧起始符判断,满足起始符要求,则报文帧接收完毕;若不符合报文帧起始符,丢弃错误的报文帧,复位状态机。将接收到的帧数据单元存入缓冲区;其他帧字符,则提取相关的FDL信息,是否存在地址扩展、使用的SAP(Service Access Point,服务节点)等,把不同功能的数据分配到对应的缓冲区进行处理。同时,该模块还实现控制校验和计算功能,将最终校验与接收到的FCS进行比较,不一致,则认为接收到的帧数据错误,丢弃该错误的报文帧,状态机复位。随后解析FC(功能码),以确定SDN或SRD数据传输服务和对FDL状态的查询。

3 系统仿真与验证

本设计采用Verilog硬件描述语言(HDL)进行编程,使用Modelsim SE 10.0C软件进行时序仿真和功能仿真,系统能够实现协议功能。为了进一步验证设计的正确性,在以下环境进行了验证: 以 Altera公司设计研发的 CycloneⅣEP4CE617C8的开发板为平台,将设计的程序固化到FPGA芯片中,外搭RS-232串行通信接口,实现了最简PROFIBUS-DP从站。测试过程中,以笔记本的USB端口和PROFIBUS-DP之间接入通信管理机(ProfiCore),在笔记本上运行ProfiScript,按照协议设置相应的参数。测试结果表明,从站基本完成了协议功能。

4 结 论

本文提出了一种以FPGA器件为核心,利用其自顶向下的设计理念,采用Verilog硬件描述语言来实现PROFIBUSDP从站协议内容的新型设计方法。在设计工程中,没有拘泥于繁琐的通用协议,只是对最为广泛的两种请求帧进行设计,节省了FPGA资源。对功能模块进行了仿真,并给出部分功能的仿真波形,进行了逻辑功能的验证。该设计需要进一步的升级和完善,促进工业总线发展,在工程中有广泛的应用价值。

[1]侯维岩,费敏锐.PROFIBUS协议分析和系统应用[M].北京:清华大学出版社,2006.

[2]夏宇闻.Verilog数字系统设计教程[M].北京:北京航空航天大学出版社,2008.

[3]吴厚航.深入浅出玩转FPGA[M].北京:北京航空航天大学出版社,2008.

[4]王诚,吴继华.Altera FPGA/CPLD设计[M].北京:人民邮电出版社,2005.

[5]俞跃.基于FPGA的PROFIBUS-DP从站通信控制芯片的设计[D].辽宁:东北大学,2009.

[6]田红霞,戴彦,鹿红玉.基于FPGA的RS232串行接口设计[J].煤炭技术,2010,29(9):194-196.

[7]朱博,夏继强.基于FPGA的PROFIBUS-DP从站链路层控制器IP核的设计[J].微电子学与计算机,2007,24(1):102-105.

[8]蔡远斌.基于FPGA的PROFIBUS-DP从站研究与实现[D].吉林:吉林大学,2012.

[9]石晓亮.基于FPGA的PROFIBUS-DP从站设计[D].浙江:浙江大学,2008.

[10]徐祥,蒋哲,王威廉.基于FPGA的高速数据采集、缓存与处理系统[J].电子测量技术,2013,36(4):68-71.

The design of PROFIBUS-DP slave station based on FPGA

SONG Lian-qing,LIANG Peng-fei,WANG Ji-chen

(Xi’an Polytechnic University,Xi’an 710048,China)

This design is based on FPGA,using Verilog HDL to achieve the agreement,replacing the SPC3 protocol chip,realized the each communication module controller logical function of slave station,making up a PROFIBUS-DP slave station,and gived the Physical Layer(PHY)for the detailed design process.Using this technology will no logger be limited by foreign suppliers and reduce the cost of PROFIBUS-DP,has some practical significance.

PROFIBUS-DP;FPGA;slave;PHY

TN871

A

1674-6236(2016)03-0069-03

2015-03-31稿件编号:201503466

宋连庆(1963—),男,河南新乡人,副教授。研究方向:现代电力电子变换与传动,工业设备自动化控制。